標題: 數電基于FPGA的數字時鐘的設計及仿真結果分析 [打印本頁]

作者: 1038623568 時間: 2019-1-10 13:58

標題: 數電基于FPGA的數字時鐘的設計及仿真結果分析

目錄

一、 設計任務與要求 3

二、設計思路 4

1.1設計方案 4

1.2設計要點 4

1.3工作原理 4

三、程序運行及結果 5

(1)分頻模塊 5

(2)秒模塊 6

(3)分模塊(minute) 8

(4)時模塊(hour) 10

(5)數碼顯示驅動模塊 12

(6)片選模塊(sell) 13

(7)譯碼顯示模塊(display) 14

(8)報時模塊(alart) 15

(9)六進制計數器模塊(cnt6) 16

(10)兩輸入與模塊(and2a) 17

(11)兩輸入或模塊(or2a) 18

四、頂層電路設計及仿真結果與分析 19

五、心得體會 22

六、參考文獻 23

七、 源程序 23

摘要:近年來隨著數字技術的迅速發展,各種中、大規模集成電路在數字系統、控制系統、信號處理等方面都得到了廣泛的應用。這就迫切要求理工科大學生熟悉和掌握常用中、大規模集成電路功能及其在實際中的應用方法,除通過實驗教學培養數字電路的基本實驗方法、分析問題和故障檢查方法以及雙蹤示波器等常用儀器使用方法等基本電路的基本實驗技能外,還必須培養大學生工程設計和組織實驗能力。

本次設計的目的在于培養學生對基本電路的應用和掌握,使學生在實驗原理的指導下,初步具備基本電路的分析和設計能力,并掌握其應用方法;自行擬定實驗步驟,檢查和排除故障 、分析和處理實驗結果及撰寫實驗報告的能力。綜合實驗的設計目的是培養學生初步掌握小型數字系統的設計能力,包括選擇設計方案,進行電路設計、安裝、調試等環節,運用所學知識進行工程設計、提高實驗技能的實踐。數字電子鐘是一種計時裝置,它具有時、分、秒計時功能和顯示時間功能;具有整點報時功能。

本次設計我查閱了大量的文獻資料,學到了很多關于數字電路方面的知識,并且更加鞏固和掌握了課堂上所學的課本知識,使自己對數字電子技術有了更進一步的認識和了解。

基本功能:能進行正常的時、分、秒計時功能,分別由6個數碼管顯示24小時,60分鐘,60秒鐘的計數器顯示。

附加功能:1)能利用硬件部分按鍵實現“校時”“校分”“清零”功能;

2)能利用蜂鳴器做整點報時:當計時到達59’59’’時開始報時,鳴叫時間1秒鐘;

3)定時鬧鈴:本設計中設置的是在七點時進行鬧鐘功能,鳴叫過程中,能夠進行中斷鬧鈴工作。

二、設計思路

1.1設計方案

1、時鐘功能,具有顯示時、分、秒的功能;

2、具有整點報時功能,在整點時使用蜂鳴器進行報時,具有鬧鐘功能,鳴叫過程中,具有中斷鬧鈴功能。

1.2設計要點

數字鐘一般是由振蕩器、分頻器、計數器、譯碼器、顯示器等幾部分組成。這些都是數字電路中應用最廣泛的基本電路,本設計分模塊設計實現各部分功能,采用軟件編程控制FPGA芯片內部產生振動周期為1s的脈沖。并將信號送入計數器進行計算,并把累加的結果以“時”、“分”、“秒”的數字顯示出來。“秒”的顯示由兩級計數器和譯碼器組成的六十進制計數電路實現;“分”的顯示電路“秒”相同,“時”的顯示由兩級計數器和譯碼器組成的二十四進制電路來實現。所有計時結果由六位數碼管顯示。

1.3工作原理

數字電子鐘由振蕩器、分頻器 計數器、譯碼顯示、報時等電路組成。振蕩器產生穩定的高頻脈沖信號,作為數字鐘的時間基準,然后經過分頻器輸出標準秒脈沖。秒計數器滿60后向分計數器進位,分計數器滿60后向小時計數器進位,小時計數器按照“24翻1”規律計數。計滿后各計數器清零,重新計數。計數器的輸出分別經譯碼器送數碼管顯示,計時出現誤差時,可以用校時電路“校時”“校分”“清零”。秒脈沖可以通過分頻電路得到。通過報時設計模塊可以實現整點報時及定時鬧鈴,譯碼顯示由七段譯碼器完成,顯示由數碼管構成,采用的是動態顯示方式。數碼管動態顯示:動態掃描電路將計數器輸出的8421BGD碼轉換為數碼管需要的邏輯狀態,并且輸出數碼管的片選信號和為選信號。所謂動態掃描顯示方式是在顯示某一位LED 顯示塊的數據的時候,讓其它位不顯示,然后再顯示下一位的數據。只要保證每一位顯示的時間間隔不要太大,利用人眼的視覺暫留的現象,就可以造成各位數據同時顯示的假象。一般每一位的顯示時間為1~10ms。

三、程序運行及結果

(1)分頻模塊(fenpin)

1)程序:

library ieee;

use ieee.std_logic_1164.all;

entity fenpin is

port(clk6:in std_logic;

q1000,q5,q1:out std_logic);

end fenpin;

architecture ccc_arc of fenpin is

signal x:std_logic;

begin

process(clk6)

variable cnt:integer range 0 to 24999;

begin

if clk6'event and clk6='1' then

if cnt<24999 then

cnt:=cnt+1;

else

cnt:=0;

x<=not x;

end if;

end if;

end process;

q1000<=x;

process(x)

variable cnt2:integer range 0 to 999;

variable y:std_logic;

begin

if x'event and x='1' then

if cnt2<999 then

cnt2:=cnt2+1;

q1<='0';

else

cnt2:=0;

q1<='1';

end if;

end if;

if x'event and x='1' then

y:=not y;

end if;

q5<=y;

end process;

end ccc_arc;

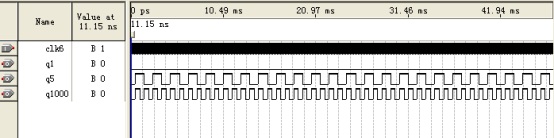

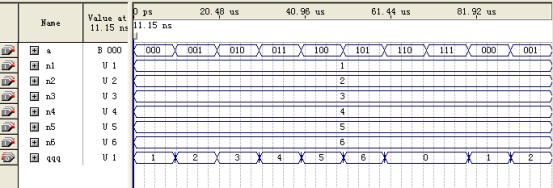

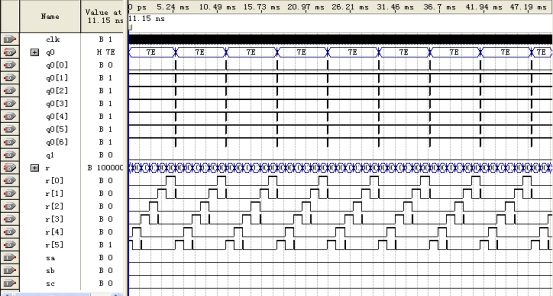

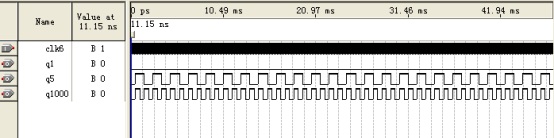

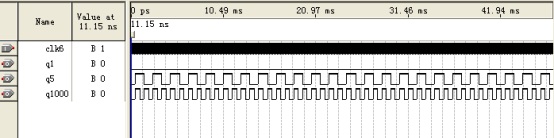

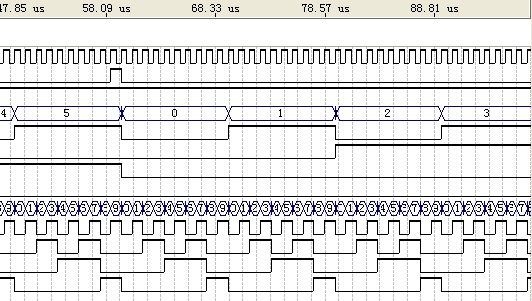

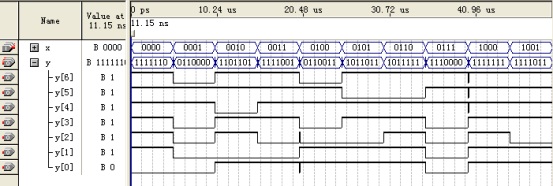

2)仿真波形:

- 仿真結果分析:產生用于計時,掃描輸入,掃描顯示,以及蜂鳴器所需的各個頻率的信號。

(2)秒模塊(second)

1)程序:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity second is

port (clk1,en1:in std_logic;

qa:out std_logic_vector(3 downto 0);

co1:out std_logic;

qb:out std_logic_vector(3 downto 0));

end second;

architecture cc of second is

signal cout2,cout1:std_logic_vector(3 downto 0);

signal mm: std_logic;

begin

process(clk1,en1)

begin

if en1='1' then

cout2<="0000";cout1<="0000";

elsif (clk1'event and clk1='1')then

if (cout2=5 and cout1=8) then cout2<=cout2;cout1<=cout1+1;mm<='1';

elsif (cout2=5 and cout1=9) then cout2<="0000";cout1<="0000";mm<='0';

else if (cout1=9) then cout2<=cout2+1;cout1<="0000";mm<='0';

else cout2<=cout2;cout1<=cout1+1;mm<='0';

end if;

end if;

end if;

end process;

co1<=mm;

qa<=cout2;

qb<=cout1;

end cc;

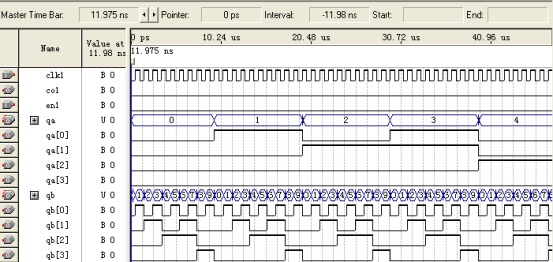

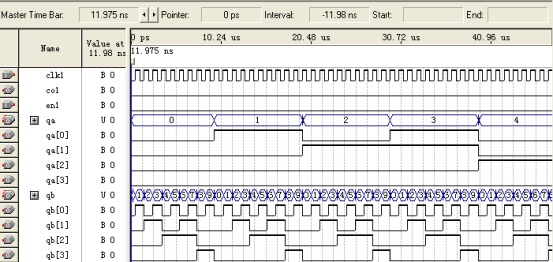

2)仿真波形:

- 仿真結果分析:該模塊實際是一個六十進制計數器,而六十秒為一分鐘,故用此模塊可以作為秒部分設計,通過觀察可知,仿真波形是正確可行的。

(3)分模塊(minute)

1)程序:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity minute is

port (clk2,en2:in std_logic;

qc:out std_logic_vector(3 downto 0);

co2:out std_logic;

qd:out std_logic_vector(3 downto 0));

end minute;

architecture bb of minute is

signal cout2,cout1:std_logic_vector(3 downto 0);

signal cc:std_logic;

begin

process(clk2,en2)

begin

if en2='1' then

if (clk2'event and clk2='1')then

if (cout2=5 and cout1=8) then cout2<=cout2;cout1<=cout1+1;cc<='1';

elsif (cout2=5 and cout1=9) then cout2<="0000";cout1<="0000";cc<='0';

else if (cout1=9) then cout2<=cout2+1;cout1<="0000";cc<='0';

else cout2<=cout2;cout1<=cout1+1;cc<='0';

end if;

end if;

end if;

end if;

end process;

co2<=cc;

qc<=cout2;

qd<=cout1;

end bb

2)仿真波形:

- 仿真結果分析:此模塊實際也是一個六十進制的計數器模塊,六十分鐘即為一個小時,用此模塊就成功解決了分設計模塊這個難題。從仿真波形可知,該設計時正確的。

(4)時模塊(hour)

1)程序:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity hour is

port (clk3,en3:in std_logic;

qe:out std_logic_vector(3 downto 0);

qf:out std_logic_vector(3 downto 0));

end hour;

architecture aa of hour is

signal cout2,cout1:std_logic_vector(3 downto 0);

begin

process(clk3,en3)

begin

if en3='1' then

if (clk3'event and clk3='1')then

if (cout2=2 and cout1=3) then cout2<="0000";cout1<="0000";

else if (cout1=9) then cout2<=cout2+1;cout1<="0000";

else cout2<=cout2;cout1<=cout1+1;

end if;

end if;

end if;

end if;

end process;

qe<=cout2;

qf<=cout1;

end aa;

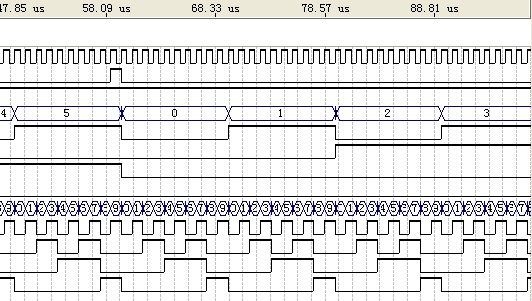

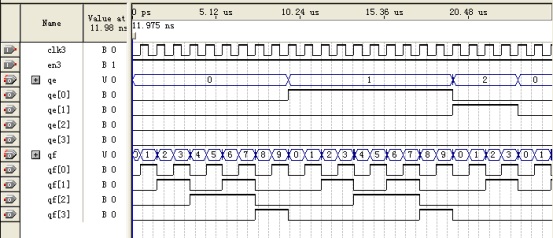

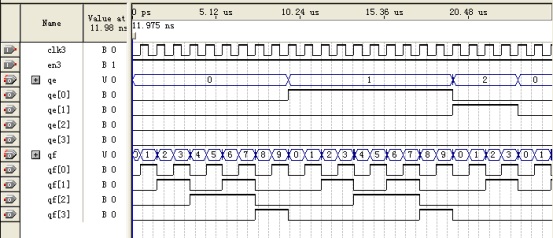

2)仿真波形:

- 仿真結果分析:這是一個24計數器,用來表示24小時,通過波形可知,程序設計正確,正常計時是每次清零后從00:00:00開始計時的,若要從預置時間開始,可以通過“校時”“校分”“清零”三個按鍵調整時間。

(5)數碼顯示驅動模塊

1)程序:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity hhh is

port(n1,n2,n3,n4,n5,n6:in std_logic_vector(3 downto 0);

a:in std_logic_vector(2 downto 0);

qqq:out std_logic_vector(3 downto 0));

end hhh;

architecture dd of hhh is

begin

with a select

qqq<=n1 when "000",

n2 when "001",

n3 when "010",

n4 when "011",

n5 when "100",

n6 when "101",

"0000" when others;

end dd;

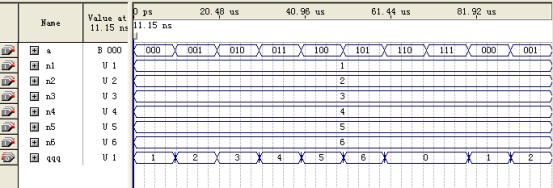

2)仿真波形:

- 仿真結果分析:其實這是一個選擇器,從波形圖可以很容易看出來。它是用來選擇需要顯示的數字,比如秒的十位,就會選擇n1到譯碼顯示器顯示出來,具備驅動數碼管的作用!

(6)片選模塊(sell)

1)程序:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity ggg is

port(m:in std_logic_vector(2 downto 0);

b:out std_logic_vector(5 downto 0));

end ggg;

architecture ee of ggg is

begin

with m select

b<="100000" when "000",

"010000" when "001",

"001000" when "010",

"000100" when "011",

"000010" when "100",

"000001" when "101",

"000000" when others;

end ee;

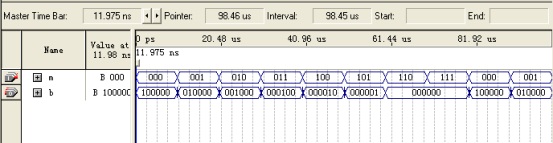

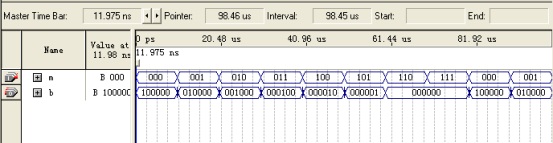

2)仿真波形:

- 仿真結果分析:設置時間時將所需的數據傳給顯示模塊,當設置鬧鈴時將數據傳給鬧鐘和顯示模塊。

(7)譯碼顯示模塊(display)

1)程序:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity decoder is

port(x:in std_logic_vector(3 downto 0);

y:out std_logic_vector(6 downto 0));

end decoder;

architecture one of decoder is

begin

with x select

y<="1111110" when "0000",

"0110000" when "0001",

"1101101" when "0010",

"1111001" when "0011",

"0110011" when "0100",

"1011011" when "0101",

"1011111" when "0110",

"1110000" when "0111",

"1111111" when "1000",

"1111011" when "1001",

"0000000" when others;

end one;

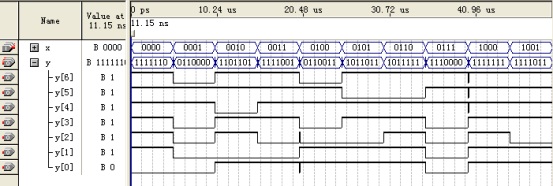

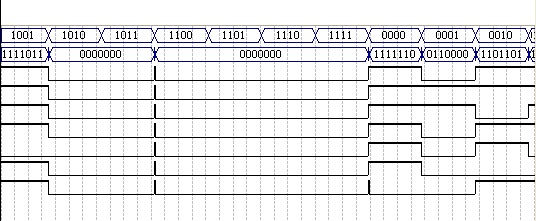

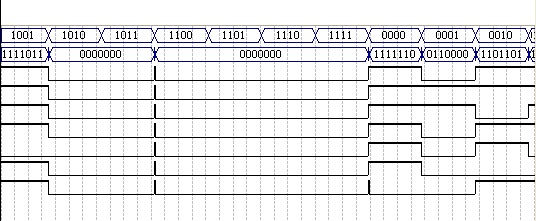

2)仿真波形:

- 仿真結果分析:此模塊是用來顯示時間的,采用動態顯示方式。

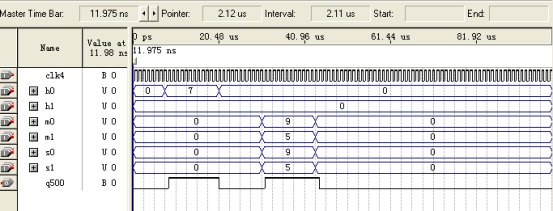

(8)報時模塊(alart)

1) 程序:

library ieee;

use ieee.std_logic_1164.all;

entity sst is

port(h1,h0,m1,m0,s1,s0:in std_logic_vector(3 downto 0);

clk4:in std_logic;

q500:out std_logic);

end sst;

architecture sss of sst is

begin

process(clk4,m1,m0,s1,s0)

begin

if (clk4'event and clk4='1') then

if ((h1="0000" and h0="0111" and m1="0000" and m0="0000")

or (m1="0101" and m0="1001" and s1="0101" and s0="1001"))then

q500<='1';

else

q500<='0';

end if;

end if;

end process;

end sss;

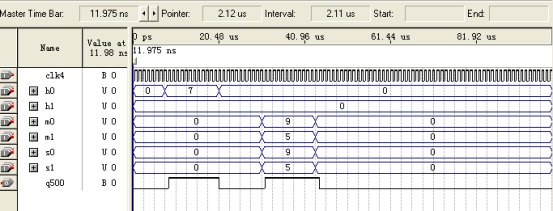

2) 仿真波形:

- 仿真結果分析:通過觀察波形可知,當時鐘時間與整點或鬧鈴預設時間相同時,給出一個脈沖信號,使蜂鳴器鳴叫,實現整點報時和定時鬧鈴功能。

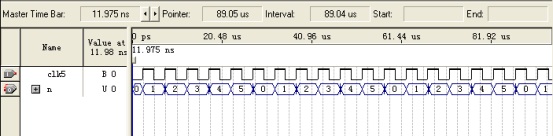

(9)六進制計數器模塊(cnt6)

1)程序:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity cnt6 is

port (clk5:in std_logic;

n:out std_logic_vector(2 downto 0));

end cnt6;

architecture behav of cnt6 is

signal q1:std_logic_vector(2 downto 0);

begin

process(clk5)

begin

if clk5'event and clk5='1' then

if q1<5 then q1<=q1+1;

else q1<=(others=>'0');

end if;

end if;

end process;

n<=q1;

end behav;

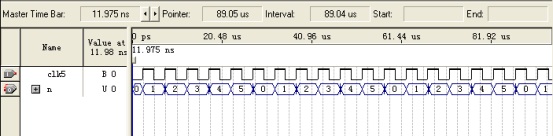

2)仿真波形:

- 仿真結果分析:很明顯可以看出這是一個簡單的六進制計數器。它與3-6譯碼器配合作用產生片選信號。

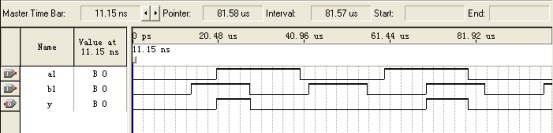

(10)兩輸入與模塊(and2a)

1)程序:

library ieee;

use ieee.std_logic_1164.all;

entity anda is

port (a1,b1:in std_logic;

y:out std_logic);

end anda;

architecture an of anda is

begin

y<=a1 and b1;

end an;

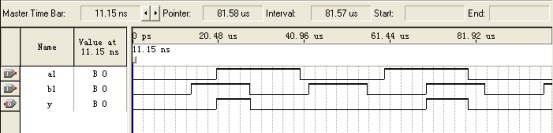

2)仿真波形:

3) 仿真結果分析:經觀察波形,程序正確。該與門的兩個輸入端分別為秒模塊和分模塊的進位輸出信號,當它們均為高電平時,時模塊使能端即為高電平,時模塊工作。

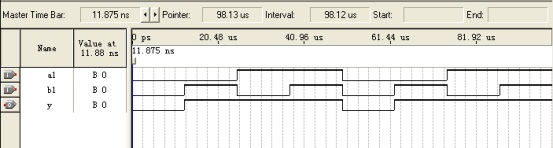

(11)兩輸入或模塊(or2a)

1)程序:

library ieee;

use ieee.std_logic_1164.all;

entity or_1 is

port (a1,b1:in std_logic;

y:out std_logic);

end or_1;

architecture oo of or_1 is

begin

y<=a1 or b1;

end oo;

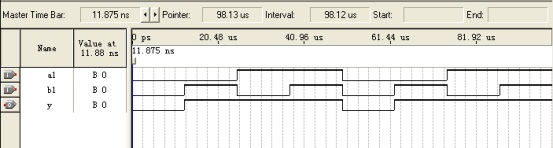

2)仿真波形:

3) 仿真結果分析:在整個數字鐘程序設計中,兩處用到兩輸入或門。一處是分模塊,或門兩輸入分別是秒模塊的進位輸出信號和外部校分信號,任一一個信號為高電平,分模塊使能端就為高電平,分模塊工作。另一處是在時模塊的使能端,它受分模塊進位輸出和外部校時信號輸入的控制,只要其一位高電平,時模塊都將工作。

四、頂層電路設計及仿真結果與分析

- library ieee;

- use ieee.std_logic_1164.all;

- entity digital_clock is

- port(clk,sa,sb,sc:in std_logic;

- q1:out std_logic;

- r:out std_logic_vector(5 downto 0);

- q0:out std_logic_vector(6 downto 0));

- end digital_clock;

- architecture main of digital_clock is

- component anda

- port(a1,b1:in std_logic;

- y:out std_logic);

- end component;

- component or_1

- port(a1,b1:in std_logic;

- y:out std_logic);

- end component;

- component fenpin

- port(clk6:in std_logic;

- q1000,q1,q5:out std_logic);

- end component;

- component hour

- port (clk3,en3:in std_logic;

- qe:out std_logic_vector(3 downto 0);

- qf:out std_logic_vector(3 downto 0));

- end component;

- component minute

- port (clk2,en2:in std_logic;

- qc:out std_logic_vector(3 downto 0);

- co2:out std_logic;

- qd:out std_logic_vector(3 downto 0));

- end component;

- component second

- port (clk1,en1:in std_logic;

- qa:out std_logic_vector(3 downto 0);

- co1:out std_logic;

- qb:out std_logic_vector(3 downto 0));

- end component;

- component sst is

- port(h1,h0,m1,m0,s1,s0:in std_logic_vector(3 downto 0);

- clk4:in std_logic;

- q500:out std_logic);

- end component;

- component hhh

- port(n1,n2,n3,n4,n5,n6:in std_logic_vector(3 downto 0);

- a:in std_logic_vector(2 downto 0);

- qqq:out std_logic_vector(3 downto 0));

- end component;

- component ggg

- port(m:in std_logic_vector(2 downto 0);

- b:out std_logic_vector(5 downto 0));

- end component;

- component cnt6 is

- port (clk5:in std_logic;

- n:out std_logic_vector(2 downto 0));

- end component;

- component decoder

- port(x:in std_logic_vector(3 downto 0);

- y:out std_logic_vector(6 downto 0));

- end component;

- signal a,b,c,h, i,j,z:std_logic;

- signal k,l,e,f,u,v,t:std_logic_vector(3 downto 0);

- signal s: std_logic_vector(2 downto 0);

- begin

- u1:fenpin port map(clk6=>clk,q1=>h,q1000=>z);

- u2:second port map(clk1=>h,en1=>sc,qa=>k,qb=>l,co1=>I);

- u0:or_1 port map(a1=>i,b1=>sb,y=>a);

- u3:minute port map(clk2=>h,en2=>a,qc=>e,qd=>f,co2=>j);

- u30:anda port map(a1=>i,b1=>j,y=>b);

- u31:or_1 port map(a1=>b,b1=>sa,y=>c);

- u4:hour port map(clk3=>h,en3=>c,qe=>u,qf=>v);

- u5:sst port map(h1=>u,h0=>v,m1=>e,m0=>f,s1=>k,s0=>l,clk4=>h,q500=>q1);

- u6:hhh port map(n1=>k,n2=>l,n3=>e,n4=>f,n5=>u,n6=>v,qqq=>t,a=>s);

- u7:ggg port map(b=>r,m=>s);

- u8:cnt6 port map(n=>s,clk5=>z);

- u9:decoder port map(x=>t,y=>q0);

- end architecture main;

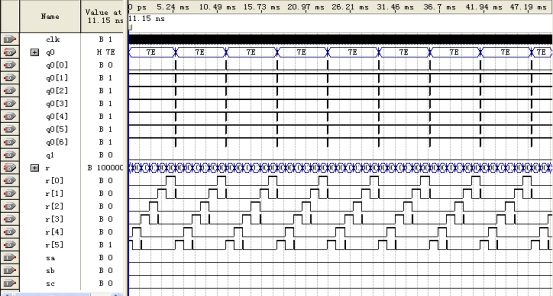

3)仿真結果分析:本次試驗給出的頻率是50MHZ,用QUARTUS-2軟件把數字鐘的全部工作過程記錄下來不容易,故這幅圖只是其工作的一小部分。將程序下載到FPGA芯片中,并與硬件部分對應連接好,可以驗證到我們所預期的所有功能,故可知該頂層文件是正確的,每一個模塊的功能也都是正確的,模塊之間的連接也都是正確的。

在軟件調試仿真過程中,我們以參考資料上的程序為模板,依據個人的需要添加修改各個功能模塊,盡管有模板作為參考,仿真過程中還是出了很多的問題,例如在做數碼管動態顯示中,我們采用了NPN型9013晶體三極管作為數碼管的接地驅動,這里的片選信號應該是高電平有效,我們原程序是低電平,經過多次的和其他組的學習交流中,找到了這個錯誤。解決分頻問題中,我們也在分頻模塊中做了修改,得到我們所需要的頻率。

五、心得體會

經過這次的數字電路課程設計,我個人得到了不少的收獲,一方面加深了我對課本理論的認識,另一方面也提高了實驗操作能力。現在我總結了以下的體會和經驗。

這次的課程設計跟我們以前做的不同,因為我覺得這次我是真真正正的自己親自去完成。所以是我覺得這次實驗最寶貴,最深刻的。就是設計的過程全是我們學生自己動手來完成的,這樣,我們就必須要弄懂一個電路的原理。在這里我深深體會到哲學上理論對實踐的指導作用:弄懂實驗原理,而且體會到了實驗的操作能力是靠自己親自動手,親自開動腦筋,親自去請教別人才能得到提高的。

我們做實驗絕對不能人云亦云,要有自己的看法,這樣我們就要有充分的準備,若是做了也不知道是個什么實驗,那么做了也是白做。實驗總是與課本知識相關的,有了課本的知識,我們才能編寫出自己需要的程序,實現自己預期的功能。

我們做實驗不要一成不變和墨守成規,應該有改良創新的精神。實際上,在弄懂了實驗原理的基礎上,我們的時間是充分的,做實驗應該是游刃有余的,如果說創新對于我們來說是件難事,那改良總是有可能的。數字時鐘大體看上去很簡單,但其中的可變的地方還是有很多的,譬如說整點報時功能,報時持續的時間長短就是一個可變的地方。

在實驗的過程中我們要培養自己的獨立分析問題,和解決問題的能力。在編程過程中,我們也遇到了很多的問題,就之前提到的動態掃描驅動問題,如果一味的去遵循資料上的程序的話,那整個設計將會失敗,只有不斷的學習研究,才能解決問題。

這次的課程設計,我的收獲很多,就我本身來說,不但對理論知識有了更加深的理解,對于實際的操作和也有了質的飛躍。經過這次的實驗,我們整體對各個方面都得到了不少的提高,團隊的合作意識也增強了很多。

六、參考資料:

付家才 .《 EDA工程實踐技術 》.化學工業出版社.2004年12月

陳忠平 .《 基于Quartus II的FPGA/CPLD設計與實踐 》.北京電子工業出版社.2010年4月

- library ieee;

- use ieee.std_logic_1164.all;

- entity fenpin is

- port(clk6:in std_logic;

- q1000,q5,q1:out std_logic);

- end fenpin;

- architecture ccc_arc of fenpin is

- signal x:std_logic;

- begin

- process(clk6)

- variable cnt:integer range 0 to 24999;

- begin

- if clk6'event and clk6='1' then

- if cnt<24999 then

- cnt:=cnt+1;

- else

- cnt:=0;

- x<=not x;

- end if;

- end if;

- end process;

- q1000<=x;

- process(x)

- variable cnt2:integer range 0 to 999;

- variable y:std_logic;

- begin

- if x'event and x='1' then

- if cnt2<999 then

- cnt2:=cnt2+1;

- q1<='0';

- else

- cnt2:=0;

- q1<='1';

- end if;

- end if;

- if x'event and x='1' then

- y:=not y;

- end if;

- q5<=y;

- end process;

- end ccc_arc;

- library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_unsigned.all;

- entity second is

- port (clk1,en1:in std_logic;

- qa:out std_logic_vector(3 downto 0);

- co1:out std_logic;

- qb:out std_logic_vector(3 downto 0));

- end second;

- architecture cc of second is

- signal cout2,cout1:std_logic_vector(3 downto 0);

- signal mm: std_logic;

- begin

- process(clk1,en1)

- begin

- if en1='1' then

- cout2<="0000";cout1<="0000";

- elsif (clk1'event and clk1='1')then

- if (cout2=5 and cout1=8) then cout2<=cout2;cout1<=cout1+1;mm<='1';

- elsif (cout2=5 and cout1=9) then cout2<="0000";cout1<="0000";mm<='0';

- else if (cout1=9) then cout2<=cout2+1;cout1<="0000";mm<='0';

- else cout2<=cout2;cout1<=cout1+1;mm<='0';

- end if;

- end if;

- end if;

- end process;

- co1<=mm;

- qa<=cout2;

- qb<=cout1;

- end cc;

- library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_unsigned.all;

- entity minute is

- port (clk2,en2:in std_logic;

- qc:out std_logic_vector(3 downto 0);

- co2:out std_logic;

- qd:out std_logic_vector(3 downto 0));

- end minute;

- architecture bb of minute is

- signal cout2,cout1:std_logic_vector(3 downto 0);

- signal cc:std_logic;

- begin

- process(clk2,en2)

- begin

- if en2='1' then

- if (clk2'event and clk2='1')then

- if (cout2=5 and cout1=8) then cout2<=cout2;cout1<=cout1+1;cc<='1';

- elsif (cout2=5 and cout1=9) then cout2<="0000";cout1<="0000";cc<='0';

- else if (cout1=9) then cout2<=cout2+1;cout1<="0000";cc<='0';

- else cout2<=cout2;cout1<=cout1+1;cc<='0';

- end if;

- end if;

- end if;

- end if;

- end process;

- co2<=cc;

- qc<=cout2;

- qd<=cout1;

- end bb

- library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_unsigned.all;

- entity hour is

- port (clk3,en3:in std_logic;

- qe:out std_logic_vector(3 downto 0);

- qf:out std_logic_vector(3 downto 0));

- end hour;

- architecture aa of hour is

- signal cout2,cout1:std_logic_vector(3 downto 0);

- begin

- process(clk3,en3)

- begin

- if en3='1' then

- if (clk3'event and clk3='1')then

- if (cout2=2 and cout1=3) then cout2<="0000";cout1<="0000";

- else if (cout1=9) then cout2<=cout2+1;cout1<="0000";

- else cout2<=cout2;cout1<=cout1+1;

- end if;

- end if;

- end if;

- end if;

- end process;

- qe<=cout2;

- qf<=cout1;

- end aa;

- library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_unsigned.all;

- entity hhh is

- port(n1,n2,n3,n4,n5,n6:in std_logic_vector(3 downto 0);

- a:in std_logic_vector(2 downto 0);

- qqq:out std_logic_vector(3 downto 0));

- end hhh;

- architecture dd of hhh is

- begin

- with a select

- qqq<=n1 when "000",

- n2 when "001",

- n3 when "010",

- n4 when "011",

- n5 when "100",

- n6 when "101",

- "0000" when others;

- end dd;

- library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_unsigned.all;

- entity ggg is

- port(m:in std_logic_vector(2 downto 0);

- b:out std_logic_vector(5 downto 0));

- end ggg;

- architecture ee of ggg is

- begin

- with m select

- b<="100000" when "000",

- "010000" when "001",

- "001000" when "010",

- "000100" when "011",

- "000010" when "100",

- "000001" when "101",

- "000000" when others;

- end ee;

- library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_unsigned.all;

- entity decoder is

- port(x:in std_logic_vector(3 downto 0);

- y:out std_logic_vector(6 downto 0));

- end decoder;

- architecture one of decoder is

- begin

- with x select

- y<="1111110" when "0000",

- "0110000" when "0001",

- "1101101" when "0010",

- "1111001" when "0011",

- "0110011" when "0100",

- "1011011" when "0101",

- "1011111" when "0110",

- "1110000" when "0111",

- "1111111" when "1000",

- "1111011" when "1001",

- "0000000" when others;

- end one;

- library ieee;

- use ieee.std_logic_1164.all;

- entity sst is

- port(h1,h0,m1,m0,s1,s0:in std_logic_vector(3 downto 0);

- clk4:in std_logic;

- q500:out std_logic);

- end sst;

- architecture sss of sst is

- begin

- process(clk4,m1,m0,s1,s0)

- begin

- if (clk4'event and clk4='1') then

- if ((h1="0000" and h0="0111" and m1="0000" and m0="0000")

- or (m1="0101" and m0="1001" and s1="0101" and s0="1001"))then

- q500<='1';

- else

- q500<='0';

- end if;

- end if;

- end process;

- end sss;

- library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_unsigned.all;

- entity cnt6 is

- port (clk5:in std_logic;

- n:out std_logic_vector(2 downto 0));

- end cnt6;

- architecture behav of cnt6 is

- signal q1:std_logic_vector(2 downto 0);

- begin

- process(clk5)

- begin

- if clk5'event and clk5='1' then

- if q1<5 then q1<=q1+1;

- else q1<=(others=>'0');

- end if;

- end if;

- end process;

- n<=q1;

- end behav;

- library ieee;

- use ieee.std_logic_1164.all;

- entity anda is

- port (a1,b1:in std_logic;

- y:out std_logic);

- end anda;

- architecture an of anda is

- begin

- y<=a1 and b1;

- end an;

- library ieee;

- use ieee.std_logic_1164.all;

- entity or_1 is

- port (a1,b1:in std_logic;

- y:out std_logic);

- end or_1;

- architecture oo of or_1 is

- begin

- y<=a1 or b1;

- end oo;

- library ieee;

- use ieee.std_logic_1164.all;

- entity digital_clock is

- port(clk,sa,sb,sc:in std_logic;

- q1:out std_logic;

- r:out std_logic_vector(5 downto 0);

- q0:out std_logic_vector(6 downto 0));

- end digital_clock;

- architecture main of digital_clock is

- component anda

- port(a1,b1:in std_logic;

- y:out std_logic);

- end component;

- component or_1

- port(a1,b1:in std_logic;

- y:out std_logic);

- end component;

- component fenpin

- port(clk6:in std_logic;

- q1000,q1,q5:out std_logic);

- end component;

- component hour

- port (clk3,en3:in std_logic;

- qe:out std_logic_vector(3 downto 0);

- qf:out std_logic_vector(3 downto 0));

- end component;

- component minute

- port (clk2,en2:in std_logic;

- qc:out std_logic_vector(3 downto 0);

- co2:out std_logic;

- qd:out std_logic_vector(3 downto 0));

- end component;

- component second

- port (clk1,en1:in std_logic;

- qa:out std_logic_vector(3 downto 0);

- co1:out std_logic;

- qb:out std_logic_vector(3 downto 0));

- end component;

- component sst is

- port(h1,h0,m1,m0,s1,s0:in std_logic_vector(3 downto 0);

- clk4:in std_logic;

- q500:out std_logic);

- end component;

- component hhh

- port(n1,n2,n3,n4,n5,n6:in std_logic_vector(3 downto 0);

- a:in std_logic_vector(2 downto 0);

- qqq:out std_logic_vector(3 downto 0));

- end component;

- component ggg

- port(m:in std_logic_vector(2 downto 0);

- b:out std_logic_vector(5 downto 0));

- end component;

- component cnt6 is

- port (clk5:in std_logic;

- n:out std_logic_vector(2 downto 0));

- end component;

- component decoder

- port(x:in std_logic_vector(3 downto 0);

- y:out std_logic_vector(6 downto 0));

- end component;

- signal a,b,c,h, i,j,z:std_logic;

- signal k,l,e,f,u,v,t:std_logic_vector(3 downto 0);

- signal s: std_logic_vector(2 downto 0);

- begin

- u1:fenpin port map(clk6=>clk,q1=>h,q1000=>z);

- u2:second port map(clk1=>h,en1=>sc,qa=>k,qb=>l,co1=>I);

- u0:or_1 port map(a1=>i,b1=>sb,y=>a);

- u3:minute port map(clk2=>h,en2=>a,qc=>e,qd=>f,co2=>j);

- u30:anda port map(a1=>i,b1=>j,y=>b);

- u31:or_1 port map(a1=>b,b1=>sa,y=>c);

- u4:hour port map(clk3=>h,en3=>c,qe=>u,qf=>v);

- u5:sst port map(h1=>u,h0=>v,m1=>e,m0=>f,s1=>k,s0=>l,clk4=>h,q500=>q1);

- u6:hhh port map(n1=>k,n2=>l,n3=>e,n4=>f,n5=>u,n6=>v,qqq=>t,a=>s);

- u7:ggg port map(b=>r,m=>s);

- u8:cnt6 port map(n=>s,clk5=>z);

- u9:decoder port map(x=>t,y=>q0);

- end architecture main;

以上的Word格式文檔51黑下載地址:

數電課程設計——基于fpga的數字時鐘的設計.doc

(364.62 KB, 下載次數: 81)

數電課程設計——基于fpga的數字時鐘的設計.doc

(364.62 KB, 下載次數: 81)

2019-1-10 13:57 上傳

點擊文件名下載附件

下載積分: 黑幣 -5

作者: jjjjsss歃 時間: 2020-5-30 11:44

分頻模塊仿真沒有輸出波型是怎么回事啊

作者: 小白單片機123 時間: 2021-6-7 14:29

分頻仿真出不來呀

| 歡迎光臨 (http://www.zg4o1577.cn/bbs/) |

Powered by Discuz! X3.1 |

主站蜘蛛池模板:

免费观看黄色片视频

|

国产综合久久久

|

久久亚洲一区二区三区四区

|

亚洲精品永久免费

|

欧美精品一区二区三区在线

|

亚洲一区二区精品视频在线观看

|

精品一区二区三区电影

|

国产精品一区二区在线

|

成人久草

|

日韩一区二区三区在线

|

国产激情|

精品videossex高潮汇编

|

亚洲精品第一

|

日韩在线中文

|

在线免费观看毛片

|

一区二区三区国产精品

|

美女天堂

|

欧美精品久久一区

|

午夜国产

|

国产一区二区三区四区五区加勒比

|

一区二区在线免费观看

|

免费观看的av毛片的网站

|

四虎影视|

精品久久久久久久久久久久久久久久久

|

夜操

|

中文字幕 在线观看

|

日韩三级电影一区二区

|

精品国产乱码久久久久久蜜臀

|

日韩黄

|

亚洲成人av在线播放

|

日韩在线播放第一页

|

国内精品视频一区二区三区

|

99国内精品久久久久久久

|

中文久久

|

www.日日夜夜

|

高清黄色毛片

|

久久综合九九

|

青春草国产

|

麻豆视频国产在线观看

|

国产高清视频一区二区

|

欧美aa在线

|

數電課程設計——基于fpga的數字時鐘的設計.doc

(364.62 KB, 下載次數: 81)

數電課程設計——基于fpga的數字時鐘的設計.doc

(364.62 KB, 下載次數: 81)