1 �wՓ

1.1 �n�}�о��ı���

�Ƽ��w�ٰl(f��)չ�r(sh��)�����գ������y(c��)���V����(y��ng)���ڹ��I(y��)���r(n��ng)�I(y��)����ͨ���h(hu��n)������ȫ���o(h��)��Դ�y(c��)���ȿƌW(xu��)�I(l��ng)�����y(c��)��Ĝy(c��)�����ȡ��y(c��)�����x���ɿ��Ե�����ָ��(bi��o)��(du��)��������P(gu��n)��(y��ng)��ϵ�y(t��ng)�Ĝy(c��)�ؾ��ȡ��ɿ��ԣ�������a(ch��n)Ч�ʡ����M(j��n)�ƌW(xu��)���g(sh��)�İl(f��)չ�����ИO����Ҫ�����á��S����(j��ng)��(j��)��Ѹ�ٰl(f��)չ����ͨϵ�y(t��ng)��������ͨ��ȫ��(w��n)�}Խ��(l��i)Խ����ҕ����ȫ���o(h��)�F(xi��n)��׃�ɞ�һ��(g��)��Ҫ�h�}�������꣬�����\(y��n)ݔ�¹��l�l(f��)����(f��)�s��ˮ�\(y��n)�h(hu��n)��������ꡢ���F��ҹ�g������(d��o)�º�������Ҋ(ji��n)�Ƚ��ͣ������ײ�¹ʡ����ڳ����y(c��)�༼�g(sh��)�����ںڰ����҉m�����F�Ȑ��ӵĭh(hu��n)�����������������ԣ��������y(c��)�����뺽�\(y��n)ϵ�y(t��ng)���Ќ�(sh��)���еľ����@һ��(w��n)�}��

�����y(c��)��ϵ�y(t��ng)���O(sh��)Ӌ(j��)�Y(ji��)��(g��u)��N���ӣ����ܲҲ������Ŀǰ�����������ij����y(c��)��ϵ�y(t��ng)�������8λ����16λ��Ƭ�C(j��)������оƬ���a(ch��n)���(q��)��(d��ng)��̖(h��o)����ؓ(f��)؟(z��)����̎���ز������ƬF(xi��n)��(sh��)ͨӍ���@��̎���ɱ���Ȼ�����ˣ����ǜy(c��)�����ȣ��͜y(c��)�����x���Լ��r(sh��)��Ŀ����������ޡ�

�����y(c��)��ĺ������ڳ�����̖(h��o)���հl(f��)���֣����y(t��ng)��Ƭ�C(j��)��(n��i)��ָ���\(y��n)�Еr(sh��)�����^���ӕr(sh��)�`���侫�ȟo(w��)���M�㾫�ܜy(c��)����Ҫ���O(sh��)Ӌ(j��)��FPGA(�F(xi��n)��(ch��ng)�ɾ����T���)���볬���y(c��)��ϵ�y(t��ng)���O(sh��)Ӌ(j��)��(n��i)���������^�ߵ��\(y��n)���ٶȺ��S����Ƭ��(n��i)�YԴ��ȡ����Ƭ�C(j��)����ߌ�(du��)���������l�ʵĿ��ƾ����Լ���(du��)�����հl(f��)��Խ�r(sh��)�g�Ĝy(c��)�����ȡ�

1.2��(gu��)��(n��i)����F(xi��n)��

�����y(c��)�౻������(y��ng)���ڸ��N���I(y��)�I(l��ng)���T�繤�I(y��)�Ԅ�(d��ng)���ƣ��������̜y(c��)���͙C(j��)����ҕ�X(ju��)�R(sh��)�e�ȷ��档������������ȣ����缤��y(c��)�ࡢ���y(c��)��ȣ��������ڿ՚��Ђ����ٶ��h(yu��n)�h(yu��n)С�ڹ⾀�͟o(w��)��늲��Ă����ٶȣ���(du��)�ڕr(sh��)�g��(c��)������ ��Ҫ���h(yu��n)С�ڼ���y(c��)�ࡢ���y(c��)���ϵ�y(t��ng)����������y(c��)��ϵ�y(t��ng)�·��(sh��)�F(xi��n)���Y(ji��)��(g��u)��(ji��n)�κ���r(ji��)�ͣ��ҳ����ڂ����^(gu��)���в��ܟ��F���՚���Ҋ(ji��n)�ȵ����ص�Ӱ푣��ڸ��N��(ch��ng)�Ͼ��õ��V����(y��ng)�á�

�����y(c��)������һ�N���͵ķǽ��|�y(c��)���������ںܶ���(ch��ng)�ϵ��ԑ�(y��ng)�á�Ȼ�������y(c��)���ڌ�(sh��)�H��(y��ng)��Ҳ�кܶ�����ԡ�

�����ڿ՚���˥�p�O�����ڜy(c��)�����x�IJ�ͬ����ɻز���̖(h��o)�����׃������ͬ���Ȼز���̖(h��o)��ͨ�^(gu��)�̶��T�ޱ��^���������^(gu��)���У��ز����_(d��)�r(sh��)�g�Ĝy(c��)t�a(ch��n)���^����`�������ǘ�(g��u)�ɳ����������ĉ���մ�Ƭ�ډ�늵��p���D(zhu��n)�Q�^(gu��)���У����ڑT�ԡ�����ȬF(xi��n)���Լ������}�_�ڿ՚��Ђ������������صķ���·��������(d��o)�»ز���̖(h��o)��չ����Ҳʹ�y(c��)���a(ch��n)���^����`�Ӱ��˜y(c��)��ķֱ��ʡ�����߀��һЩ���أ��T��h(hu��n)���ضȣ��L(f��ng)�ٵ�Ҳ��(hu��)��(du��)�y(c��)�����һ����Ӱ푡�

Ŀǰ��(gu��)��(n��i)�⌦(du��)�����y(c��)����о���Ҫ��������ߜy(c��)�ྫ�ȷ��档���ڳ����y(c��)����y(c��)�������c�y(c��)���������ì�ܵġ�Ҫ��õ��^��Ĝy(c��)���������轵�ͳ������l�ʣ����˕r(sh��)���L(zh��ng)���y(c��)�����Ȅt��(hu��)���ͣ�Ҫ����ߜy(c��)�����ȣ���ʹ�ø��l�ij��������ڿ՚���˥�p�ܿ죬�y(c��)�������t��(hu��)�sС��

�����y(c��)��ľ�����Ҫȡ�Q�����y(c��)������ݔ�r(sh��)�g�Ĝy(c��)�����Ⱥͳ����ڽ��|(zh��)�еĂ�ݔ�ٶ��@�ɷ��档��(gu��)������߳����y(c��)�����ܷ������˴����о�����(gu��)��(n��i)���P(gu��n)�W(xu��)��Ҳ�������P(gu��n)�о�����߂�ݔ�r(sh��)��(w��n)�Ĝy(c��)��������Ҫͨ�^(gu��)��ߜy(c��)���x����Ӌ(j��)�r(sh��)���ȁ�(l��i)��(sh��)�F(xi��n)������(du��)�ڳ����Ă�ݔ�ٶȵ���ߣ���Ҫͨ�^(gu��)���ø��l�ij����Q������(sh��)�F(xi��n)�����l�ij����Q�����Ĺ��������l�ʣ�һ���ǎ�ʮ��MHz�����ړQ�����Ĺ����l�ʺܸߣ�����˥�p�dz����@���@�͌�(du��)�y(c��)���x�����(q��)��(d��ng)��̖(h��o)�� �(q��)��(d��ng)Ч������˸���Ҫ�����ʹ�(q��)��(d��ng)��̖(h��o)�������l�ʾ�����߳ɞ���һ��(g��)�����о�����

1.3����������

��(d��ng)���w���(d��ng)�r(sh��)��(hu��)�l(f��)�������ƌW(xu��)�҂���ÿ������(d��ng)�ĴΔ�(sh��)�Q�������l�ʣ����Ć�λ�Ǻ�Ɲ���҂�?n��i)�������?t��ng)�������l�ʞ�20~20000��Ɲ����(d��ng)�������(d��ng)�l�ʴ���20000��Ɲ��С��20��Ɲ�r(sh��)���҂��� (t��ng)��Ҋ(ji��n)�ˡ���ˣ��҂����l�ʸ���20000��Ɲ�����Q�顰��������

���Ϳ����|(zh��)����һ�µģ������Ĺ�ͬ�c(di��n)����һ�N�C(j��)е���(d��ng)��ͨ���Կv���ķ�ʽ�ڏ��Խ��|(zh��)��(n��i)��(hu��)��������һ�N�����Ă�����ʽ���䲻ͬ�c(di��n)�dz��l�ʸߣ����L(zh��ng)�̡�

������һ�N�ڏ��Խ��|(zh��)�еęC(j��)е��ʎ�������ٶȃH��Ⲩ�İ��f(w��n)��֮һ���v��ֱ����^�ߡ�������(du��)ɫ�ʡ����նȡ����⾀��늴ň�(ch��ng)�����У���(du��)�ڱ��y(c��)��̎�ںڰ����л҉m���F����(qi��ng)늴Ÿɔ_���ж��Ȑ��ӵĭh(hu��n)���³����к�(qi��ng)���m��(y��ng)������

���ڳ������������ľ������ڽ��|(zh��)�Ђ����ľ��x�^�h(yu��n)���������ٶ����ஔ(d��ng)����(n��i)�c�l�ʟo(w��)�P(gu��n)�Ȫ�(d��)��(y��u)�c(di��n)��������ҕ��y(c��)�༼�g(sh��)��һ�N�����x����܊�£����I(y��)����ͨ���кܶ�đ�(y��ng)�á�

2FPGA��B

2.1 FPGA��(du��)���O(sh��)Ӌ(j��)�ı�Ҫ��

���@���҂����^һ��Ƭ�C(j��)�cFPGA���������c(di��n)��

��Ƭ�C(j��)���ɲ���C�Z(y��)�Ծ��̣��`���׃�����Է���Č�(sh��)�F(xi��n)��(f��)�s��ָ����ơ����nj�(du��)�r(sh��)����ƌ�(sh��)�F(xi��n)�����^�����M��߉�����^���������(zh��)�в�������(zh��)�з�ʽ���ⲿ����ʹ��I/O�ڔ�(sh��)�����ޣ���(du��)�ڽӿ���̖(h��o)���l�ʿ��������^�����\(y��n)�����ʼs���ʮ��Ɲ�������ⲿ������l�ʲ��ܳ��^(gu��)40MHz��

FPGA������Ӳ���Z(y��)�Ծ��̣��](m��i)��ָ�����ϵ�y(t��ng)�����������^���������к�(qi��ng)�ĕr(sh��)�����������߉�M����������(du��)��ͨ�Žӿ��e�Ǹ��ٽӿڿ��Ԍ���ͬ���ʲ�ͬ�f(xi��)�h����Ϻ͘�ӡ��\(y��n)�����ʼs��װ���Ɲ�������ⲿ������l�ʿɳ��^(gu��)100MHz��

����(g��)ϵ�y(t��ng)�ĺ��IJ����dz������հl(f��)���ƶ˺���̖(h��o)̎�����֣����dz����@�N���]�F(xi��n)���������O(sh��)Ӌ(j��)�Dz��Æ�Ƭ�C(j��)��������оƬؓ(f��)؟(z��)�a(ch��n)�������(q��)��(d��ng)��̖(h��o)����(du��)�ز��M(j��n)�Д�(sh��)��(j��)̎�������ƬF(xi��n)��(sh��)ݔ����

�Q�������(q��)��(d��ng)��̖(h��o)��Ч����ͬ�r(sh��)��(du��)�ڻز���̖(h��o)��̎����������(g��)�����y(c��)�࿂Ӌ(j��)�r(sh��)���������ڵľ��_�r(sh��)�g��һ��(g��)��Ҫ�ą���(sh��)����(du��)���(q��)��(d��ng)��̖(h��o)�l�ʵć�(y��n)����ƣ���Ӌ(j��)�r(sh��)�ĕr(sh��)�g���ƣ���ϵ�y(t��ng)�����ܱ�����Ҫ�l����

�F(xi��n)���������O(sh��)Ӌ(j��)�Dz��Æ�Ƭ�C(j��)���Д�Ӷ��r(sh��)Ӌ(j��)��(sh��)����(l��i)̎�����鷽��Ӌ(j��)�㶨�r(sh��)����ֵ������12MHz�����(l��i)Ӌ(j��)�㣬�o(w��)Փ�Dz����Dz����ķNλ���r(sh��)��/Ӌ(j��)��(sh��)����ʽ���(q��)��(d��ng)��̖(h��o)���l�ʾ��ȶ����ޣ��c��Փ��������^���S���M(j��n)���Д�֮ǰ��(zh��)���΄�(w��)�IJ�ͬ�����r(sh��)����Ӌ(j��)�r(sh��)ֵ���������_(d��)3us���ϵIJ��_���`������ö��r(sh��)���Č�(du��)�ⲿ���}�_�Ԅ�(d��ng)Ӌ(j��)�r(sh��)�Ĺ��ܣ������y(c��)��̖(h��o)�����ⲿ�Д����_���Ԅ�(d��ng)��(sh��)�F(xi��n)��̖(h��o)���ȵĜy(c��)����ԓ������Ӌ(j��)�r(sh��)����Ҳֻ���_(d��)��lus������Ӌ(j��)�r(sh��)�ľ��������چ�Ƭ�C(j��)���\(y��n)���ٶȣ�����߿��g��С��������TTL����Ԫ��(��8253/8254)��(l��i)��(sh��)�F(xi��n)Ӌ(j��)��(sh��)���·���@��Ӌ(j��)�r(sh��)�ľ��ȕ�(hu��)������ߣ���Ӌ(j��)�r(sh��)�l�ʿ���߿��g������8254���Ӌ(j��)�r(sh��)�l�ʲ����^(gu��)10MHz��ͬ�r(sh��)�O(sh��)Ӌ(j��)���ڲ��÷���Ԫ�����w�eҲ�ܴ�

��(du��)�ز����_(d��)�r(sh��)�g�Ĝy(c��)������(du��)�ز���̖(h��o)�ı��R(sh��)�;C��̎��Ҳ��ϵ�y(t��ng)�O(sh��)Ӌ(j��)���P(gu��n)�I�΄�(w��)����(sh��)�H�ϳ����Q��������������������1��2us�IJ��_���`���Ӌ(j��)�r(sh��)��������Ӌ(j��)�r(sh��)�`��Ҳ��us��(j��)�ģ���ô�C������(l��i)֮���`���������O(sh��)Ӌ(j��)�в���FPGA���g(sh��)�������䏊(qi��ng)��ĕr(sh��)��̎���������O�ߵ��\(y��n)���ٶ�(100MHz����)��ͬ�r(sh��)�����S���ă�(n��i)���YԴ�ֿ��Ԍ�ǰ���ĸ��N߉���ܼ�����һ�KоƬ��(n��i)����(sh��)�F(xi��n)���w�eҲ��С��F(xi��n)PGA(Field Programmable Gate Array)�ǿɾ���߉������һ�N���ɾ���߉�����Ǵ�Ҏ(gu��)ģ�����·���g(sh��)�l(f��)չ�Įa(ch��n)���һ�N�붨�Ƶļ����·���Y(ji��)��Ӌ(j��)��C(j��)ܛ�����g(sh��)���Կ��١�����ؘ�(g��u)����(sh��)��ϵ�y(t��ng)�����º�(ji��n)Ҫ��B�ɾ���߉������FPGA�İl(f��)չ���Y(ji��)��(g��u)�������c(di��n)��

2.2 �ɾ���߉����

�S������O(sh��)Ӌ(j��)���g(sh��)�c��ˇ�İl(f��)չ����(sh��)�ּ����·����ӹܡ����w�ܡ���СҎ(gu��)ģ�����·������Ҏ(gu��)ģ�����·(VLSIC)�l(f��)չ������Č��ü����·(ASIC)��ASIC�ij��F(xi��n)�����ˮa(ch��n)Ʒ�ijɱ��������ϵ�y(t��ng)�Ŀɿ��ԣ��sС���O(sh��)Ӌ(j��)�Ƶ������ߴ磬�Ƅ�(d��ng)�����(hu��)�Ĕ�(sh��)�ֻ��M(j��n)�̡�����ASIC�����O(sh��)Ӌ(j��)�����L(zh��ng)���İ�Ͷ�Y���`���Բ��ȱ���Ƽs�����đ�(y��ng)�÷�����Ӳ�����̎�ϣ����һ�N���`����O(sh��)Ӌ(j��)����������(j��)��Ҫ���ڌ�(sh��)�(y��n)�Ҿ����O(sh��)Ӌ(j��)�����Ĵ�Ҏ(gu��)ģ��(sh��)��߉�������Լ���ASIC���R��Ͷ��ʹ�ã��@������ɾ���߉�����Ļ���˼�롣

�ɾ���߉�����S��������칤ˇ�İl(f��)չȡ�����L(zh��ng)����M(j��n)���������ڵ�ֻ�ܴ惦(ch��)������(sh��)��(j��)����ɺ�(ji��n)��߉���ܵĿɾ���ֻ�x�惦(ch��)��(PROM)�����⾀�ɲ���ֻ�x�惦(ch��)��(EPROM)��늿ɲ���ֻ�x�惦(ch��)�����l(f��)չ���ɞ������ɳ���Ҏ(gu��)ģ�ď�(f��)�s�M��߉�c�r(sh��)��߉�Ŀɾ���߉����(CPLD)�ͬF(xi��n)��(ch��ng)�ɾ���߉�T���(FPGA)���S����ˇ���g(sh��)�İl(f��)չ�c�Ј�(ch��ng)����Ҫ������Ҏ(gu��)ģ�����١����ĵ�����FPGA/CPLD������ꐳ��¡���һ����FPGA��������������̎����(CPU) ��(sh��)��̎����(DSP)��(n��i)�ˣ���һƬF(xi��n)PGA���M(j��n)��ܛӲ���f(xi��)ͬ�O(sh��)Ӌ(j��)���錍(sh��)�F(xi��n)Ƭ�Ͽɾ���ϵ�y(t��ng)(SOPC��System On Programmable Chip)�ṩ�ˏ�(qi��ng)���Ӳ��֧�֡�

2.3 FPGA�ĽY(ji��)��(g��u)

FPGA���a(ch��n)�S����Altera��Xilinx��Actel��Lattice���ļҹ�˾������Altera ��Xilinx��Ҫ���a(ch��n)һ����;FPGA������Ҫ�a(ch��n)Ʒ����RAM��ˇ��Actel��Ҫ�ṩ����ʧ��FPGA���a(ch��n)Ʒ��Ҫ���ڷ��۽z��ˇ��FLASH��ˇ������Altera��˾һֱ��̎�ڿɾ���оƬϵ�y(t��ng)(SOPC)�I(l��ng)���ǰ�غ��I(l��ng)���λ����I(y��)���ṩ�����M(j��n)�Ŀɾ������������P(gu��n)ܛ�����ߡ�IPܛ��ģ�K�Լ���(y��u)����O(sh��)Ӌ(j��)������������FPGAϵ�а���FLEX6000��FLEXl0K��ACEX��Cyclone��CyclonelI��APEX20K��APEXII��Stratix��Mercury��Exclibur�ȡ�

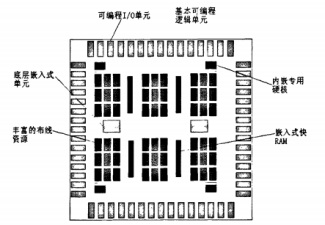

��(ji��n)����FPGA������6���ֽM�ɣ��քe��ɾ���ݔ��/ݔ����Ԫ�������ɾ���߉��Ԫ��Ƕ��ʽRAM���S���IJ����YԴ����Ƕ�빦�܆�Ԫ�̓�(n��i)Ƕ����Ӳ�˵ȣ���D��

�D2.1 FPGA�ă�(n��i)��߉�Y(ji��)��(g��u)

3 ����FPGA�y(c��)��ϵ�y(t��ng)Ӳ���Y(ji��)��(g��u)ƽ�_(t��i)

3.1 FPGA����Y(ji��)��(g��u)

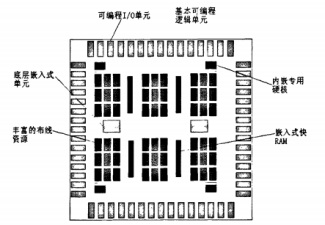

ԓ�O(sh��)Ӌ(j��)����FPGA�_(k��i)�l(f��)�壬ԓ�_(k��i)�l(f��)�弯���˶�N���ܣ������f(shu��)��VGA�ӿڡ�PS2 �I�P�ӿڡ�138�g�a�Ĕ�(sh��)�a�ܡ�32pin��ӿ�I/O���g����2.54mm����Ӳ����jtag�{(di��o)ԇ�ӿڡ�AS���d�ӿڡ�DA��(sh��)ģ�D(zhu��n)�QоƬTLC5620��USB�D(zhu��n)���ڽӿڡ����Q�����Ă�(g��)�p�|���I���_(k��i)�l(f��)��ľ��w�Y(ji��)��(g��u)���D��ʾ��

�D3.1 FPGA �_(k��i)�l(f��)��Y(ji��)��(g��u)

���O(sh��)Ӌ(j��)���濼�]Ҫ�õ��IJ�������ӿ�I/O��138�g�a�Ĕ�(sh��)�a�ܡ�jtag�{(di��o)ԇ�ӿڡ�AS���d�˿ڡ����Q���ȡ���������O(sh��)Ӌ(j��)˼·���\(y��n)�õ���LED�����p�|���I�@Щ���ܡ��\(y��n)���@Щ���ܵ�Ŀ���nj�(du��)FPGA�_(k��i)�l(f��)���M(j��n)��һ��(g��)�����ČW(xu��)��(x��)���Ķ���(sh��)�F(xi��n)һЩ��(ji��n)�εĹ��ܣ��M(j��n)�����^�y�Ĺ����~��һС����

ԓFPGA�_(k��i)�l(f��)�����õĺ���оƬ��ALTERA��˾��cyclone IV Eϵ��оƬ�����w��̖(h��o)��EP4CE6E22C8N��cyclone IV Eϵ�е�оƬͨ�^(gu��)����͵ijɱ���(sh��)�F(xi��n)���^�ߵĹ��ܣ�����cyclone IV Eϵ�е�������߅���ɺܶ�ͳɱ����հl(f��)�����ڲ�Ӱ������w���ܵ�ǰ���£���(ji��)ʡ�˺ܶ�ɱ���Cyclone IV E ϵ���ںܶ��I(l��ng)���T����o(w��)����ͨӍ�ȶ�����һЩ���Ѓr(ji��)ֵ�đ�(y��ng)�á�

cyclone IV E ����ϵ�о����������ԣ�

��1��6k��150k��߉��Ԫ��

��2�����_(d��)6.3Mb��Ƕ��ʽ�惦(ch��)����

��3�����_(d��)360��(g��)18*18�˷�������(sh��)�F(xi��n)DSP̎���ܼ��͵đ�(y��ng)�á�

��4���f(xi��)�h��ӵđ�(y��ng)�ã����Ԍ�(sh��)�F(xi��n)С��1.5W�Ŀ����ʡ�

��5���ͳɱ������ĵ�FPGA��(g��u)�ܡ�

�D3.1 cyclone IV E EP4CE6E22C8N ��̖(h��o)оƬ

���x��ԓ�_(k��i)�l(f��)��֮ǰ����(du��)��(sh��)�F(xi��n)һ��(g��)���wϵ�y(t��ng)��(y��ng)ԓ��һ��(g��)ȫ��λ���˽⣬ᘌ�(du��)ϵ�y(t��ng)�Ĺ��ܺ���Ҫ���YԴ��(l��i)���w�x��FPGA�_(k��i)�l(f��)�塣����ᘌ�(du��)cyclone IV Eϵ�е�EP4CE6E22C8N ��̖(h��o)оƬ�ľ��w���Æ�Ԫ������B��

��1�����пɾ��̵�ݔ��ݔ���˿�

��ԓFPGA�_(k��i)�l(f��)���У�I/Oλ������߅�IJ��֣�������32��(g��)��������FPGAоƬ�c����·����Ҫ�ӿڲ��֣�ͬ�r(sh��)����Ҳ��ɲ�ͬ��������Ԍ�(du��)I/O��̖(h��o)���(q��)��(d��ng)��ƥ�������ھ���(xi��)����ĕr(sh��)���Еr(sh��)���˹�(ji��)ʡ�YԴ��?y��n)��˳���ĺ?ji��n)���ԣ�Ŀǰ�����(sh��)FPGA �˿ڶ��O(sh��)Ӌ(j��)�ɾ��пɾ����Ե�I/O�ӿڡ�FPGAᘌ�(du��)�ⲿ�O(sh��)��Ľӿھ��п��Ծ���(xi��)����ݔ��оƬ�Ĺ��ܣ������@�Ӿʹ��������FPGA���������ԡ�

��2���^���S���IJ����YԴ

��cycloneϵ�е�����оƬһ�ӣ�F(xi��n)PGA�����;��зdz��S���IJ����YԴ�������@��(g��)���c(di��n)���Խo�_(k��i)�l(f��)���̎����dz���������x���x���(ji��n)���IJ�����ʽ���(ji��n)����㷨���@Щ�����ĽY(ji��)��(g��u)���B�����L(zh��ng)�Ȍ�(du��)��̖(h��o)�Ă�ݔ�ٶ����˷dz���Ҫ��Ӱ푣������㷨�ă�(y��u)�ȼ�(j��)���㷨�ă�(y��u)�����@���Ȟ���Ҫ�ˣ�������ֱ�ӿ��Դ_���\(y��n)���ٶ��ˡ�

��3���^�͵Ĺ���

Cyclone IV Eϵ��оƬ�����˽�(j��ng)�^(gu��)��(y��u)�����60nm�Ĺ�ˇ�����ă�(n��i)��늉�����(du��)��ǰ�״��Ķ��������͡��@�ڴ�Ҏ(gu��)ģ�����·�Ĺ����O(sh��)Ӌ(j��)�мȹ�(ji��)ʡ���YԴ���ֽ�����ϵ�y(t��ng)���w�Ĺ��ġ��@��(du��)���YԴ��(y��u)���c�YԴ�ĺ����ֲ����@��ͬ�����ăr(ji��)ֵ���ڡ�

��4��ȫ����O(sh��)Ӌ(j��)�YԴ

ԓϵ��FPGA����оƬ�\(y��n)����������IP��(k��)Ҳ�dz����죬ʹ�õ���Quarters II�_(k��i)�l(f��)ܛ���������dz����{(di��o)ԇ����߀�����d���·�D����ȷ��涼�dz��ı�������Ƕ��ʽ̎�������õ���NiosII̎�����@��Ŀǰ��������ͨ�õ�Ƕ��ʽ̎������������ʹ�þC���·�\(y��n)�еĸ����������r(sh��)��l�ʸ��ӷ�(w��n)����

��5��ȫ��λ�ĕr(sh��)犾W(w��ng)�j(lu��)

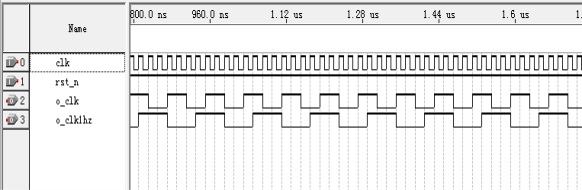

ԓоƬ�r(sh��)犾W(w��ng)�j(lu��)�YԴ�S������������PLL�M(j��n)�з��l�����l�������{(di��o)��IP�ˌ�(du��)��Ҫ�ĕr(sh��)��l���M(j��n)�о��w�O(sh��)����������оƬ̎��ϵ�y(t��ng)�п��Ԍ�(du��)��ͬ�ĕr(sh��)���̖(h��o)�M(j��n)��ͬ�r(sh��)̎����

3.2 �����y(c��)��������

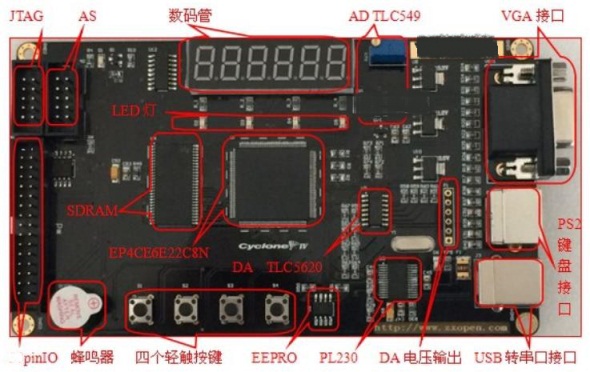

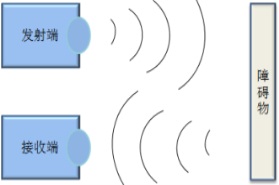

���Ƚ�B�����y(c��)�����x��ԭ������ν�B�����y(c��)��ģ�K�������y(c��)��Ļ���ԭ�������@���J(r��n)�飬�҂�֪�����ڿ՚���Ă����ٶȴ�s��0.34ǧ��/�롣�����ڿ՚��еĂ����ٶȴ��Ҳ��0.34ǧ��/�룬���@��(g��)�ٶ������h(hu��n)��׃���e��С���r�ҳ����IJ��L(zh��ng)����(du��)�ڿ՚��еđҸ��w��ֱ���^�����������Ч���@���^(gu��)�՚��еđҸ��w����ֱ�����^С���ϵK����Կ����J(r��n)�����ڿ՚��еĂ����ٶȻ������ԾS����0.34ǧ��/�롣�����@��(g��)������׃���ٶȣ�ֻ��y(c��)����l(f��)��ȥ�Լ������(l��i)�ĕr(sh��)�g�Ȼ����ͨ�^(gu��)һ����Ӌ(j��)�㣬�Ϳ��Եõ��l(f��)��˵�Ŀ��(bi��o)���w�ľ��x�ˡ�

�����ϵij����y(c��)�����x��ԭ��D�Ϳ���֪�����xS���Ա��ܺ�(ji��n)���ı��_(d��)����(l��i)�ˡ������ٱ�ʾ��V�������İl(f��)�䵽���յĕr(sh��)�g���T���@�Ӿ��x�Ϳ��Ա����_(d��)��S=V*T/2���D3.2�еķ����ɷQ���g�Ӝy(c��)�෨��߀��һ�Nֱ�Ӝy(c��)��ķ�����ֱ�Ӝy(c��)����nj��y(c��)��ϵ�y(t��ng)�İl(f��)��˿ںͽ��ն˿ڌ�(du��)��(zh��n)���l(f��)��ij���ֱ���M(j��n)����նˣ��@�ӾͿ���ֱ��Ӌ(j��)�����y(c��)���ľ��x�ˡ��@�N�y(c��)��ϵ�y(t��ng)�����H�H�����ڳ����y(c��)��ϵ�y(t��ng)����һЩ����y(c��)�ࡢ�t��y(c��)���ϵ�y(t��ng)����Ҳ����һ���r(ji��)ֵ�đ�(y��ng)�á�

�D3.2 �����y(c��)�����x��ԭ��D

�ڱ��O(sh��)Ӌ(j��)�����ó����ڿ՚��еĂ���ԭ��������S=V*T/2���P(gu��n)ϵӋ(j��)���1���ĕr(sh��)犸��ƽ��(g��)��(sh��)�����þ��x��λ�����(xi��ng)�B�ӣ�����(g��)�M(j��n)λ�ķ�ʽӋ(j��)�������x��

�D3.3 ����ģ�K

����FPGA�ij����y(c��)��ϵ�y(t��ng)���õij���ģ�K��̖(h��o)��HC_SR04������(sh��)�H�ϲ��õ��ǽoģ�K�ϵ�trig�˿�һ��(g��)�|�l(f��)�ƽ�����|�l(f��)�����İl(f��)����

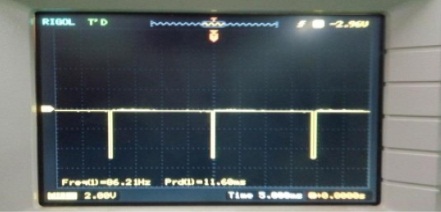

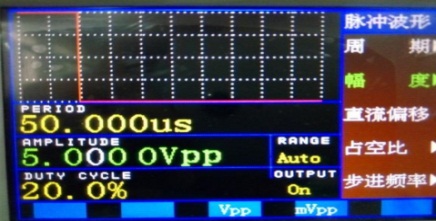

���ȣ���ʹ��ԓģ�K֮ǰ����(du��)ԓ����ģ�K�M(j��n)���˺�(ji��n)�εĶ˿ڜy(c��)ԇ������늉�Դ�oԓģ�K����5V��늉���������̖(h��o)�l(f��)�����a(ch��n)��һ��(g��)10us�ĸ��ƽ�}�_��̖(h��o)��������̖(h��o)�ӵ�trig�ӿ��ϣ��@�Ӿ�����ˌ�(du��)ԓ����ģ�K���|�l(f��)��Ȼ��ʾ����̽�^���ڳ���ģ�K��echo�˿��ϣ��^��ʾ������(hu��)�@ʾ������̖(h��o)��

�D3.4 ʾ�����^�y(c��)�D

�D3.5 ��̖(h��o)Դ��̖(h��o)�D

�ɈD3.5�е���̖(h��o)Դ���Կ������O(sh��)��ռ�ձȞ�20%���}�_늉���5V�����ڞ�50us���@����̖(h��o)Դ�Ϳ��Ԯa(ch��n)��һ��(g��)10us���B�m(x��)�}�_�������}�_��̖(h��o)�ͽotrig�˿ڣ�Ȼ���ڳ���ģ�K�ϵ�echo�˿��ϼ���ʾ������(l��i)�y(c��)��echo�ϵ���̖(h��o)׃�����D3.4��ʾ����������Ŀ���echo��̖(h��o)Ҳ�ʬF(xi��n)������׃������ԭ����ǽotrigݔ�����̖(h��o)��������׃����ÿ�ν�(j��ng)�^(gu��)10us���B�m(x��)���ƽ�������͕�(hu��)�l(f��)��һ��(g��)�{(di��o)�Ƶ��}�_��̖(h��o)��ԓ�{(di��o)����̖(h��o)���غ�echo�˵���̖(h��o)�͕�(hu��)�ɸ��ƽ˲�g׃�ص��ƽ�ˣ�����echo��̖(h��o)��������׃������trig��̖(h��o)��������׃������ġ�߀��һ��(g��)ֵ��ע��Ć�(w��n)�}���^��ʾ�����ķ��ֵ���Կ���echo�����ĸ��ƽ�ͽo����ģ�K��VCC�˿���ݔ���늉���̖(h��o)�ĸ��ƽֵ��һ�Ӵ�ģ���˾�Ҫ���]FPGA�_(k��i)�l(f��)���I/O�ӿ������ܵ�����͉�ֵ��������Xilinx��Basysϵ�е��_(k��i)�l(f��)��I/O�ӿ�늉�����ֵ��3.3V���@�N��r��Ҫ�oecho�ӿڼ�һ��(g��)�։���衣���ⷵ��늉��^(gu��)�����(du��)оƬ���һ���̶ȵēp������ALTERAϵ���_(k��i)�l(f��)���I/O�ӿ�һ����r���Գ���5V��늉�ֵ����˿���ֱ�ӌ�I/O�ӿ��cecho�˿ں�trig�˿ڽ���һ��

4�����y(c��)��ϵ�y(t��ng)�����O(sh��)Ӌ(j��)������

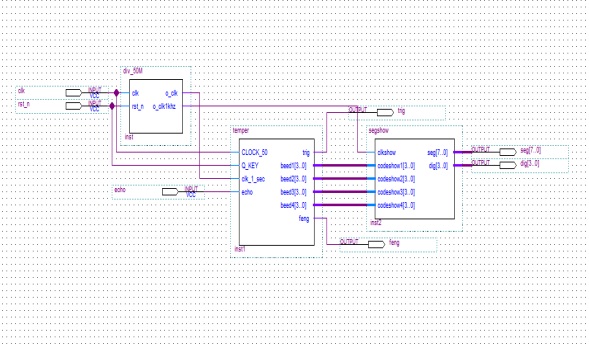

4.1 �������̈D

�D�o����ϵ�y(t��ng)ܛ���O(sh��)Ӌ(j��)�����w��ܣ���(sh��)�H������FPGA��(n��i)�ĸ���(g��)���M(j��n)�̶��Dz��Ј�(zh��)�еģ���ÿ��(g��)���M(j��n)�̶����Ǫ�(d��)����ģ�K����˳����O(sh��)Ӌ(j��)�����ǰ������ķ����O(sh��)Ӌ(j��)�ģ����Ƿ��x�ɸ���(g��)С����ģ�K�M(j��n)���O(sh��)Ӌ(j��)�C�ϵģ���Ҫ��(y��n)����ƕr(sh��)��

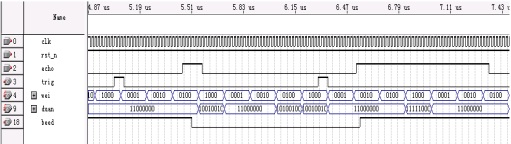

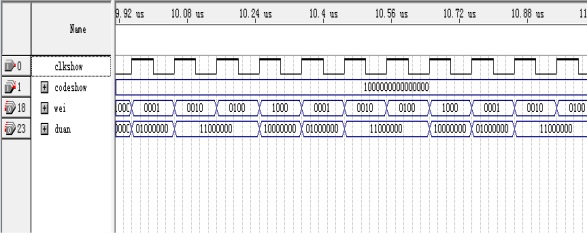

�����հl(f��)����ؓ(f��)؟(z��)�a(ch��n)�������(q��)��(d��ng)��̖(h��o)��Ҫ���l�ʞ�50MHz��ռ�ձȞ�50�ķ�����̖(h��o)���(q��)��(d��ng)�����Q������ͬ�r(sh��)����Ӌ(j��)��(sh��)���_(k��i)ʼӋ(j��)��(sh��)���z�y(c��)�ز���Ӌ(j��)��(sh��)��ֹͣӋ(j��)��(sh��)��Ӌ(j��)�������@ʾݔ����

�D4.1 ϵ�y(t��ng)ܛ���O(sh��)Ӌ(j��)��D

4.2����������������ģ�K���a��

ͨ�^(gu��)�����Ƴ����Ԍ�(sh��)�F(xi��n)�����y(c��)���Լ���(d��ng)�y(c��)�����xС��һ���L(zh��ng)�ȕr(sh��)�����Q����(b��o)������(b��o)�����x����ͨ�^(gu��)�Ĵ��a����(sh��)�F(xi��n)��Ҫ�Ĉ�(b��o)���ľ��x��������ͨ�^(gu��)���η���ĽY(ji��)������D��ʾ��

�D4.2 �y(c��)�ಢ��(b��o)��

���lģ�K���a��

Endmodule

�������a��ݔ����1KHZ�r(sh��)犣���֮���M(j��n)���g�a�����衣���lģ�K�������Dʾ��

�D4.3 ���lģ�K����

�g�a��ģ�K���a��

�g�a��ģ�K��ͨ�^(gu��)����z�y(c��)����1KHZ�r(sh��)�ݔ�룬�ќy(c��)�����ľ��x�@ʾ����(sh��)�a���ϣ��g�a��ģ�K�������D��ʾ��

�D4.4 ��(sh��)�a���@ʾ����

4.3플�ԭ���D플�ԭ��D��Ҫ�֞�����(g��)ģ�K���քe����lģ�K��������ģ�K���g�a��ģ�K��߀�г���ģ�K�ӿڣ��Լ���(sh��)�a��ģ�K�ӿڡ����D��ʾ��

�D4.5 ԭ��D

�˴ε���ĩ�����I(y��)���mȻ��(j��ng)�v��һ�δε����y�����e���˺ܶ����F�Ľ�(j��ng)�(y��n)��������(g��)�O(sh��)Ӌ(j��)���^(gu��)���������Ć�(w��n)�}��Ҫ���������c(di��n)����һ�����A(ch��)֪�R(sh��)���յIJ��ι̣���(du��)��(sh��)���ϵă�(n��i)�����ⲻ���أ��](m��i)�����պþ������P(gu��n)֪�R(sh��)���ڶ��������y(c��)���@��(g��)ģ�K����ľ���(xi��)�](m��i)��˼·����(du��)VerilogHDL�Z(y��)�ԵIJ���Ϥ��(d��o)��ֱ���ڳ�����ʹ�ó˳�����ȡ��ȷ�̖(h��o)���mȻ���g���](m��i)�Ј�(b��o)�e(cu��)�������\(y��n)���������](m��i)�нY(ji��)����Ҳ���ܾC�ϳ�һ��(g��)�������·�����������P(gu��n)֪�R(sh��)���յIJ���ȫ�棬ȱ��ϵ�y(t��ng)�O(sh��)Ӌ(j��)�Ľ�(j��ng)�(y��n)��

�@�δ����I(y��)�M(j��n)һ�������ҵČW(xu��)��(x��)�B(t��i)�ȣ��W(xu��)��(hu��)�ˌ�(sh��)�����ǣ���(y��n)֔(j��n)?sh��)����L(f��ng)����(du��)�Լ�Ҫ��(y��n)��Ҫ���܉�һ֪��⣬Ҫ���������װס���������Dz��õģ����������ܡ����ʡ������Щ��Ҫ�IJ��E��������ɣ����H��(hu��)���M(f��i)�r(sh��)�g��߀��(hu��)�m���䷴�����X(ju��)�Ä�(d��ng)��֮ǰ���^�X�������ԓ��ô�����@һ�c(di��n)�Ǻ���Ҫ�ġ���Ŀǰ��(l��i)�f(shu��)���ҵĄ�(d��ng)�������mȻ��һ�c(di��n)�������룬ͨ�^(gu��)�ҵIJ�иŬ�������@���棬�ҿ���(hu��)�õ���ߡ��@һ�c(di��n)���҈�(ji��n)�š���?y��n)�e���������ģ���Ҳһ����������

ȫ���Y��51hei���d��ַ��

FPGA�������.rar

(1.24 MB, ���d��(sh��): 160)

FPGA�������.rar

(1.24 MB, ���d��(sh��): 160)

����FPGA�ij����y(c��)��.docx

(1.11 MB, ���d��(sh��): 116)

����FPGA�ij����y(c��)��.docx

(1.11 MB, ���d��(sh��): 116)

Screenshot_20191223_105349.jpg (113.53 KB, ���d��(sh��): 182)

| �gӭ���R (http://www.zg4o1577.cn/bbs/) | Powered by Discuz! X3.1 |