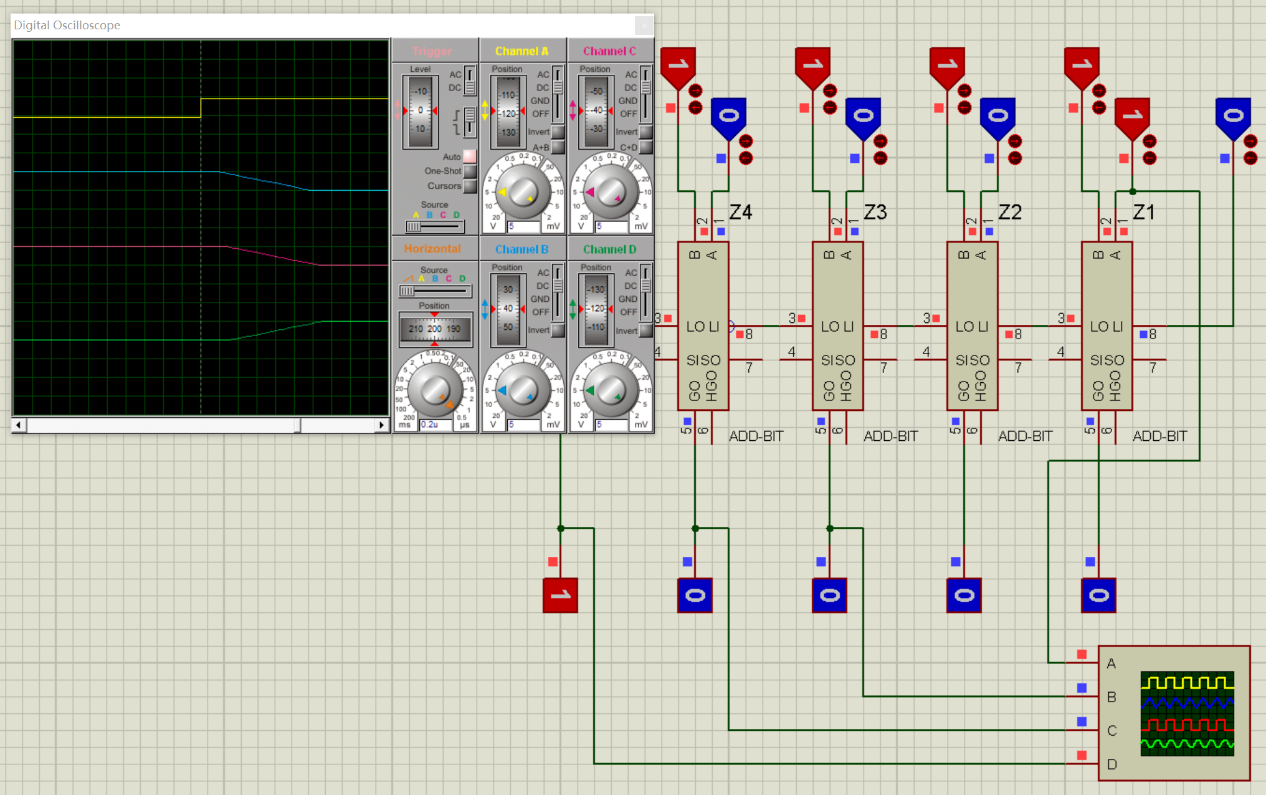

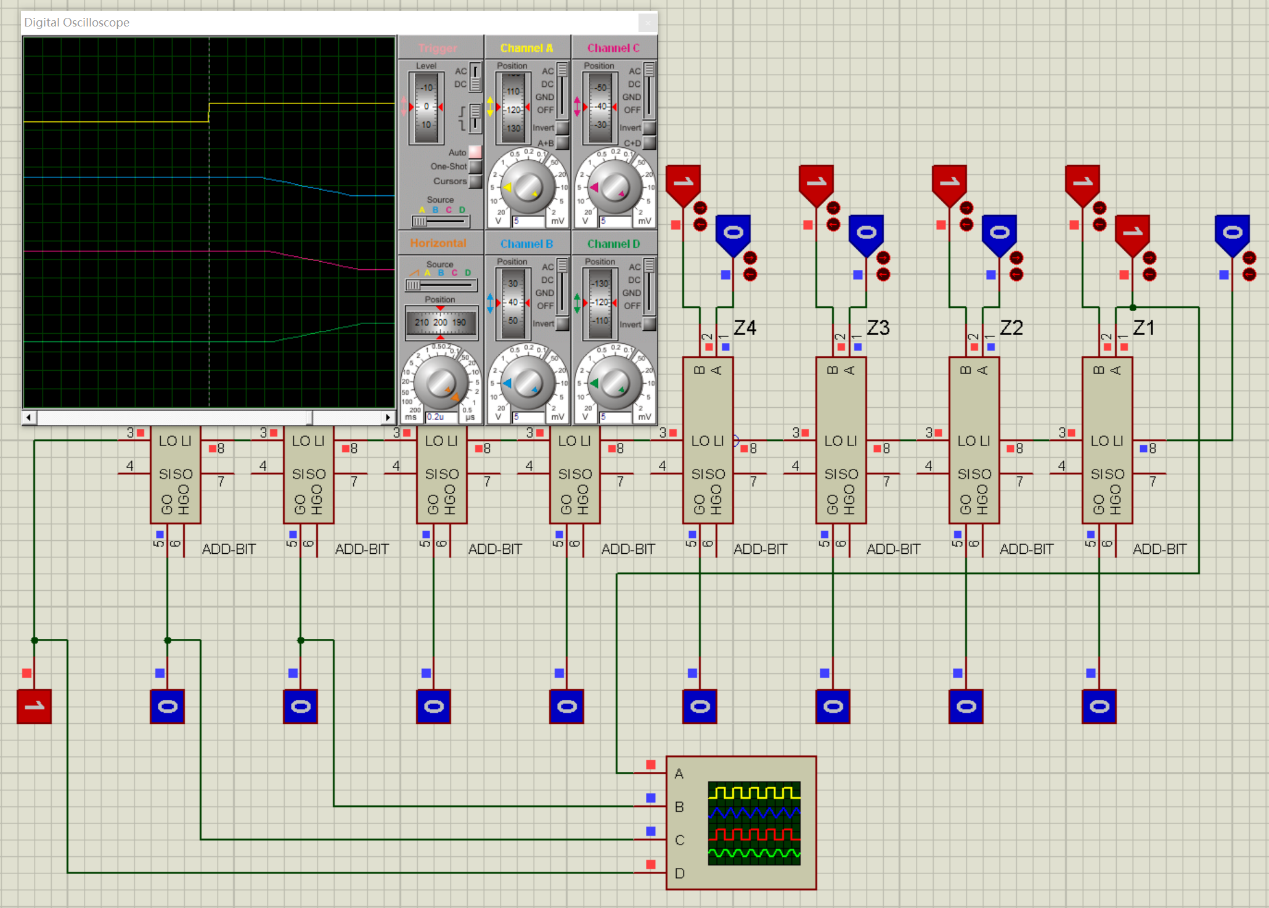

加法器延遲 | 4位 | 8位 | 16位 | 32位 |

RCA | 1.3微秒 | 1.64微秒 | 2.4微秒 | 3.8微秒 |

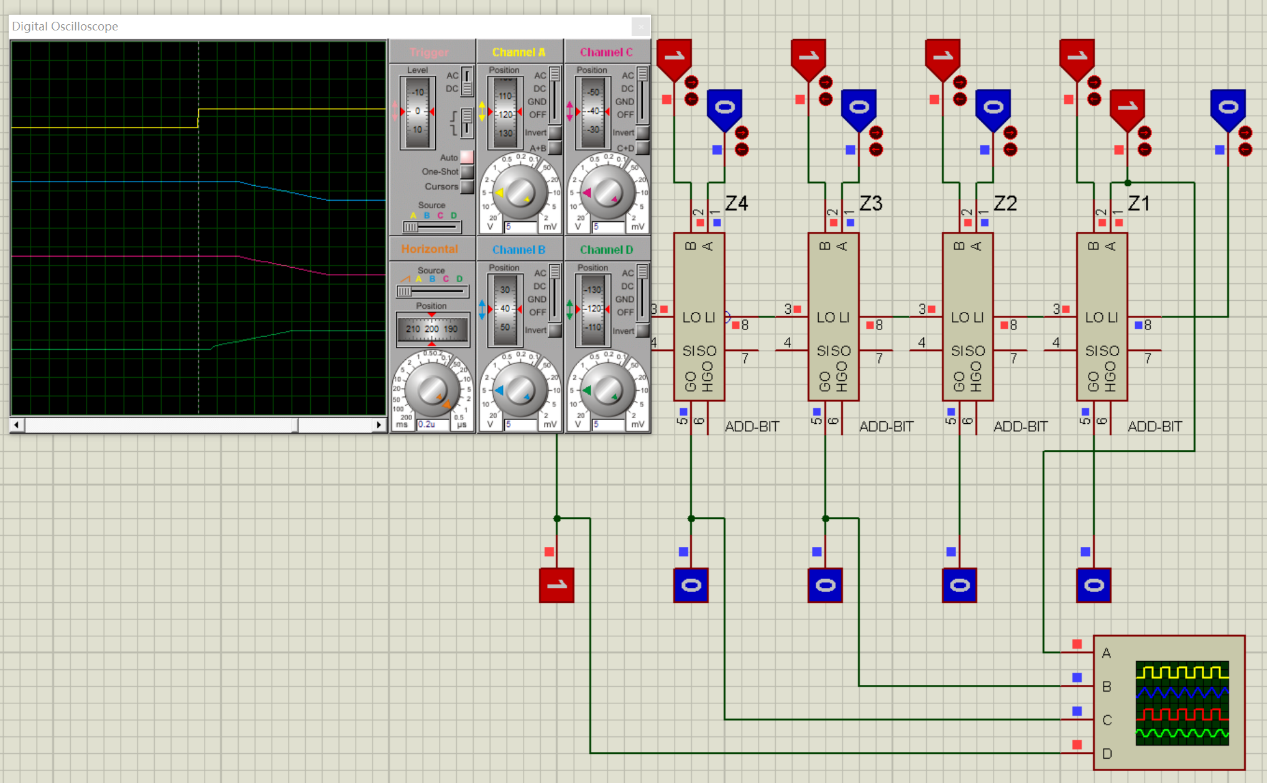

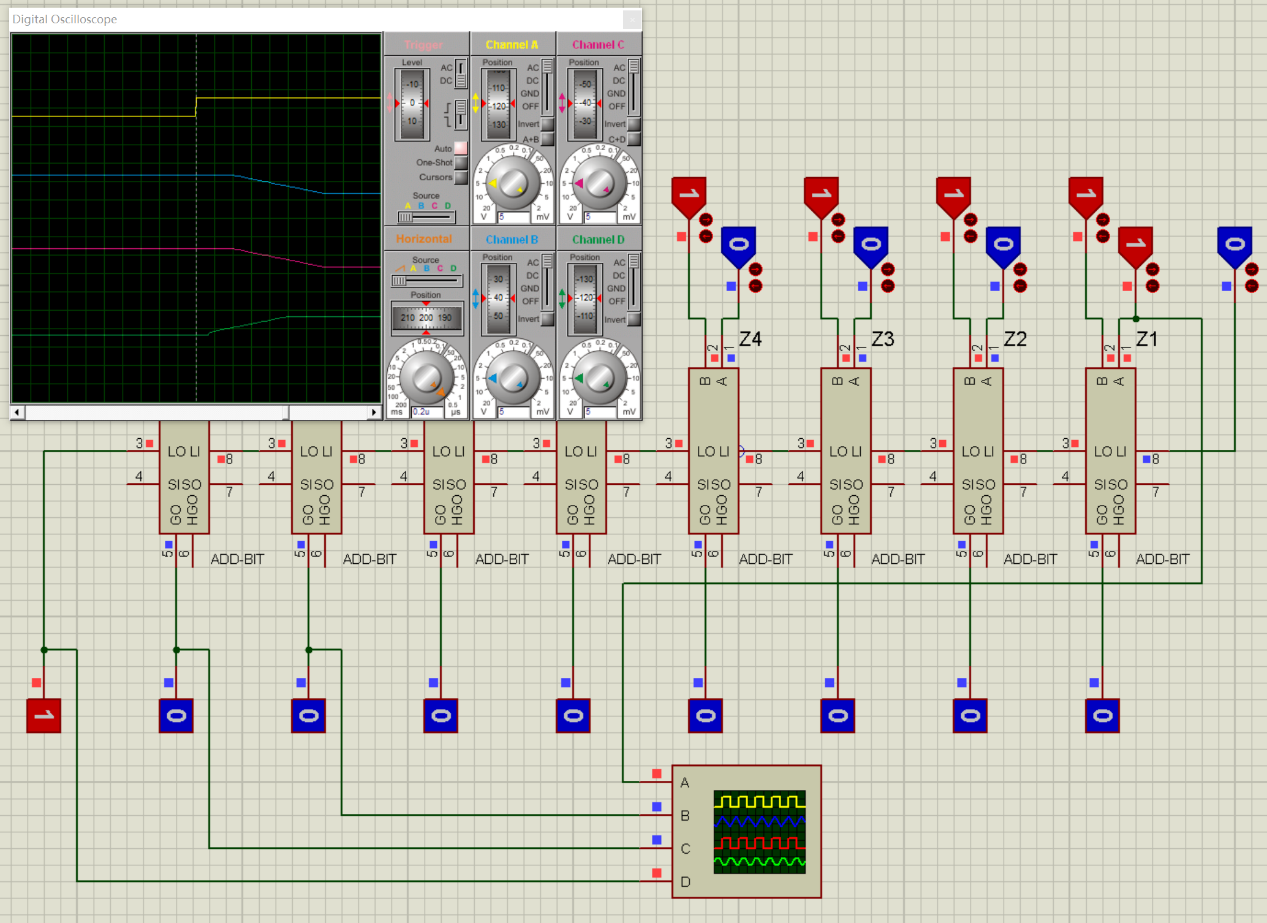

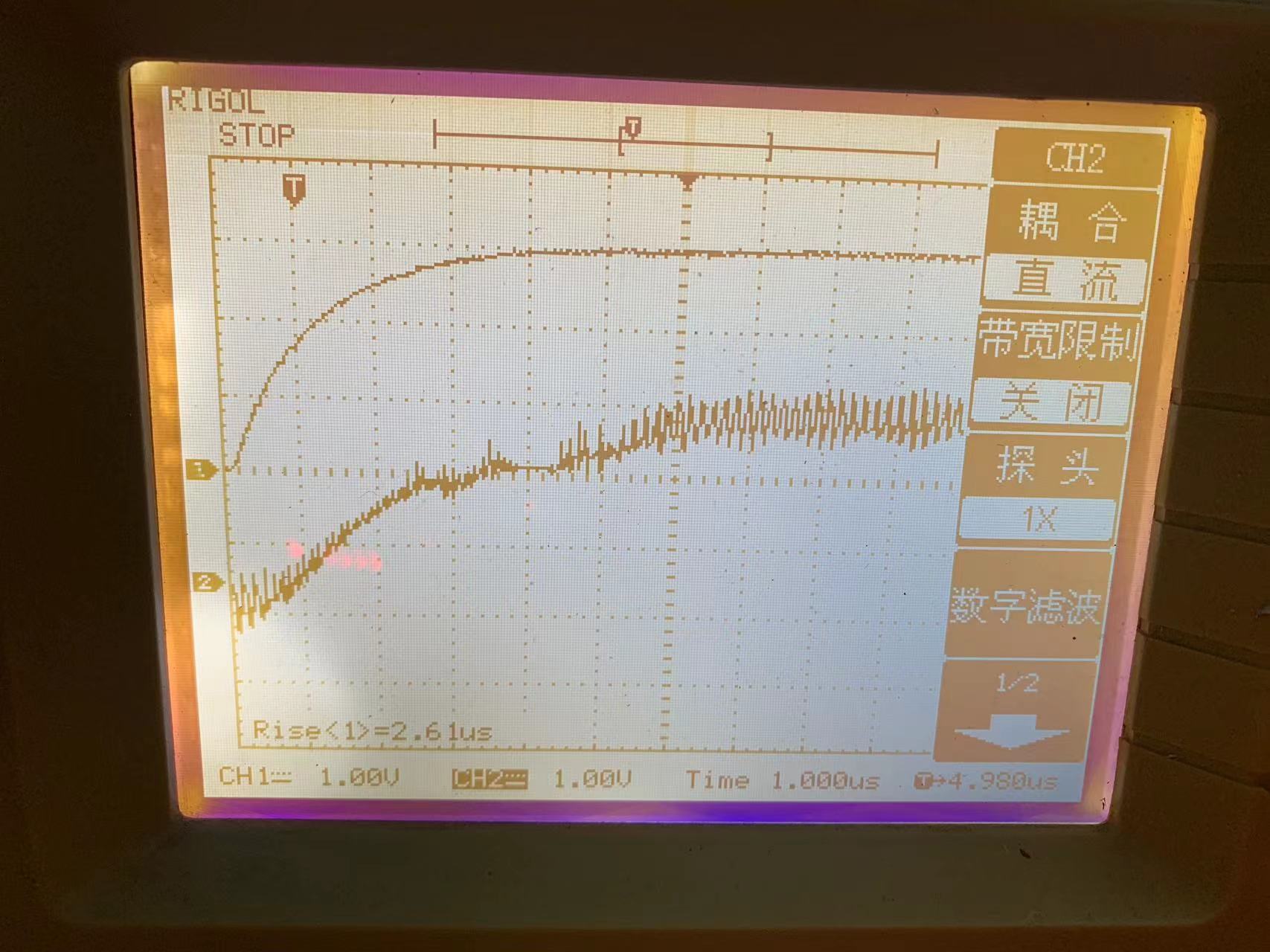

SCA | 1.4微秒 | 1.4微秒 | 1.4微秒 | 1.4微秒 |

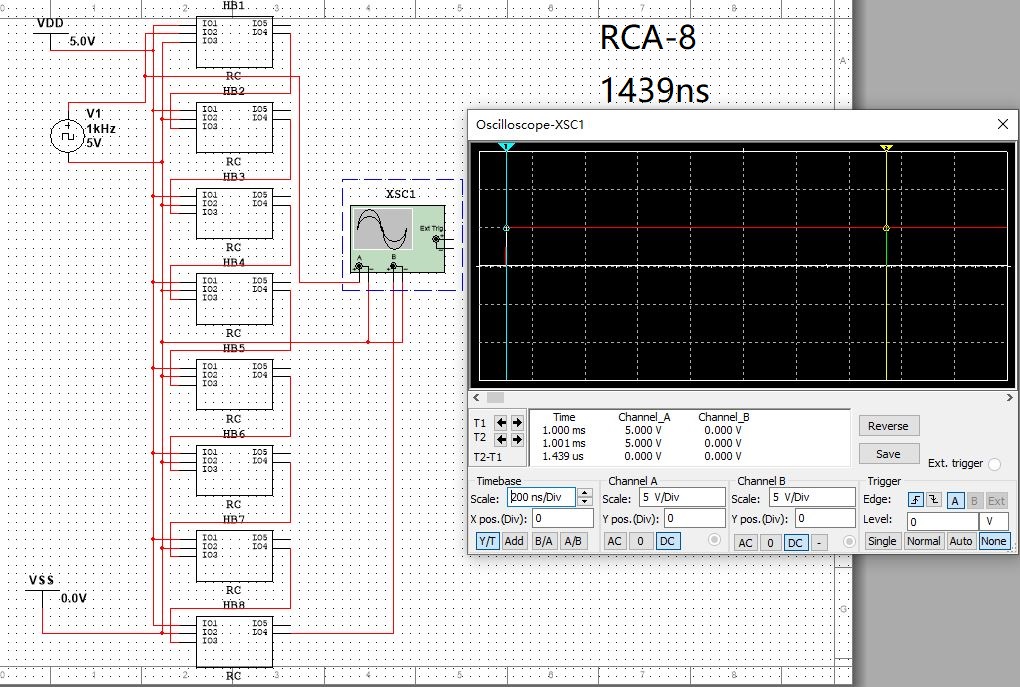

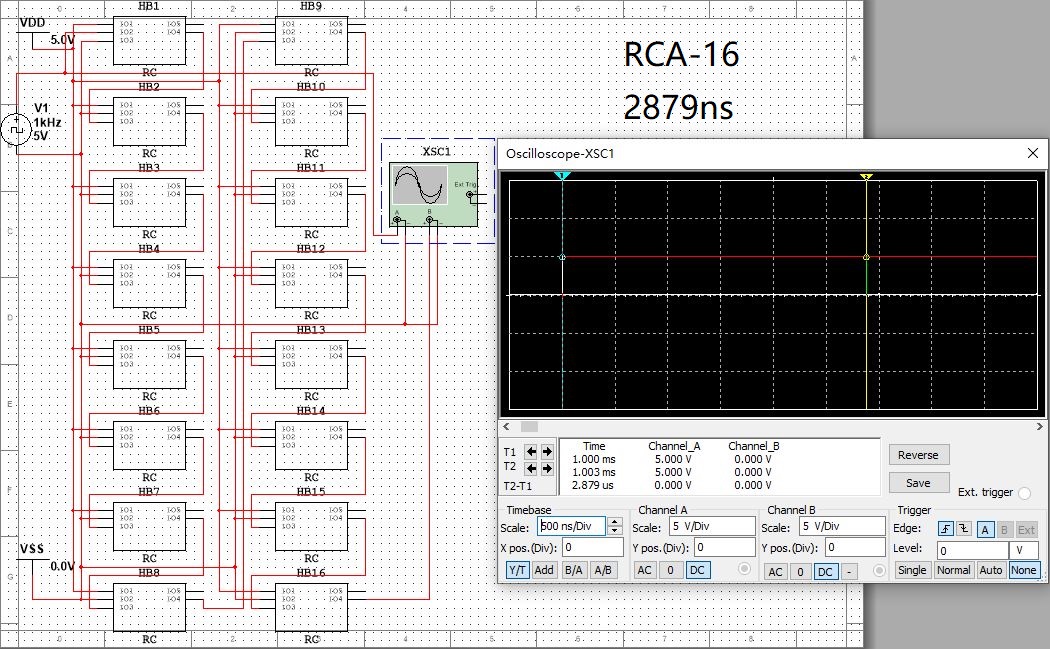

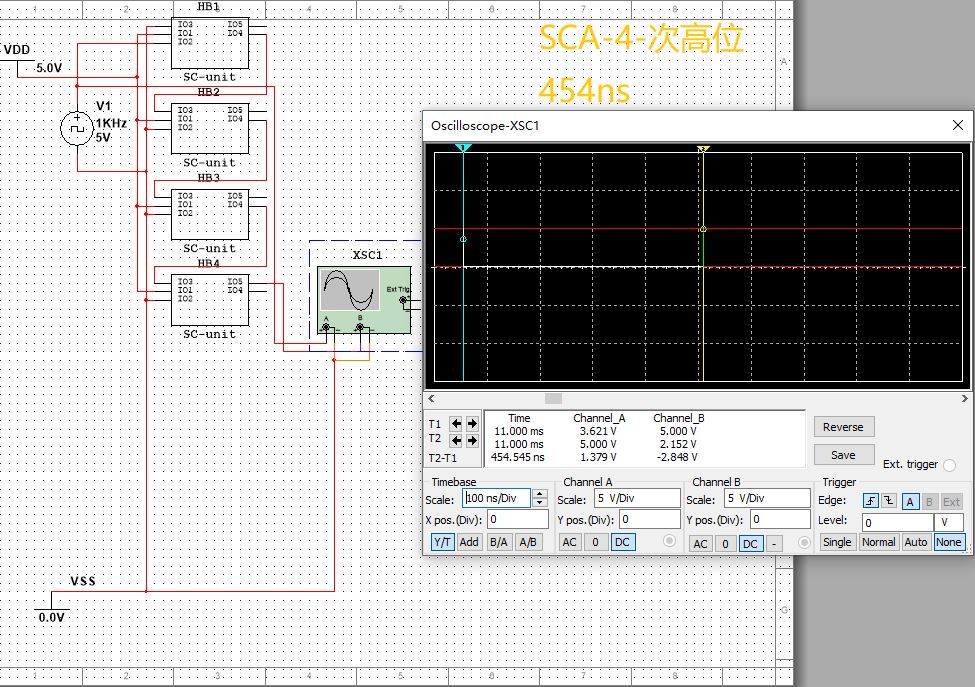

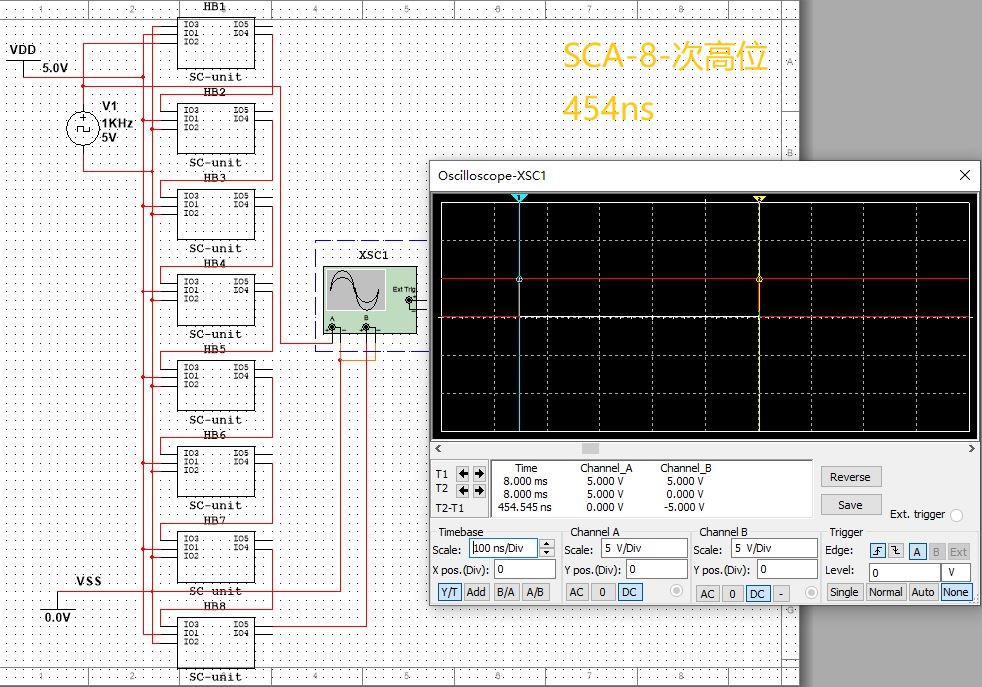

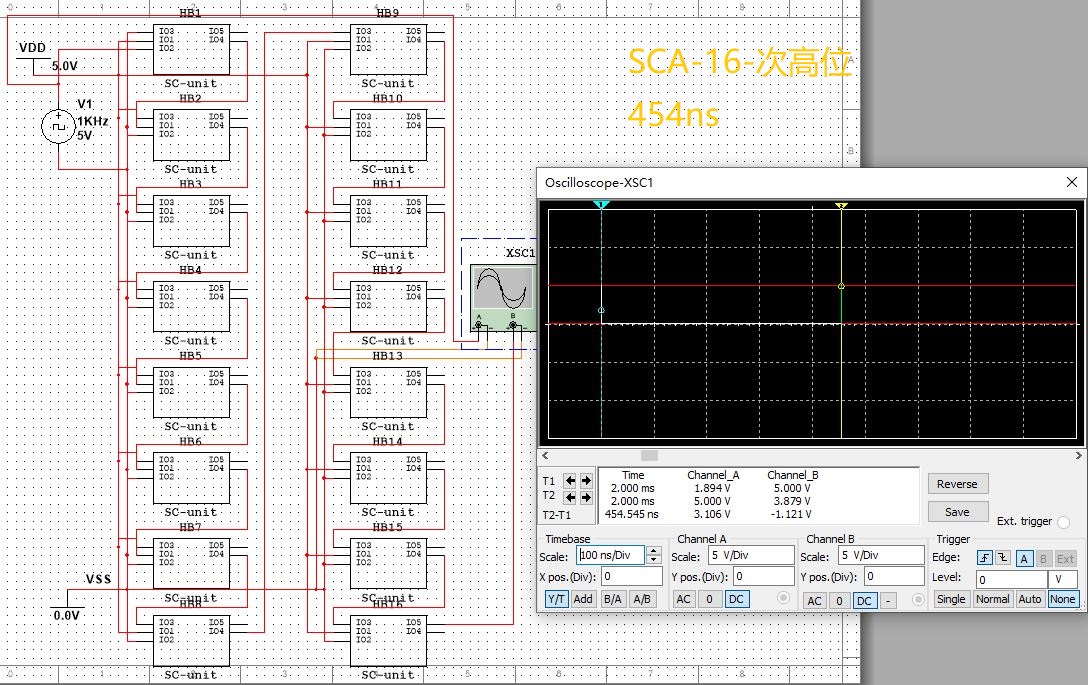

加法器延遲 | 4位 | 8位 | 16位 |

RCA | 723納秒 | 1439納秒 | 2879納秒 |

SCA | 454納秒 | 454納秒 | 454納秒 |

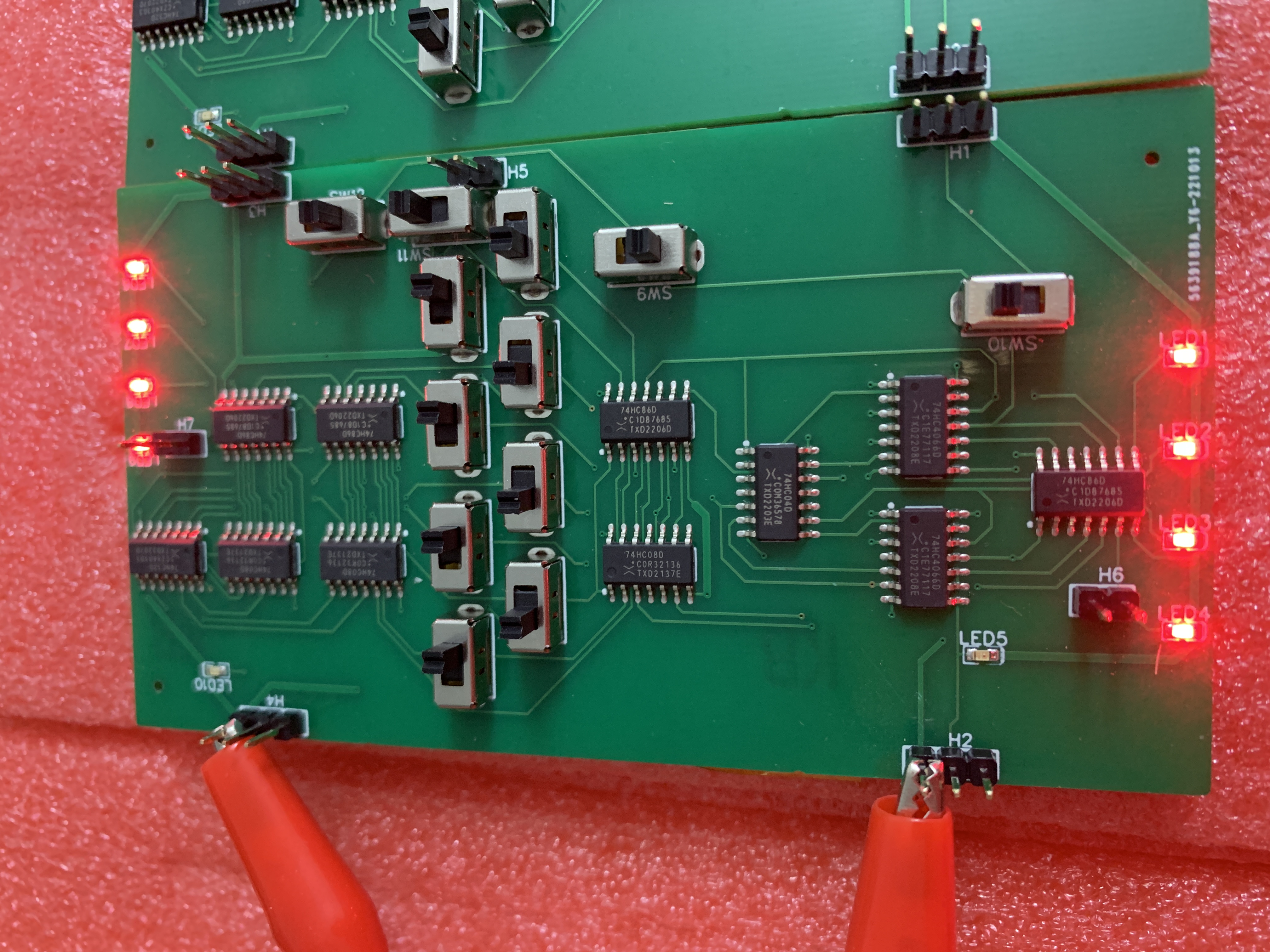

Hephaestus 發表于 2022-10-31 21:48

我覺得你的做法真沒什么實際意義,跟74系列小規模集成電路搭建CPU一樣無聊。

弄一個FPGA開發板,就算你 ...

wufa1986 發表于 2022-11-1 07:54

你這只是理論而已

yzwzfyz 發表于 2022-11-1 11:12

速度 = 距離/時間。

對于命題而言實際上是時間長短,而不存在距。

時間的長短認定,必須有起點和終點。

1951387254 發表于 2022-11-1 14:23

速度 = 距離/時間。 對于命題而言實際上是時間長短,而不存在距。 時間的長短認定,必須有起點和終點。 1、 ...

Y_G_G 發表于 2022-11-1 15:14

你是做什么的?或者是說你要做什么?為什么對"加法器速度"如此的執著?

我個人認為,這種古怪的問題是由于新手 ...

Ele_insect 發表于 2022-11-1 17:04

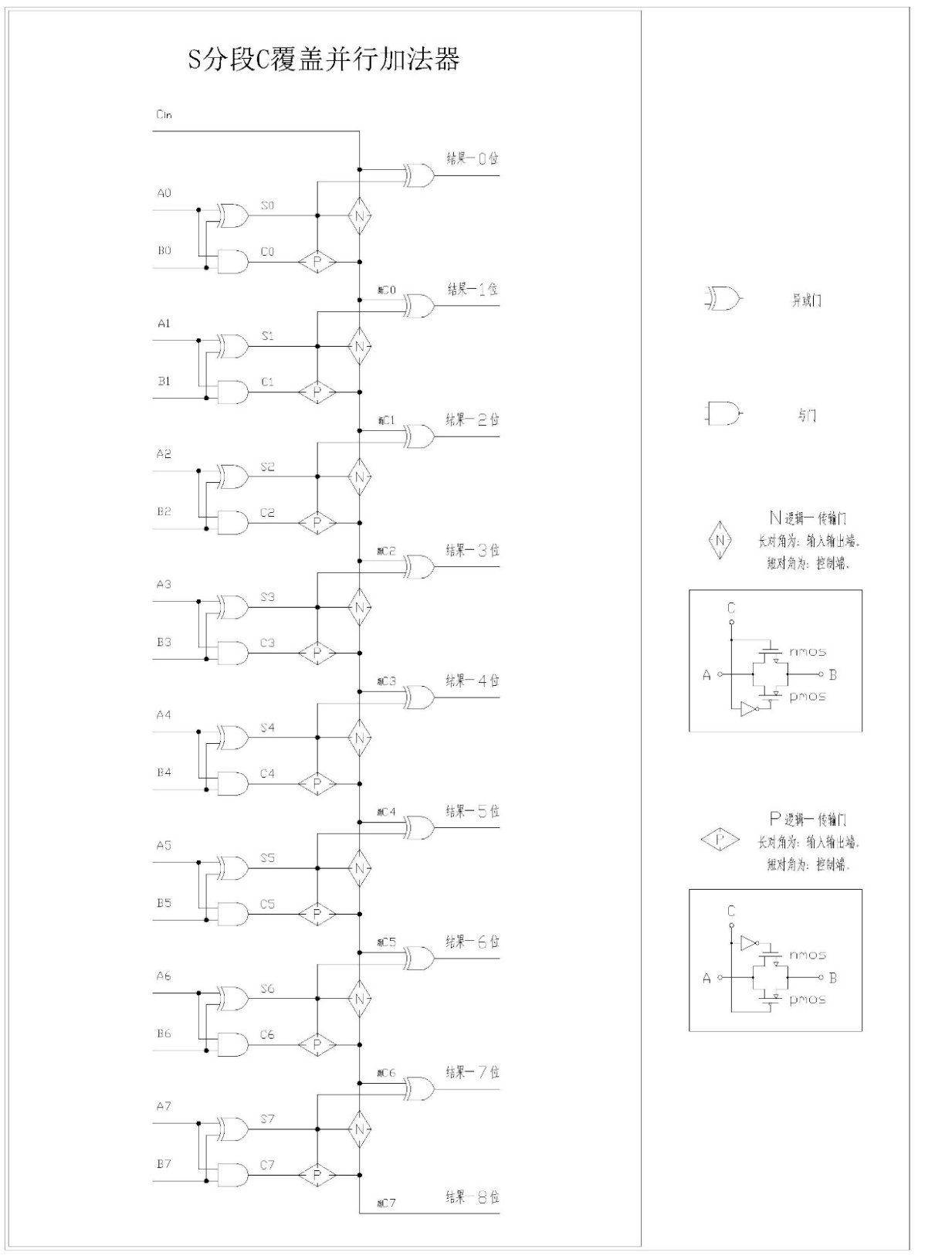

我要做:一個拓撲結構和RCA一樣簡單的,晶體管數量少的,速度比CLA快的加法器。

只需要簡單的并聯,就 ...

Y_G_G 發表于 2022-11-1 19:24

你的專業是什么?

FPGA還是嵌入式?

yzwzfyz 發表于 2022-11-2 10:22

【加法器里面有,最長路徑的,這個是最慢的。只用測量這個的速度,就好了!】

1、電速如光速,最長路徑能 ...

風吹過后 發表于 2022-11-6 21:01

加法器的速度翻倍,ALU的計算能力會不會翻倍?cpu的性能,能不能翻倍?

51單片機換上這個加法器,性能會 ...

Ele_insect 發表于 2022-11-7 10:44

在微處理器芯片中,加法器是進行數字信號處理的核心,同時也是微處理器中進行數據處理的關鍵部件。

加法 ...

Ele_insect 發表于 2022-11-16 09:34

我自己覺得,這個加法器挺好的,能加快ALU的計算速度,提升CPU性能!

| 歡迎光臨 (http://www.zg4o1577.cn/bbs/) | Powered by Discuz! X3.1 |