��(bi��o)�}: ��(n��i)����������ô�ӵģ���֪���� [��ӡ���]

����: hubaba �r�g: 2016-3-25 16:48

��(bi��o)�}: ��(n��i)����������ô�ӵģ���֪����

��������� hubaba �� 2016-3-28 13:44 ��

ժҪ

�I��X����Ҫ�ą���ָ��(bi��o)֮һ�ǿ죬�������c����DDR�Q���������҂�Ԕ��(x��)��BDDR�r���·�c�B�����a(b��)��

�I��X����Ҫ�ą���ָ��(bi��o)֮һ�ǿ죬�������c����DDR�Q�����ԏ���һƪ���½�B����N�DDR�����Թ��ܺ����҂�Ԕ��(x��)��BDDR�r���·�c�B�����a(b��)��

�D1 DDR4

һ���r���P(gu��n)ϵ

SDRAM��DDR��DDR2��DDR3��DDR4���x���r�����w��ƣ��^(q��)�e�����g���r�g��������ʽ�����������ܵȡ�

�ԈD������ʽ�f����(n��i)���x���r���P(gu��n)ϵ��

CK/CK#���r���̖����ַ��������̖�ڕr犵���������Ч����(sh��)��(j��)��̖�ڕr犵������غ��½��ض���Ч��

R����ʾ�x���

W����ʾ�����

A����ʾ��ַ��������е�ַ���е�ַ���K��ַ���K�M��ַ��

D����ʾ��(sh��)��(j��)��������(sh��)��(j��)�͔�(sh��)��(j��)�xͨ��̖��

AL������֮�g���g���r�g��ÿ�оƬ���g���r�g�Dz�ͬ�ģ��ԕr犵Ă���(sh��)���λ��

CL���x�Ĕ�(sh��)��(j��)�ă�(n��i)���惦��Ԫ����(sh��)��(j��)�����ĕr�g������(sh��)��(j��)�����ڣ�

CWL������(sh��)��(j��)�r���ӕr��Ҫ��CL�̵Ķࡣ

����Ďׂ������Д�(sh��)��һ�ӣ���һ�б�ʾ�r���̖���ڶ��б�ʾ������̖�������б�ʾ��(sh��)��(j��)��̖�������б�ʾ��һ���x/������l(f��)����ĕr�g�g����r�������б�ʾ�ڶ����x/������l(f��)����ĕr�g�g����r�������б�ʾ�������x/������l(f��)����ĕr�g�g����r��

��(n��i)��оƬ�IJ����r��ܶ࣬����ͨ�x��?q��)��r��ͻ�l(f��)�x��?q��)��r���x������x�r���x�r��ܼĴ����O(sh��)�ò����r��У��(zh��n)�r��ȵȣ��F(xi��n)�ڃH�H��ͻ�l(f��)���x���r��?y��n)����f����(n��i)���һ���Բ����r��

�o�g�����B�m(x��)ͻ�l(f��)�x�r�����1��ʾ��ͻ�l(f��)�L�Ȟ�4����(sh��)��(j��)���B�m(x��)ݔ���ģ�ÿ4���ֹ�(ji��)��Ҫһ��������CL��

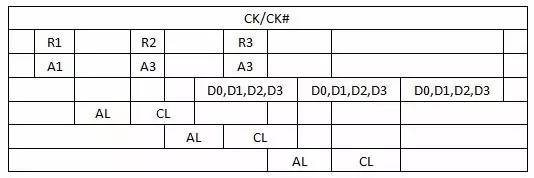

��1 �o�g����ͻ�l(f��)��(sh��)��(j��)�x����

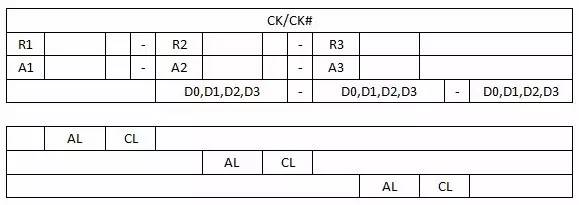

��һ���r������g����ͻ�l(f��)�x�������2��ʾ��ÿ�Ă���(sh��)��(j��)���g��һ���r����ڵ��g��������x�����Ѓɂ��r��g������(sh��)��(j��)��Ҳ�Ѓɂ��r��g����

��2 ��һ���r��g����ͻ�l(f��)��(sh��)��(j��)�x����

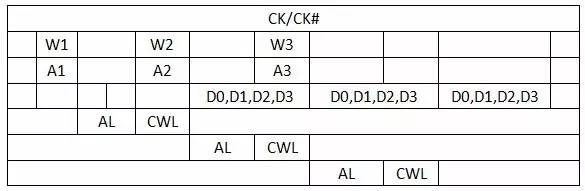

�o�g�����B�m(x��)ͻ�l(f��)���������3��ʾ��ͻ�l(f��)�L�Ȟ�4����(sh��)��(j��)�B�m(x��)ݔ�뵽��(n��i)���У�CWL�ĕr�g�g��һ����1~2���r����ڡ�

��3 �o�g����ͻ�l(f��)��(sh��)��(j��)������

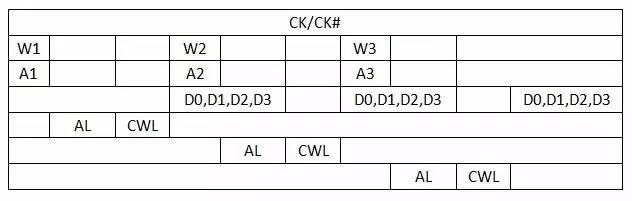

��һ���r��g����ͻ�l(f��)���������4��ʾ��ͬ�x����һ�ӣ�ÿ�Ă���(sh��)��(j��)���g��һ���r��g��������nj������Ѓɂ��r��g�����t��(sh��)��(j��)���gҲ�Ѓɂ��r��g����

��4 ��һ���r��g����ͻ�l(f��)��(sh��)��(j��)������

�����B�����a(b��)

1�����߾��Y(ji��)��(g��u)

T���߾���?f��)�Y(ji��)��(g��u)��D��ʾ��һ����(n��i)��������ϒ��d4����(n��i)��оƬ��

�D2 T���߾���?f��)?/div>

T�ͽY(ji��)��(g��u)���߾���ÿ�l���ı��L��ȣ����C��̖ͬ�r���_(d��)�K��оƬ��

2��Fly-By�߾��Y(ji��)��(g��u)

Fly-By���߾���?f��)䣬һ����(n��i)��������ϒ��d4����(n��i)��оƬ����D��ʾ��