|

發布時間: 2017-12-17 22:02

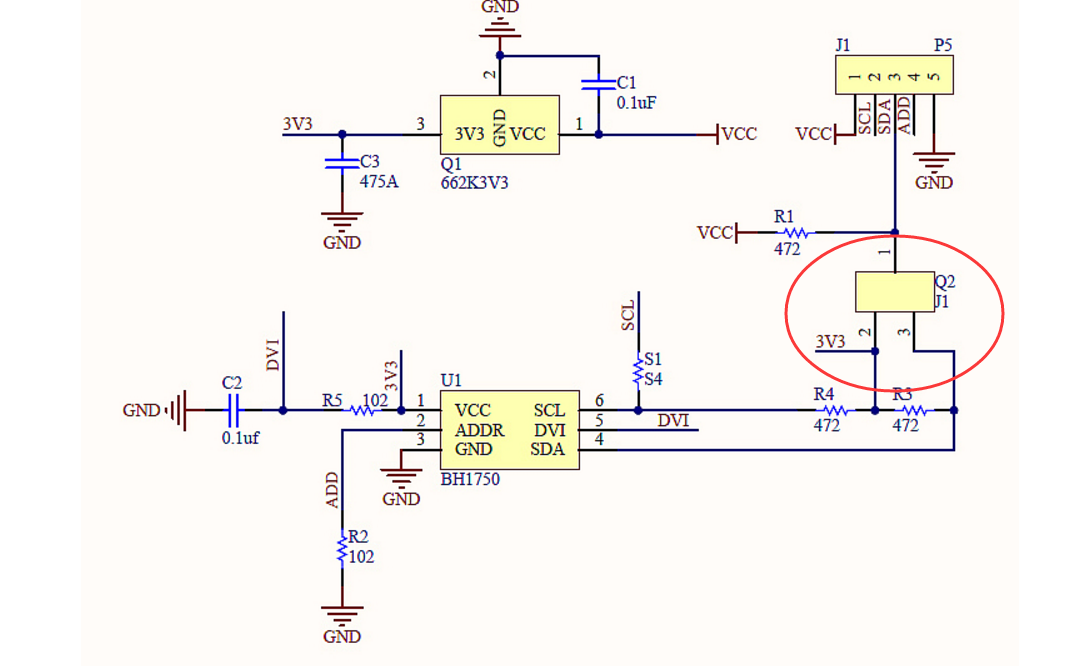

正文摘要:本帖最后由 1226199801 于 2017-12-17 22:10 編輯 Q2是n-mos管,封裝模式,有幾點不明白。兩張圖片,兩個mos管接法,那種對?我知道導通的情況要Ug>Us. 1、當1腳為5v時,3腳為什為3.3v? mos管導通不是1和3角應 ... |

| 門極(2腳)是3.3V, 漏極的電壓被下拉會逐漸將Us電壓下拉直到達到導通條件, VGS 超過閥值, 導通的情況是Ug>Us. |

angmall 發表于 2017-12-18 00:18 MOS-FET 管的漏極(1腳)基底二極管“低電壓”部分被下拉直到VGS 超過閥值,MOS-FET 管開始導通。 這一句不太理解,漏極的電壓被下拉會逐漸將Us電壓下拉直到達到導通條件? |

|

在電平轉換器的操作中要考慮下面的三種狀態: 1 沒有器件下拉總線線路。“低電壓”部分的總線線路通過上拉電阻R3 上拉至3.3V。 MOS-FET 管的門極(2腳)和源極(3腳)都是3.3V, 所以它的VGS 低于閥值電壓,MOS-FET 管不導通。這就允許“高電壓”部分的總線線路通過它的上拉電阻R1 拉到5V。 此時兩部分的總線線路都是高電平,只是電壓電平不同。 2 一個3.3V 器件下拉總線線路到低電平。MOS-FET 管的源極(3腳)也變成低電平,而門極(2腳)是3.3V。 VGS上升高于閥值,MOS-FET 管開始導通。然后“高電壓”部分的總線線路通過導通的MOS-FET管被3.3V 器件下拉到低電平。此時,兩部分的總線線路都是低電平,而且電壓電平相同。 3 一個5V 的器件下拉總線線路到低電平。MOS-FET 管的漏極(1腳)基底二極管“低電壓”部分被下拉直到VGS 超過閥值,MOS-FET 管開始導通。“低電壓”部分的總線線路通過導通的MOS-FET 管被5V 的器件進一步下拉到低電平。此時,兩部分的總線線路都是低電平,而且電壓電平相同。 這三種狀態顯示了邏輯電平在總線系統的兩個方向上傳輸,與驅動的部分無關。狀態1 執行了電平轉換功能。狀態2 和3 按照I2C 總線規范的要求在兩部分的總線線路之間實現“線與”的功能。 |