|

發布時間: 2018-5-16 11:40

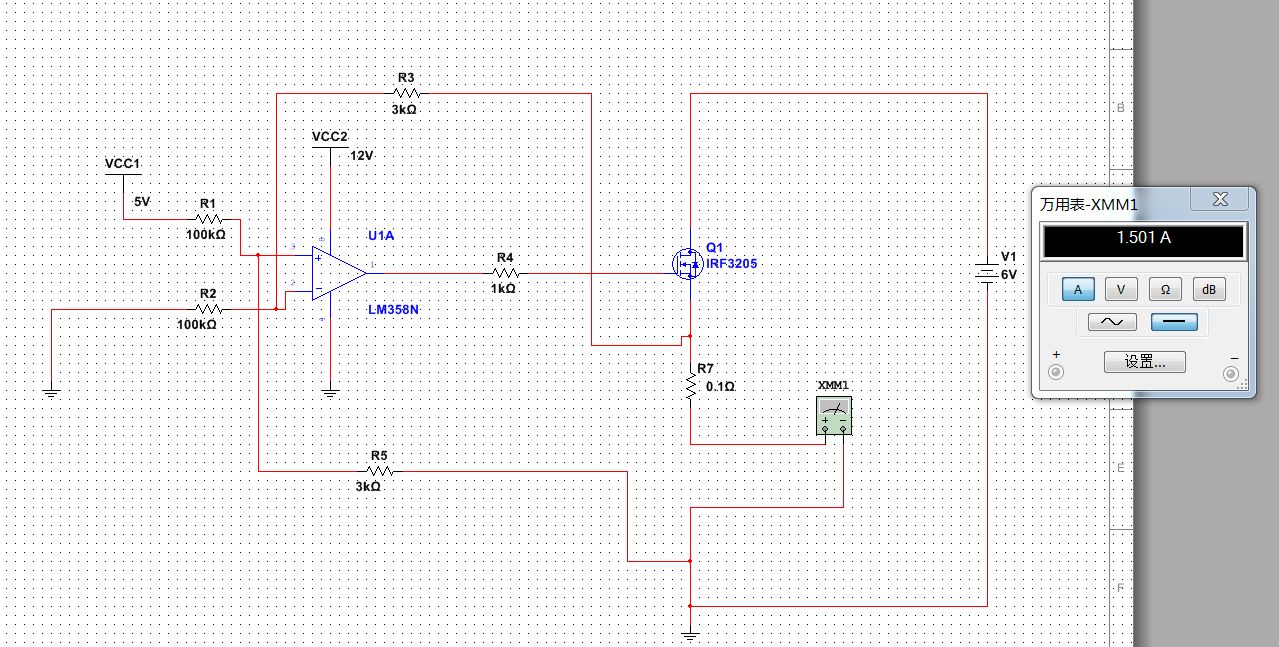

正文摘要:做一個恒流源電路,這個電路仿真能成功,但實際電路V1和VCC1會沖突,我一接入VCC1,提供電源的V1就會從CV模式變成CC模式并且只有零點幾伏,為什么會沖突啊,真的很急求各位不吝賜教,謝謝 |

yzwzfyz 發表于 2018-5-16 13:27 我的V1是直流電源提供的電壓源,應該可以滿足,而且調整這個V1值應該不影響電流值。另外這個電路VCC1在0~1V時正常工作,再進行加大時好像電路就會短路似的V1這個電壓源的輸入端會自動降低輸入電壓,我搞不清楚為什么不能在0~5V工作,我的目的就是VCC1在0~5V工作而采樣電壓值在0~0.17V左右,這樣就滿足了設計要求了 |

哈哈哈啥時候 發表于 2018-5-16 15:54 我電路就是按著這個仿真接的 |

LouisMa 發表于 2018-5-16 16:43 你的意思是v1不能直接接電壓源嗎 |

zhanghyg 發表于 2018-5-16 13:57 對,我想要的就是這個電壓值,可是V1這個電源端會自動降低電壓,使得我的電壓值變很低 |

| 電路圖呢? |