熱門: 51單片機(jī) | 24小時(shí)必答區(qū) | 單片機(jī)教程 | 單片機(jī)DIY制作 | STM32 | Cortex M3 | 模數(shù)電子 | 電子DIY制作 | 音響/功放 | 拆機(jī)樂園 | Arduino | 嵌入式OS | 程序設(shè)計(jì)

熱門: 51單片機(jī) | 24小時(shí)必答區(qū) | 單片機(jī)教程 | 單片機(jī)DIY制作 | STM32 | Cortex M3 | 模數(shù)電子 | 電子DIY制作 | 音響/功放 | 拆機(jī)樂園 | Arduino | 嵌入式OS | 程序設(shè)計(jì)

|

發(fā)布時(shí)間: 2018-12-28 13:22

正文摘要:求增量式正交旋轉(zhuǎn)編碼器的Verilog HDL鑒相代碼 需要使用大約13個(gè)增量式正交旋轉(zhuǎn)編碼器設(shè)定值,stm32的定時(shí)器不夠用,用中斷需要13個(gè)中斷,不太方便,stm32的引腳也不太好分配。想用EPM ... |

| mark幫頂下 |

if ((buffer0[3:3]==buffer1[0:0])&& (buffer0[2:2]==buffer1[1:1])) // D3和D0相同(D2和D1不同) if ((buffer0[3:3]==buffer1[0:0])&& (buffer0[2:2]!=buffer1[1:1])) // D3和D0相同(D2和D1不同) |

|

添加代碼后,排版格式亂了。再發(fā)一次。 wire A, B; reg [1:0] ABtimes; reg period; reg [3:0] shift_register, [3:0] buffer0, [3:0] buffer1; reg [15:0] Counter; always @(posedge A or posedge B or negedge A or negedge B) begin ABtimes = ABtimes +1; shift_register[3:0] = {shift_register[2:0], 1}; // 拼接1到最低位 if(ABtimes == 3) // 00-01-10-11 編碼器經(jīng)過了 A上升、B上升、A下降和B下降四步 begin if(period == 0) begin period = 1; // 第二個(gè)周期 buffer1 = shift_register; // 暫存第二個(gè)周期的移位寄存器值 end else begin period = 0; // 第一個(gè)周期 buffer0 = shift_register; // 暫存第一個(gè)周期的移位寄存器值 end end if((ABtimes == 3)&& (period == 1)) // 編碼器經(jīng)過四步和第二個(gè)周期 begin if ((buffer0[3:3]==buffer1[0:0])&& (buffer0[2:2]==buffer1[1:1])) // D3和D0相同(D2和D1不同) Counter <= Counter + 1; else Counter <= Counter - 1; shift_register <= 0; // 清零 end end |

|

謝謝 bucker 答復(fù)!沒有完全理解您的思路。簡單寫了如下代碼: |

|

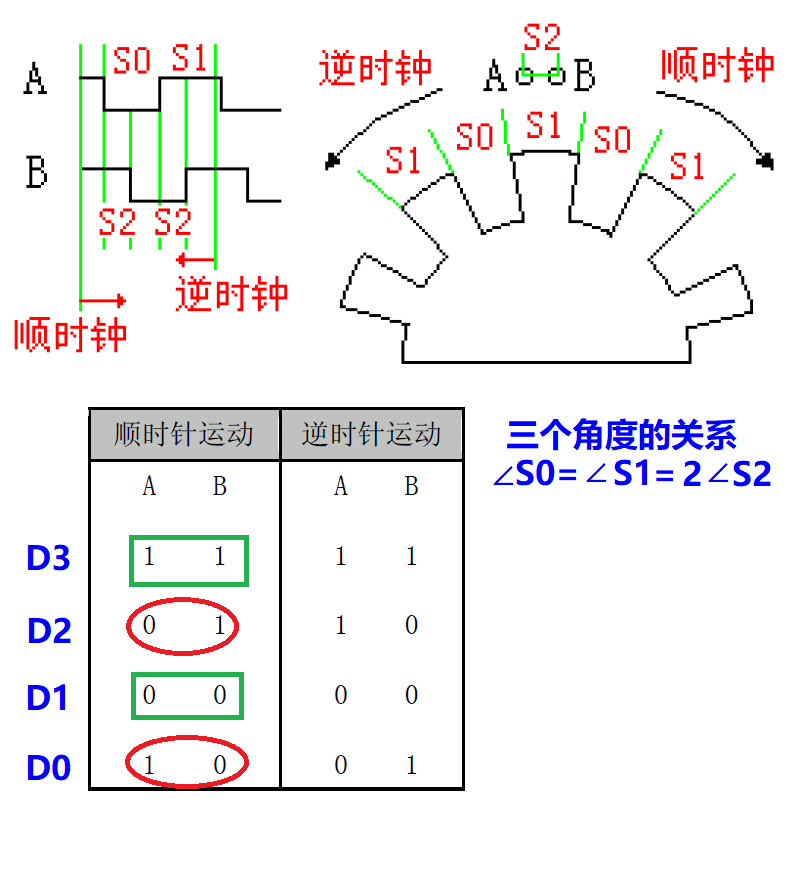

簡單的代碼比較好做,可能對于抖動(dòng)濾波做的不好,真正的消抖效果需要靠實(shí)際環(huán)境考核才能驗(yàn)證。 說個(gè)簡單方法,先設(shè)法獲取A、B相的上升沿和下降沿,每個(gè)沿都觸發(fā)同一個(gè)移位寄存器,取本次(D1、D0)及上次(D3、D2)的鎖存值共四位,即D3、D2、D1、D0。判斷方式為D3和D0相同(D2和D1不同)則正向,相反則為反向。這個(gè)方法你通過波形圖分析就可以推導(dǎo)出來。 |

|

本帖最后由 wxyz 于 2018-12-29 15:04 編輯 旋轉(zhuǎn)編碼器的A和B分別用5.1K電阻上拉到3.3V,再用0.1uF電容對地濾波消除抖動(dòng)和干擾。 借助單片機(jī)中斷模式的思路: 在上升邊沿觸發(fā)模式下,A和B進(jìn)行電平比較: 采用對A觸發(fā)的上升沿中斷模式,簡單的Verilog HDL如下:

根據(jù)以前單片機(jī)中斷模式的調(diào)試經(jīng)驗(yàn),編碼器有漏計(jì)數(shù)情況,計(jì)數(shù)不連續(xù)遞增或遞減,編碼器的抖動(dòng)干擾會(huì)造成漏計(jì)數(shù)情況。單片機(jī)可以采用延時(shí)消除抖動(dòng)干擾,但Verilog HDL中不知道如何解決? |

Powered by 單片機(jī)教程網(wǎng)