|

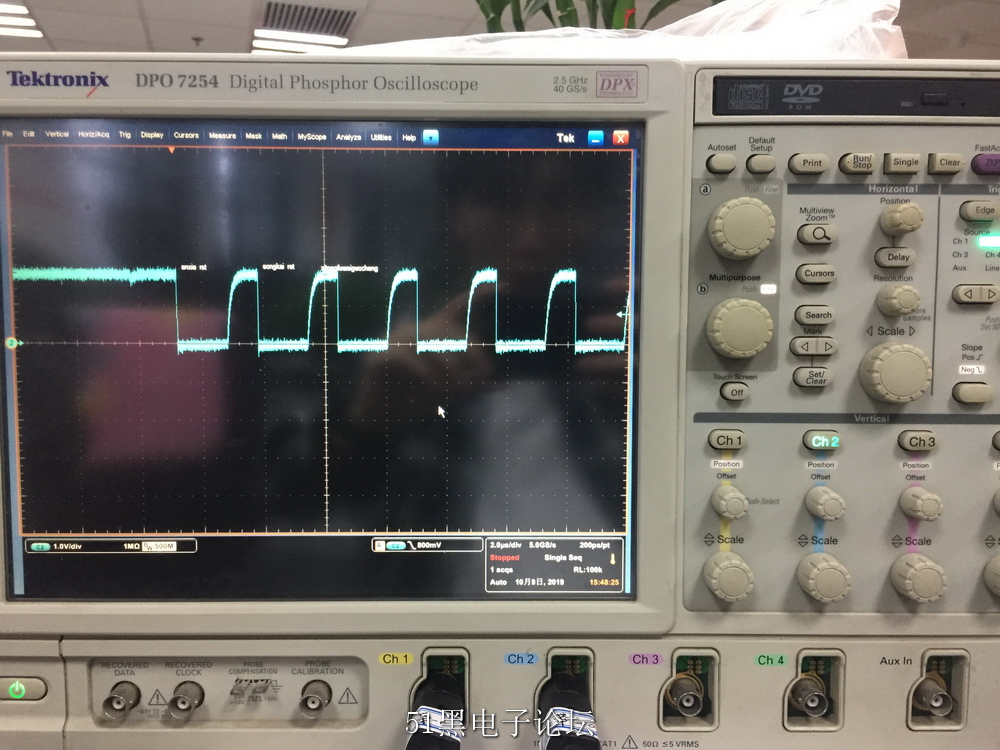

郭玲玉 發表于 2021-4-14 10:02 有沒有波形呢 |

|

想請教一下博主,我現在遇到相似的問題。 設置i2c的時鐘頻率為400kHz,但是實際出來的頻率只有360kHz左右,請問可能是什么原因呢 |

Hades_Wu 發表于 2019-11-6 15:40 我目前遇到下降時間不滿足規格書的情況,請問如何改善呢 |

| 請教一下,我遇到了i2c高速模式下信號下降時間過短,違反i2c標準中對于下降時間最小值的要求,想問一下樓主是否這個波形是否有同樣問題,該如何解決呢? |

| 好的,感謝! |

15133313 發表于 2019-10-11 12:22 在這個應用中不必糾結于波形是否理想,只要能完成正常通訊就可以了。大多數的應用IC的輸入端都具備整形電路,不易出錯。只有對脈沖寬度有嚴格要求的器件才需要認真對待上升時間和下降時間的問題。 |

| 10k是不是有點大了,我這個波形是上拉為4.7K量測出來的,如果換成10K,時間常數應該增大,上升沿更平緩了,這樣更不利于保證上升陡峭度啊 |

15133313 發表于 2019-10-10 15:07 不同品牌和型號的MCU的I/O口內部電路結構有所不同。以51為例,除P0口是內部晶體管截止時為高阻態,其它IO口都是弱上拉,也就是內部有較大阻值的上拉電阻。通常外接I2C器件時在總線上都要接10K上拉電阻以保證高電平上升陡峭度及近似等于VCC。 |

wulin 發表于 2019-10-10 08:57 晶體管截止時為高阻態,因此RC較大,1.8V通過上拉電阻對SCL線充電速度較為緩慢;晶體管導通瞬間,此時導通阻抗非常小,因此RC也非常小,所以下降速度非常快。不知道我理解的對嗎? |

| MCU準雙向I/O口高電平輸出內阻大,電平變化速率慢,低電平輸出內阻小,電平變化速率快。減小上拉電阻值有助于改善波形上升陡峭度。 |