|

發布時間: 2021-9-24 19:13

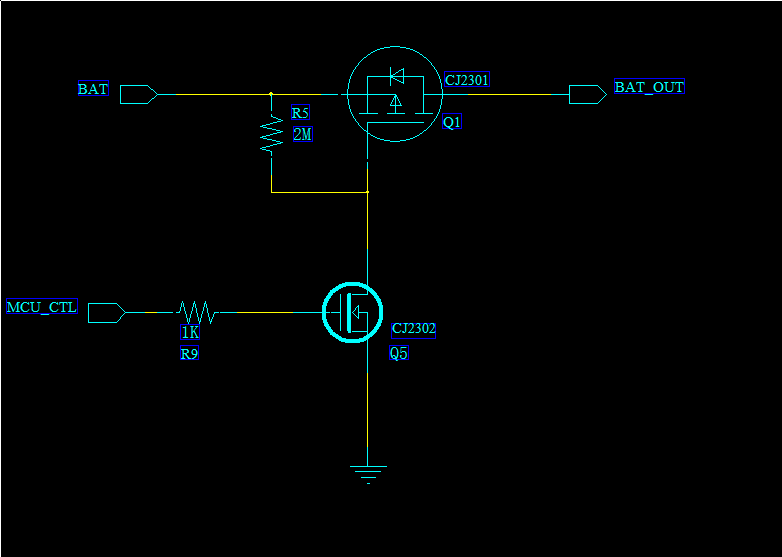

正文摘要:1.在MCU_CTL給高電平的時候,Q5、Q1導通,BAT_OUT輸出電池電壓3.7V,這個沒問題 2.在MCU_CTL給低電平的時候,Q5、Q1截止了,為什么BAT_OUT輸出還是有0.2V左右,是什么原因?如何改善這個bug 3.按照PMOS體二極 ... |

| 同意12樓,R5偏大,試試10k歐再測輸出電壓。 |

| 電路斷開,MOS處于高阻狀態,至于怎么會有0.2V電壓輸現,我認為是懸空電壓。 |

| R5的電阻給小一些大約在100K左右合適,2M的電阻太大,有壓降,導致Q1沒有完全關斷,所以有0.2V電壓 |

| 別去聽他們的,你這個個產品明顯是低功耗上面用的,他們說的情況在你這就不存在,你的電路是沒問題的,但我不明白你糾結這0.2V的電壓是什么原因,原因就是上面說的,由漏電流引起的,一般MOS管的漏電流進口的在幾十個na級別,國產的在百十個na級別,即使是低功耗環境,這種漏電流也是可以接受的吧,況且系統哪怕是處于休眠當中,也不止這點功耗了。 |

wufa1986 發表于 2021-9-27 10:40 我這里不用考慮溫度 |

mayouzhen2008 發表于 2021-9-26 09:13 為什么要加 說下你的考慮 |

munuc_w 發表于 2021-9-26 08:40 1.有很多人讓我把R5改成100K(那樣Q5就更耗電了,那改小干嘛) 2.也有人說在Q5的D和Q1的G極之間要加一個電阻 3.也有人說在Q5的極對GND之間要加一個下拉電阻 以上三點,你覺得有必要不 |

| 設計不合理,半導體都有漏電流,而且隨著溫度升高增大 |

| D和S之間漏電很小的MOS 大家有沒有推薦 |

mayouzhen2008 發表于 2021-9-26 09:13 這個電阻貌似不是必須要加,能說說你的思路嗎?為什么一定要加 |

munuc_w 發表于 2021-9-26 08:40 那如何避免呢 |

| Q5的D 和Q1的G之間加一個K級或者再小一點的電阻會更好,要不實際使用中會有問題 |

| 電路沒有問題,MOS做開關用,在截止時不是完全的斷開,是有一個電阻存在的,只是這個電阻很大,注意,是很大,不是完全斷開。當負載的等效阻抗很大時,就會有問題出現:分壓!!! |