|

| LDO可以,本身就沒什么震蕩。DCDC可能就不行了。 |

| LDO本身就是個線性降壓的,對干擾也沒多大的抗拒作用,如果信號不純凈,你說說入口地方是不是需要各加一個更好點呢? |

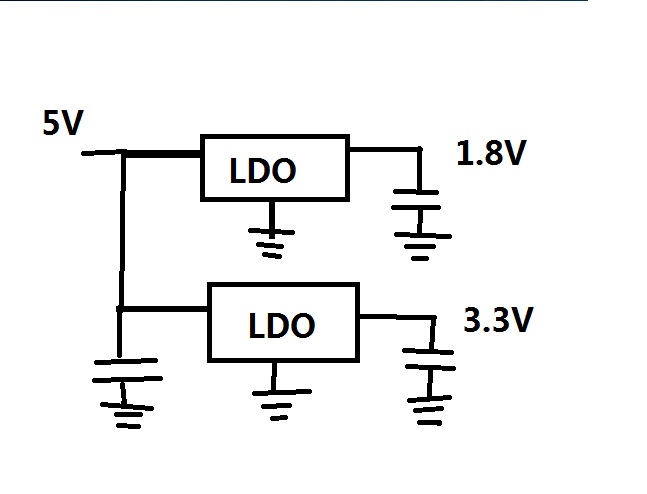

| 單從提高PSRR指標來看,如果輸入電壓紋波較大,那么可以將多個LDO串聯使用,從而提高PSRR指標,雖然噪聲的RMS值還是取決于單個LDO的性能,但是輸出電壓的紋波將比單用一個LDO要小。 |

| 行不行,看你的要求,要求不高的電路可以用一個,是否成本敏感,是否需要過EMC,需要這些綜合考慮 |

ly1972001 發表于 2021-10-18 15:57 一個好的電容美國產的2塊錢一個,量產產品上的話需要考慮成本,自己做的小玩意或者用國產的電容則不需要考慮。 |

| 兩個LDO在一起可以公用一個電容,如果距離較遠,還是每一個LDO配1uf+0.1uf效果最好了,差不了幾個錢,0603封裝的又不占地方。 |

| 最好是每個LDO的電源輸入管腳都有電容。共用電源的話,如果放在前級電源的輸出位置還好,像圖中所示只放在了最后一個LDO的位置,對第一個LDO來說,效果不好 |

ly1972001 發表于 2021-10-18 15:57 通常這是因為空間不夠吧,這東西不值錢 |

| 別扣,該用用,省不了幾個錢。理論上是不行的。輸入電容的正極和LDO的輸入要盡量靠近,它的負極要和LDO的GND腳盡量靠近。如果沒啥要求,那就隨便了。 |

| 當然可以,沒有什么不行的。 |

| 輸入可以共用一個電容 |

| 可以,問題不大 |

| 電容都有退耦半徑,電容值越大,半徑越大,如果兩個芯片挨得比較近,個人覺得也可以共用,問題不是很大。不過最好還是分開來比較合理一點 |