熱門: 51單片機(jī) | 24小時(shí)必答區(qū) | 單片機(jī)教程 | 單片機(jī)DIY制作 | STM32 | Cortex M3 | 模數(shù)電子 | 電子DIY制作 | 音響/功放 | 拆機(jī)樂園 | Arduino | 嵌入式OS | 程序設(shè)計(jì)

熱門: 51單片機(jī) | 24小時(shí)必答區(qū) | 單片機(jī)教程 | 單片機(jī)DIY制作 | STM32 | Cortex M3 | 模數(shù)電子 | 電子DIY制作 | 音響/功放 | 拆機(jī)樂園 | Arduino | 嵌入式OS | 程序設(shè)計(jì)

|

發(fā)布時(shí)間: 2022-10-31 18:28

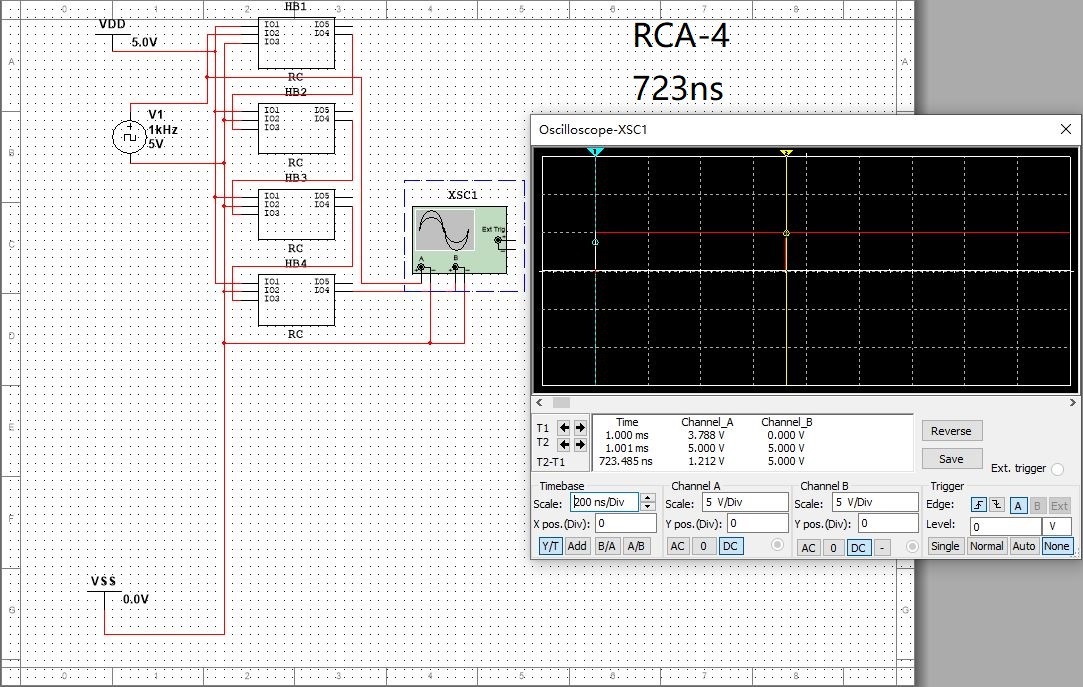

正文摘要:第一章:設(shè)計(jì) 經(jīng)過學(xué)習(xí),行波進(jìn)位加法器RCA和超前進(jìn)位加法器CLA后。 自己動(dòng)手設(shè)計(jì)一個(gè)八位二進(jìn)制加法器。 ... |

Ele_insect 發(fā)表于 2022-11-16 09:34 其實(shí)GPU的流處理器數(shù)量更多!我的2070顯卡,就有2300個(gè)流處理器,也就是說(shuō),一個(gè)顯卡里面可能會(huì)使用近萬(wàn)個(gè)加法器! |

Ele_insect 發(fā)表于 2022-11-7 10:44 我自己覺得,這個(gè)加法器挺好的,能加快ALU的計(jì)算速度,提升CPU性能!  |

風(fēng)吹過后 發(fā)表于 2022-11-6 21:01 在微處理器芯片中,加法器是進(jìn)行數(shù)字信號(hào)處理的核心,同時(shí)也是微處理器中進(jìn)行數(shù)據(jù)處理的關(guān)鍵部件。 加法器完成一次操作的周期,基本上決定了微處理器的主頻。加法器的速度和面積優(yōu)化對(duì)于整個(gè)CPU的性能來(lái)說(shuō)是非常重要的。為了加快加法器的執(zhí)行速度,減少加法器的面積,有必要對(duì)加法器的算法、結(jié)構(gòu)及電路的具體實(shí)現(xiàn)做深入的研究。 我現(xiàn)在就搞了一個(gè)晶體管數(shù)量少的,速度快的,S分段C覆蓋并行加法器。 |

|

加法器的速度翻倍,ALU的計(jì)算能力會(huì)不會(huì)翻倍?cpu的性能,能不能翻倍? 51單片機(jī)換上這個(gè)加法器,性能會(huì)翻倍嗎?  |

yzwzfyz 發(fā)表于 2022-11-2 10:22 關(guān)于第一點(diǎn):最長(zhǎng)路徑指的是門延遲最多的一條線,線延遲相對(duì)于門延遲要小很多! 關(guān)于第三點(diǎn):不是8位對(duì)比的,8種情況。而是256*256=65536種情況(0到255分別加0到255),窮舉法測(cè)量,那就太多了,只能靠FPGA寫出加法器,再通過程序進(jìn)行全面的測(cè)量時(shí)序了。 大致同意您的意見! 我現(xiàn)在應(yīng)該買一塊FPGA,然后寫入我的設(shè)計(jì),之后用程序測(cè)量嗎?(FPGA測(cè)出的數(shù)據(jù)符合現(xiàn)實(shí)嗎?) 這個(gè)好學(xué)嗎?我就只用這一部分的東西,比較簡(jiǎn)單的! |

|

【加法器里面有,最長(zhǎng)路徑的,這個(gè)是最慢的。只用測(cè)量這個(gè)的速度,就好了!】 1、電速如光速,最長(zhǎng)路徑能比其它路徑多幾何哉!如何證明它是最慢的。 2、即使是最短的路徑,如果其分布電容、電感大,也可能響應(yīng)是最慢的。 3、如果不做對(duì)比,你如何知道8個(gè)位,哪個(gè)位最慢。況且數(shù)字不同,結(jié)果不同,不可能每次都是某位最慢。 比如,第3位,本次計(jì)算結(jié)果與上次不相同,而其它位本次計(jì)算結(jié)果與上次相同(即沒有延時(shí))!你能說(shuō)第3位最慢嗎? 4、許多變化還與鄰近的線路相關(guān),當(dāng)相鄰的線路穩(wěn)定時(shí),它不受干擾,而相鄰線路波動(dòng)時(shí),它就被干擾了。也即不同的數(shù)據(jù)相加,某位受到的干擾不同,延時(shí)也會(huì)不同。要認(rèn)定哪一位延時(shí)最多,是需要做整體數(shù)據(jù)驗(yàn)證的。不是你所想像地線路最長(zhǎng)。 |

Y_G_G 發(fā)表于 2022-11-1 19:24 機(jī)械。。。加法器功能,我已經(jīng)實(shí)現(xiàn)了。就缺最大延遲的測(cè)量了 |

Ele_insect 發(fā)表于 2022-11-1 17:04 你的專業(yè)是什么? FPGA還是嵌入式? |

Y_G_G 發(fā)表于 2022-11-1 15:14 我要做:一個(gè)拓?fù)浣Y(jié)構(gòu)和RCA一樣簡(jiǎn)單的,晶體管數(shù)量少的,速度比CLA快的加法器。 只需要簡(jiǎn)單的并聯(lián),就能拼出32位,拼出64位的加法器,速度還要快過CLA【超前進(jìn)位加法器】 |

|

你是做什么的?或者是說(shuō)你要做什么?為什么對(duì)"加法器速度"如此的執(zhí)著? 我個(gè)人認(rèn)為,這種古怪的問題是由于新手剛剛學(xué)習(xí)某些專業(yè),基礎(chǔ)還沒有打好,然后就自己想當(dāng)然的去覺得應(yīng)該這么這么的,然后就冒出一個(gè)問題來(lái)了 你仿真的時(shí)候,用的是理想元件,實(shí)際PCB的時(shí)候卻并不是理想元件,誤差肯定有的了 而且,你不會(huì)告訴我說(shuō),你用示波器不會(huì)看時(shí)間差吧? 而且,你這一堆操作的意義何在?是要看加法器的延時(shí)?還是說(shuō)問題,本來(lái)就不是這個(gè)問題,"加法器延時(shí)"只是你自己覺得應(yīng)該要看的? |

1951387254 發(fā)表于 2022-11-1 14:23 【取最不利的結(jié)果作為最終結(jié)果。】 加法器里面有,最長(zhǎng)路徑的,這個(gè)是最慢的。只用測(cè)量這個(gè)的速度,就好了! |

| 速度 = 距離/時(shí)間。 對(duì)于命題而言實(shí)際上是時(shí)間長(zhǎng)短,而不存在距。 時(shí)間的長(zhǎng)短認(rèn)定,必須有起點(diǎn)和終點(diǎn)。 1、時(shí)間起始點(diǎn)在何處? 2、時(shí)間終止點(diǎn)在何處? 方案: 起點(diǎn)認(rèn)定,需要你加一個(gè)信號(hào),即認(rèn)為輸入數(shù)據(jù)穩(wěn)定了,被確認(rèn)的信號(hào),建議用A、B栓鎖信號(hào)認(rèn)定。當(dāng)A、B全部被確定后(栓鎖),作為開始信號(hào)。 終止認(rèn)定:應(yīng)當(dāng)是計(jì)算結(jié)果正確且穩(wěn)定后,才能認(rèn)定的終止。 應(yīng)該取8位輸出全部穩(wěn)定(不再變化)的時(shí)刻作為終止點(diǎn)。這需要你對(duì)各種輸入計(jì)算結(jié)果進(jìn)行對(duì)比。取最不利的結(jié)果作為最終結(jié)果。 |

yzwzfyz 發(fā)表于 2022-11-1 11:12 【對(duì)各種輸入計(jì)算結(jié)果進(jìn)行對(duì)比】8位+8位,有256*256種加法,速度是不相同的。 但是一般可以分析出最大路徑的那個(gè),就能代表其他了。 我現(xiàn)在是不會(huì)用示波器,也沒有一個(gè)精度很高的示波器。 |

wufa1986 發(fā)表于 2022-11-1 07:54 兩個(gè)仿真軟件和PCB,都證明了,加法器的功能是沒有問題的。 仿真軟件的虛擬示波器,測(cè)試出的數(shù)據(jù),也呈現(xiàn)出與理論相同的增長(zhǎng)比,就是不知道怎么更加精確的測(cè)量出加法器速度。 |

Hephaestus 發(fā)表于 2022-10-31 21:48 我不認(rèn)識(shí)電子專業(yè)的人。 做pcb是為了證明實(shí)際可以實(shí)現(xiàn)加法器功能,想用示波器測(cè)加法器的速度。 |

|

不太懂,據(jù)我所知,單純的Verilog好像看不出來(lái)實(shí)際延時(shí),要結(jié)合用的器件才行,直接用電路搭的外部因素很多,和FPGA內(nèi)部也不一樣,設(shè)計(jì)時(shí)應(yīng)該是讓一次數(shù)據(jù)處理的時(shí)間在一個(gè)時(shí)鐘周期內(nèi)完成,用流水線提高時(shí)鐘頻率,所有的運(yùn)算都可以砍成幾個(gè)步驟。 這么看來(lái),只要提高時(shí)鐘頻率直到輸出錯(cuò)誤,應(yīng)該就可以算出延時(shí)。 |

|

速度 = 距離/時(shí)間。 對(duì)于命題而言實(shí)際上是時(shí)間長(zhǎng)短,而不存在距。 時(shí)間的長(zhǎng)短認(rèn)定,必須有起點(diǎn)和終點(diǎn)。 1、時(shí)間起始點(diǎn)在何處? 2、時(shí)間終止點(diǎn)在何處? 方案: 起點(diǎn)認(rèn)定,需要你加一個(gè)信號(hào),即認(rèn)為輸入數(shù)據(jù)穩(wěn)定了,被確認(rèn)的信號(hào),建議用A、B栓鎖信號(hào)認(rèn)定。當(dāng)A、B全部被確定后(栓鎖),作為開始信號(hào)。 終止認(rèn)定:應(yīng)當(dāng)是計(jì)算結(jié)果正確且穩(wěn)定后,才能認(rèn)定的終止。 應(yīng)該取8位輸出全部穩(wěn)定(不再變化)的時(shí)刻作為終止點(diǎn)。這需要你對(duì)各種輸入計(jì)算結(jié)果進(jìn)行對(duì)比。取最不利的結(jié)果作為最終結(jié)果。 |

| 你這只是理論而已 |

|

我覺得你的做法真沒什么實(shí)際意義,跟74系列小規(guī)模集成電路搭建CPU一樣無(wú)聊。 弄一個(gè)FPGA開發(fā)板,就算你不會(huì)Verilog也沒問題,F(xiàn)PGA設(shè)計(jì)軟件都是支持原理圖的,也就是說(shuō)你在仿真軟件里面畫的那些圖,在FPGA軟件里面一樣可以畫,下載后,一樣可以用萬(wàn)用表來(lái)驗(yàn)證。 我覺得你實(shí)在是跑偏了,周圍就沒有懂點(diǎn)的人告訴你么?大學(xué)里面思路寬廣的人太多了,你是畢業(yè)了吧? |

|

雖然通過protues7.8和multisim14的虛擬示波器測(cè)試了加法器速度。 但還是做出來(lái)pcb板,用真實(shí)的示波器測(cè)延遲了,但用的不好!也不會(huì)讀數(shù)! 我接下來(lái)該怎么辦(準(zhǔn)確測(cè)量加法器速度的快慢)? 是使用Verilog時(shí)序仿真,還是怎么搞? 希望大家給點(diǎn)建議!謝謝了! |

Powered by 單片機(jī)教程網(wǎng)