|

發(fā)布時間: 2024-1-22 16:03

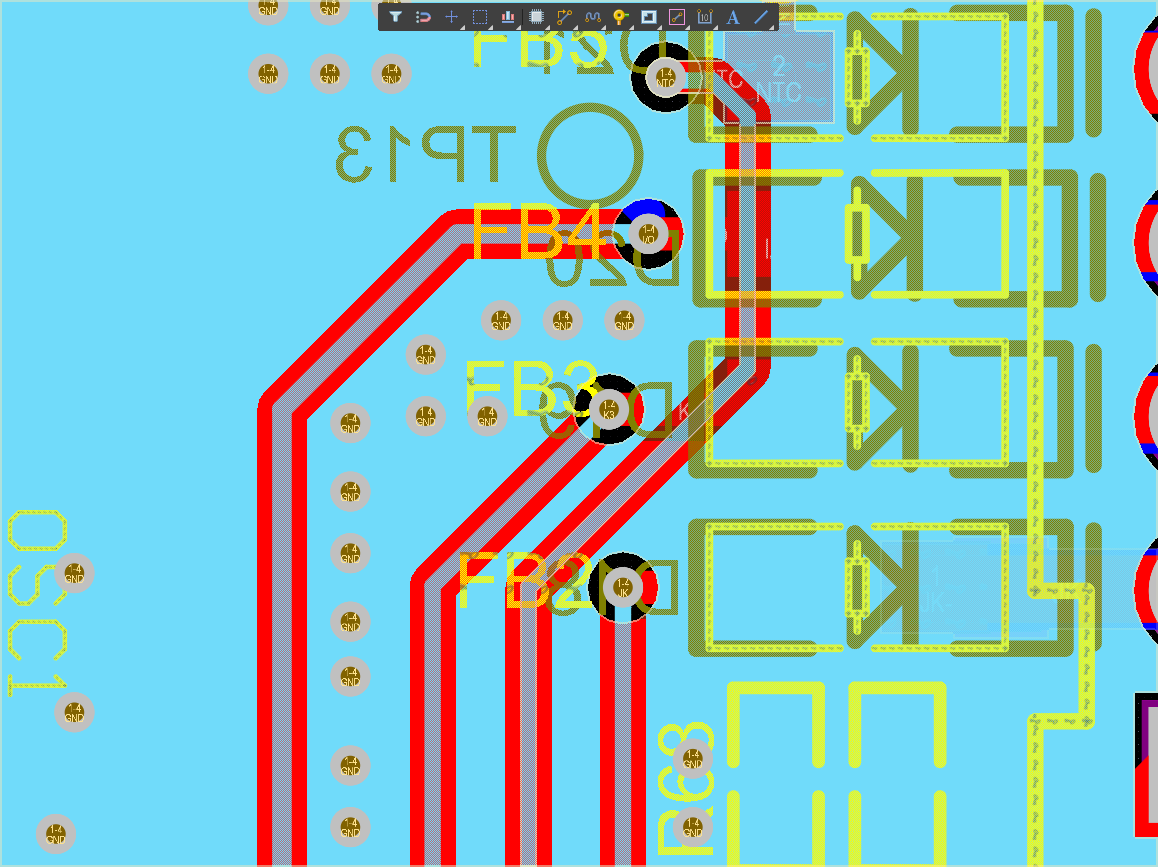

正文摘要:PCB layout中會遇到單總線,串口線TX、RX,IIC的時鐘、數(shù)據(jù)線并排走的情況,為了防止互相干擾。有沒有之間間隔拉寬一點,并且灌入銅皮,做所謂的包地處理。這個是有必要的嗎?之前的工作經(jīng)驗,有看到一個老工程師都 ... |

| 應該是類似屏蔽的作用 |

| 有必要,雖然你的通訊速率不高,但是如果系統(tǒng)采用的是高頻開關電源,還是有必要防止高頻開關電源的噪聲串入,如果有條件的話,增加包地處理是好的。它的機理就是就近增加地平面,相當于信號線到地增加一個寄生電容,使高頻噪聲就近耦合到地,濾除掉 |

| 如果是在RF干擾大的情況IIC包地還是有改善的。或者適當降低上拉電阻 |

| 包地應該是吸收掉信號線的空間輻射吧!!!! |

| 并不是一定要,之所以形成包地,是因為布線到最后一般就整塊地覆銅 |

QWE4562012 發(fā)表于 2024-1-30 18:07 一般信號速率10M以上才考慮竄擾問題,就是信號上升沿小于100ns |

| UART,IIC速率不高,沒必要包地,如果擔心竄擾問題可以把信號線之間的距離拉遠一點 |

QWE4562012 發(fā)表于 2024-1-30 18:07 速度除頻率是波長,你的長度連波長的鼻涕都達不到談什么? |

Hephaestus 發(fā)表于 2024-1-22 20:41 你說的速度低是什么概念?是頻率還是速率分別少于多少呢 |

| 頻率高,會使寄生電容發(fā)生作用,包地起這個作用。頻率低就毫無意義了。 |

| TX、RX,IIC速度太慢了,完全沒有包地的必要。 |

Powered by 單片機教程網(wǎng)