|

發布時間: 2024-2-3 11:28

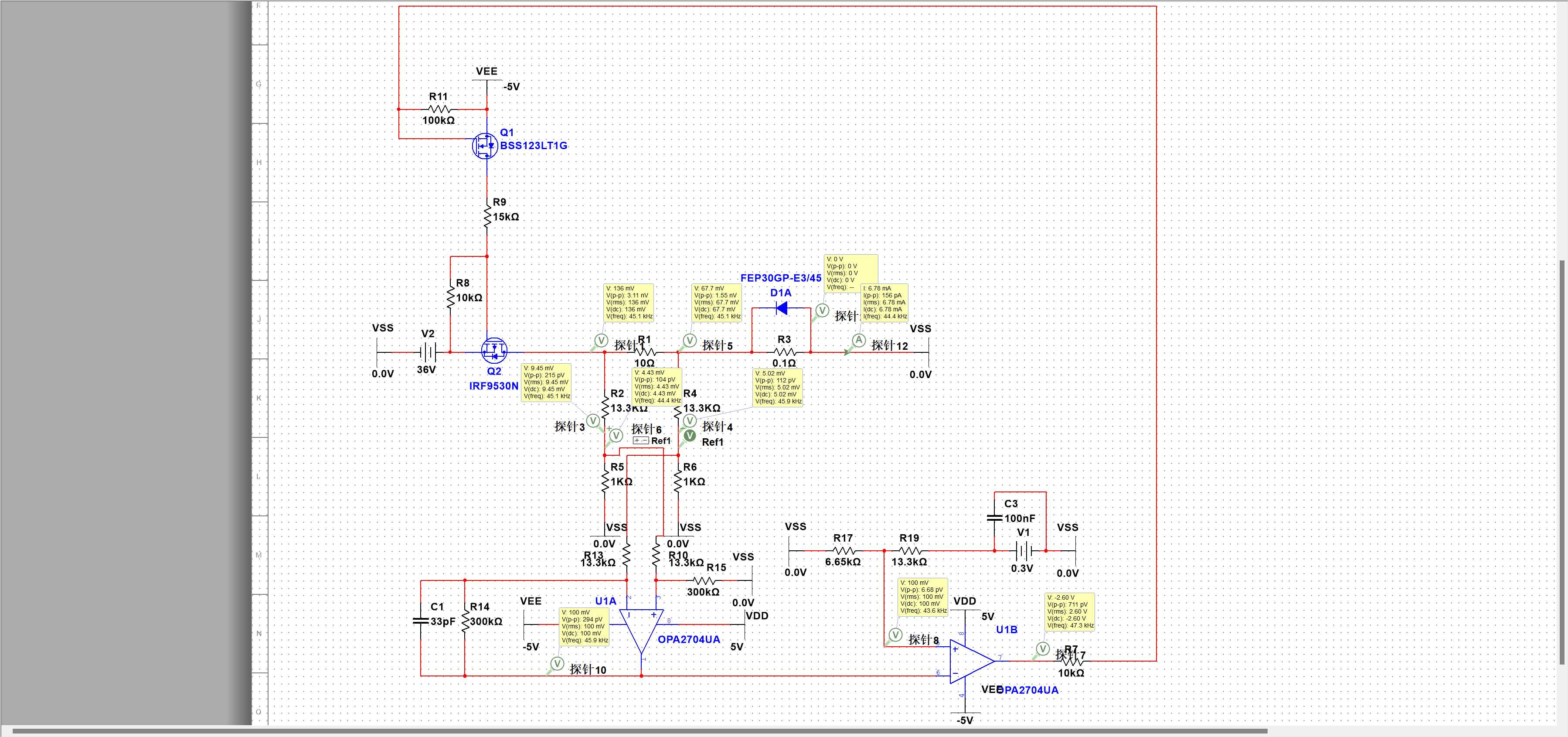

正文摘要:如圖所示, R3是負載,恒流值0.1MA-100MA,V1實際是一路16位DAC(0-5V). 電路原理是高邊采樣電阻,分壓后進入運放做差分放大,然后輸出至下一級運放與DAC分壓后做比較 然后輸出控制NMOS Q1, Q1控制Pmos Q2進入線性 ... |

|

1、Q2不要,運放直接控制Q1恒流,少一級反應更快。 2、R7太大,改成330歐姆。 3、R17要并聯一個電容1uf穩壓。C1不要,影響反應速度。 V1的紋波一定要小,如果是pwm做的DA很容易出問題。 |