由于一直在忙,都沒有空來解決,然后發現網上也有遇到這問題,但是似乎沒有解決方法,并且更多的提示是在于破解沒有破解好。后來自己琢磨,發現問題并不在modelsim的破解。

解決方案為:將庫uinsims文件夾中的verilog文件分批次編譯

下面是我的實例,xilinx庫為隨便ISE拷過來的unisims庫,第一個文件是AFIFO36_INTERNAL.v,最后一個文件是ZHOLD_DELAY.v,如果在編譯庫的時候,一次性選擇所有文件,編譯就會出現上圖的錯誤。但是如果將unisims庫中文件分幾次編譯就不會出錯,感覺原因是由于計算機配置比較低造成的。

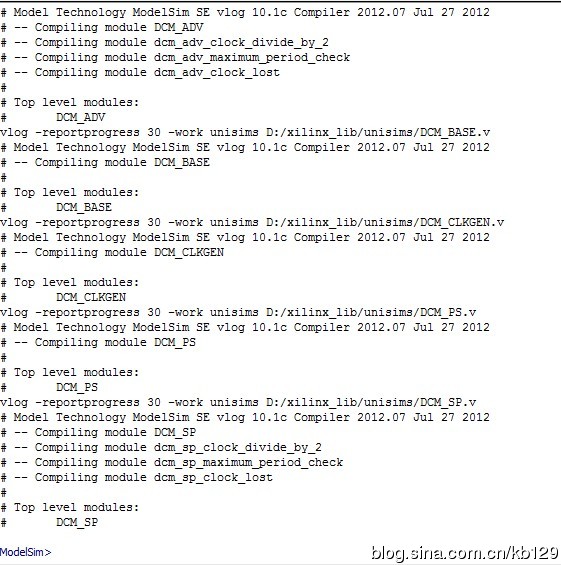

編譯后的結果是:

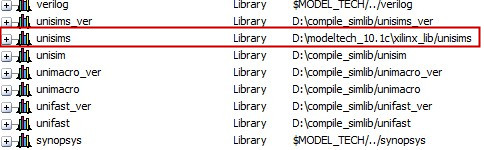

這樣編譯就沒有問題,但是此時庫并不能使用,點擊modelsim的library會發現unisims后面的顯示和其他的不一樣。

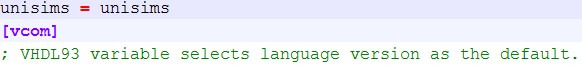

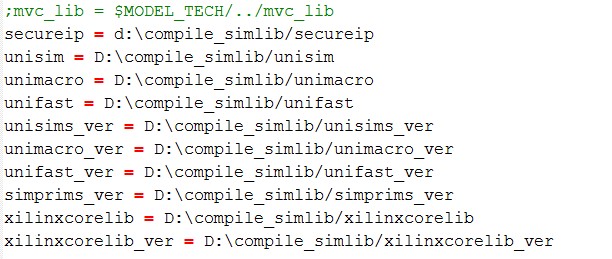

對于這種情況,就需要修改modelsim安裝路徑下的modelsim.ini文件。去掉modelsim.ini文件的只讀屬性,將modelsim.ini文件默認情況下的:

修改為:

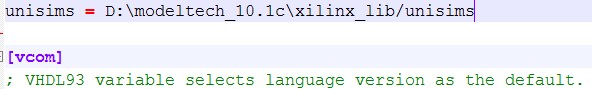

其中=后面的為在modelsim中新建庫unisims的存放路徑。保存后,再次打開modelsim。

出現這樣的結果,就表明庫已經編譯成功。

上面編譯庫的方法,對于altera的庫非常適用,但是對于xilinx的庫就有些不太方便。在xilinx的ISE或是vivado中都可以編譯庫,到時候只要將編譯好的文件夾的路徑在modelsim.ini文件中修改。

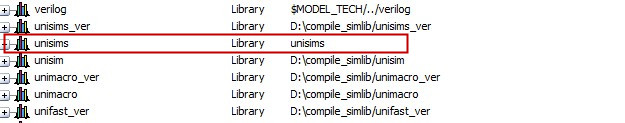

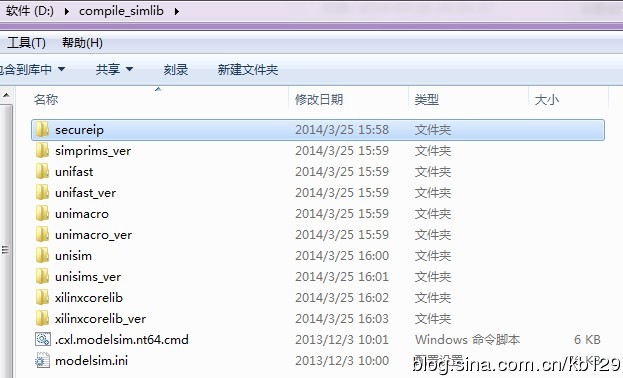

例如:在其他電腦中編譯好了xilinx的庫文件,并放在文件夾compile_simlib中,如圖

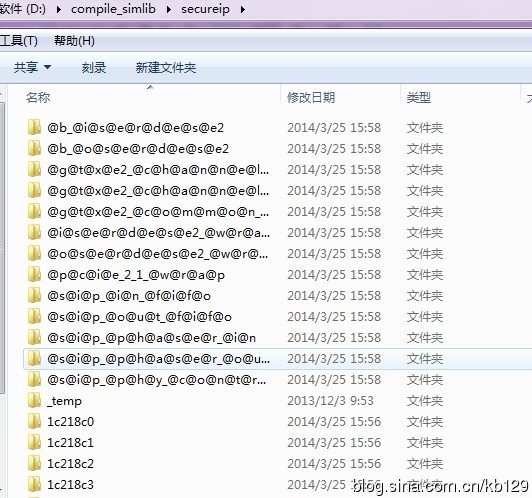

如何區別這是否是編譯好的,主要是打開文件夾,如果文件夾里面有很多@,那么就是編譯好的庫,如果是verilog/vhdl文件,則是沒有編譯的,如圖:

可以看出我只是將文件夾compile_simlib放在D盤下,然后修改文件modelsim.ini,修改為:

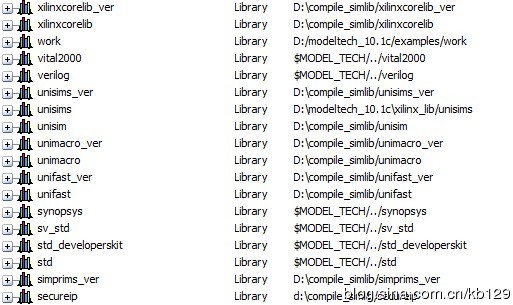

然后打開modelsim,點擊library,發現多了上面的庫文件了,如圖:

這樣就可以不安裝ISE或是vivado,就可以使用modelsim來仿真xilinx的IP core了