這是我之前問別人的一個問題,。

其實答案很明顯,讓FPGA和HPS同時控制某一個輸入或輸出是不可能的事情。就是我太笨,不知道怎么去想這個問題,所以還是試了一下。

。。。。

其實稍微不是我這樣反應遲鈍的也該發現問題了,不過我這笨笨還是要分析綜合后才意識到問題的。。。

我是傻×。。。不過還是寫一下,免得哪天又問自己這個傻問題。

問題是這么來的:

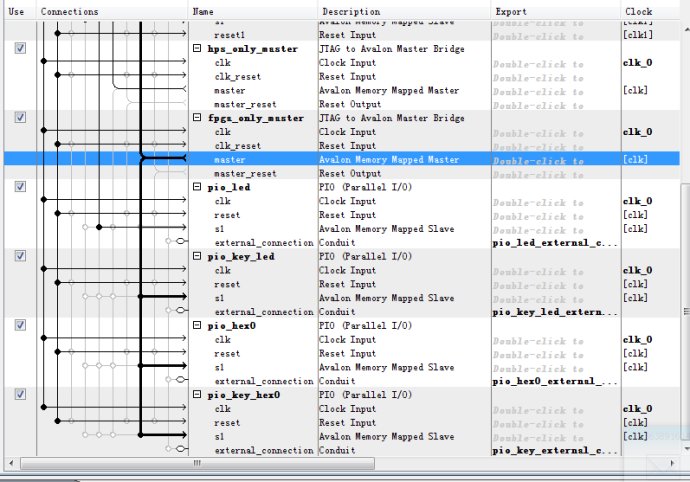

de1-soc上FPGA和HPS可以通信,FPGA的外設可以由FPGA自己控制,而HPS也可以通過AXI bridge控制FPGA的外設。由于FPGA的工程文件在Quartus中編譯,而HPS中的可執行文件是由.c文件生成的,并且在在下載時也是Quartus工程文件下載到FPGA,可執行文件在HPS中運行。所以我覺得這兩個過程基本上分開,應該不會相互干擾。那么如果讓FPGA和HPS同時控制某一個輸入或輸出會不會出現矛盾?比如,FPGA的外設LED燈,假設在FPGA中用撥碼開關控制,而在HPS中又讓它以另一種固定方式亮燈,那么結果會變成怎樣?

。。。。

其實稍微不是我這樣反應遲鈍的也該發現問題了,不過我這笨笨還是要分析綜合后才意識到問題的。。。

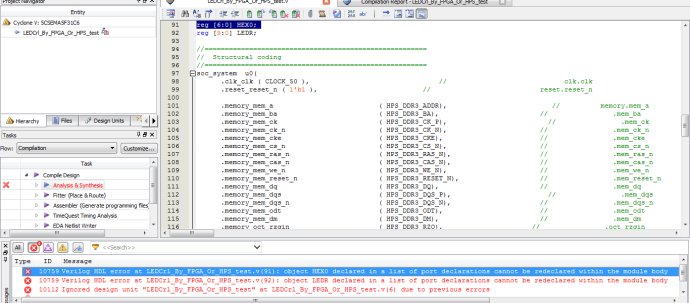

添加相應文件后分析和綜合出錯:(類似這樣的)object HEX0 declared in a list of port declarations cannot be redeclared within the module body

如圖

我是笨蛋。其實還是因為對FPGA和HPS之間的通信不理解。

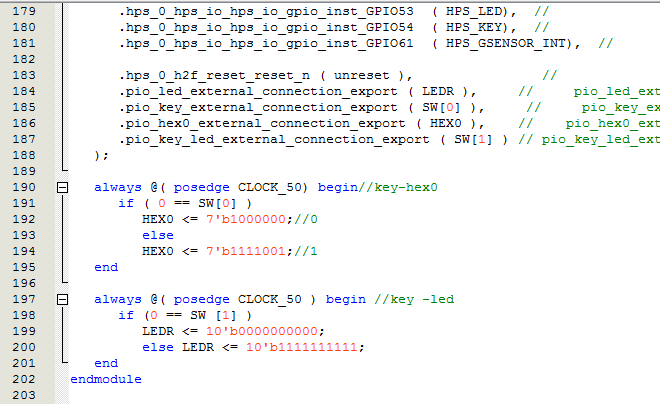

那個叫做Qsys的東西,生成的文件中有一個模塊module,這個模塊就像我們一般自己寫的模塊那樣。在FPGA的工程中,我們在頂層文件中實例化這個模塊,從而讓HPS通過AXI bridge控制FPGA的外設。而在實例化這個模塊時,LEDR作為輸出,相當于已經確定LED的輸出由誰決定,此時再在FPGA中寫LED由誰決定輸出就會報錯。

唉,兩種方式控制一個東西的狀態,肯定會打架的嘛。我個傻×。。。

同時可以看到,同樣傳到Qsys生成的系統中的KEY[0]和KEY[1],因為是作為輸入就沒有報錯。而同樣作為輸出的HEX0,也報了同樣的錯誤。

我是傻×。。。。居然問這種問題。。。

其實以前寫verilog文件時編譯出錯時就犯過兩個地方對同一個輸出賦值的情況,也是這樣子報錯的。。。額。。。我錯了。。。居然在同一個地方跌倒了。。。