2、打字好累,上傳更累;

3、之后我會發布PDF版,有心的同學可以下載學習。

之前有一點漏說明了,先補充上

***************************************************************還有一個模塊時鐘源:MODOSC,產生MODCLK時鐘源信號,一般只為閃存控制模塊和ADC12模塊提供服務。

該模塊不被使用時自動關閉,任何模塊對該時鐘源提出使用要求時,MODOSC無需被使能即可響應該請求。430F5529中MODCLK為5MHZ。

***************************************************************

MSP430F5529有多個時鐘源,而且很多模塊其時鐘源都是可以自由選擇的。此外,由于一般情況下,系統功耗是和工作頻率成正比的,因此有些時候通過選擇較低頻率的時鐘源,在滿足正常工作條件下,是可以有效降低功耗的。雖然函數庫HAL_UCS.c/h,有完整的各個控制函數,但我覺得對于這一章還是對寄存器直接操作比較簡單,因為函數太短、太多了。

3.1統一時鐘系統(UCS)的簡介

Unified Clock System,UCS。合理的配置時鐘,可以達到平衡系統且降低功耗的目的。

MSPF5529時鐘系統包含5個時鐘源:

①LFXT1 外部低頻振蕩源,32.768KHZ,可以用作FLL的參照源;

②XT2 外部高頻振蕩源,4MHZ;

③VLO (Internal very low)內部低耗低頻振蕩源,典型為10KHZ,精度一般;

④REFO 內部低頻參照源,32.768KHZ,常被用作鎖相環FLL的基準頻率,精度很高,不使用時不消耗電源,其設置往往要參考LPM模式的的設置;

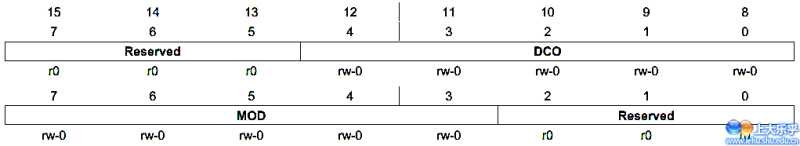

⑤DCO (Internal digitally-controlled)內部數字控制振蕩源,一般通過FLL來設置;(很有用,很重要,之后會詳細講)

通常使用3種時鐘信號,它們都來自于上述5個信號源:

①ACLK (Auxiliary clock)輔助時鐘,其時鐘源可由軟件控制從XT1、REFOC、VLO、DCO、DCOCLKDIV、XT2里面選取。其中DCOCLKDIV是由DCO經1、2、4、8、16或者32分頻得到。注意,ACLK同樣可以再次被1、2、4、8、16或者32分頻。

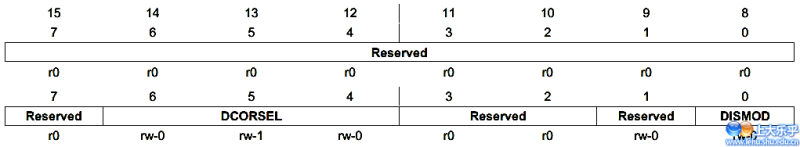

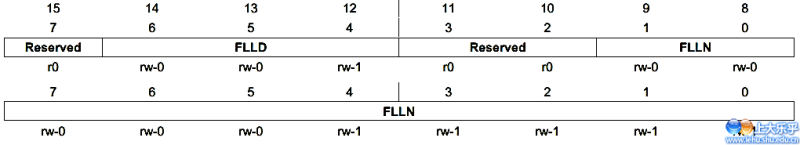

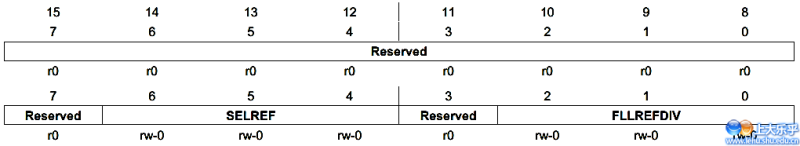

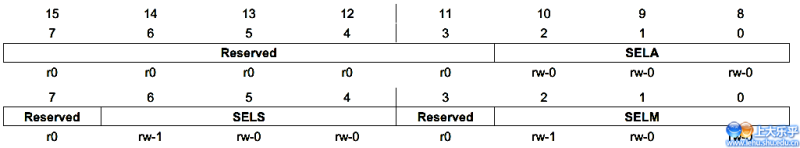

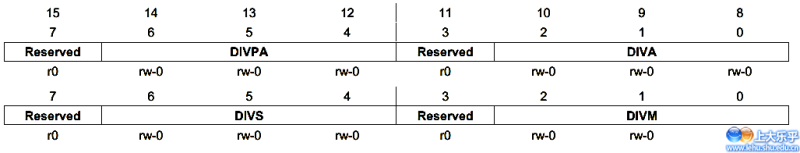

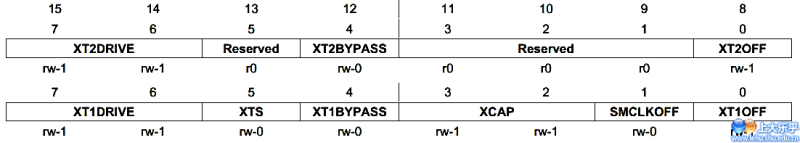

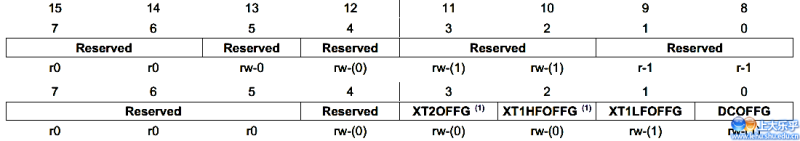

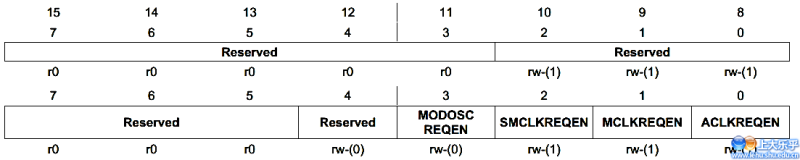

/* UCSCTL0 Control Bits */ //#define RESERVED (0x0001u) /* RESERVED */ //#define RESERVED (0x0002u) /* RESERVED */ //#define RESERVED (0x0004u) /* RESERVED */ #define MOD0 (0x0008u) /* Modulation Bit Counter Bit : 0 */ #define MOD1 (0x0010u) /* Modulation Bit Counter Bit : 1 */ #define MOD2 (0x0020u) /* Modulation Bit Counter Bit : 2 */ #define MOD3 (0x0040u) /* Modulation Bit Counter Bit : 3 */ #define MOD4 (0x0080u) /* Modulation Bit Counter Bit : 4 */ #define DCO0 (0x0100u) /* DCO TAP Bit : 0 */ #define DCO1 (0x0200u) /* DCO TAP Bit : 1 */ #define DCO2 (0x0400u) /* DCO TAP Bit : 2 */ #define DCO3 (0x0800u) /* DCO TAP Bit : 3 */ #define DCO4 (0x1000u) /* DCO TAP Bit : 4 */ //#define RESERVED (0x2000u) /* RESERVED */ //#define RESERVED (0x4000u) /* RESERVED */ //#define RESERVED (0x8000u) /* RESERVED */ /* UCSCTL0 Control Bits */ //#define RESERVED (0x0001u) /* RESERVED */ //#define RESERVED (0x0002u) /* RESERVED */ //#define RESERVED (0x0004u) /* RESERVED */ #define MOD0_L (0x0008u) /* Modulation Bit Counter Bit : 0 */ #define MOD1_L (0x0010u) /* Modulation Bit Counter Bit : 1 */ #define MOD2_L (0x0020u) /* Modulation Bit Counter Bit : 2 */ #define MOD3_L (0x0040u) /* Modulation Bit Counter Bit : 3 */ #define MOD4_L (0x0080u) /* Modulation Bit Counter Bit : 4 */ //#define RESERVED (0x2000u) /* RESERVED */ //#define RESERVED (0x4000u) /* RESERVED */ //#define RESERVED (0x8000u) /* RESERVED */ /* UCSCTL0 Control Bits */ //#define RESERVED (0x0001u) /* RESERVED */ //#define RESERVED (0x0002u) /* RESERVED */ //#define RESERVED (0x0004u) /* RESERVED */ #define DCO0_H (0x0001u) /* DCO TAP Bit : 0 */ #define DCO1_H (0x0002u) /* DCO TAP Bit : 1 */ #define DCO2_H (0x0004u) /* DCO TAP Bit : 2 */ #define DCO3_H (0x0008u) /* DCO TAP Bit : 3 */ #define DCO4_H (0x0010u) /* DCO TAP Bit : 4 */ //#define RESERVED (0x2000u) /* RESERVED */ //#define RESERVED (0x4000u) /* RESERVED */ //#define RESERVED (0x8000u) /* RESERVED */ /* UCSCTL1 Control Bits */ #define DISMOD (0x0001u) /* Disable Modulation */ //#define RESERVED (0x0002u) /* RESERVED */ //#define RESERVED (0x0004u) /* RESERVED */ //#define RESERVED (0x0008u) /* RESERVED */ #define DCORSEL0 (0x0010u) /* DCO Freq. Range Select Bit : 0 */ #define DCORSEL1 (0x0020u) /* DCO Freq. Range Select Bit : 1 */ #define DCORSEL2 (0x0040u) /* DCO Freq. Range Select Bit : 2 */ //#define RESERVED (0x0080u) /* RESERVED */ //#define RESERVED (0x0100u) /* RESERVED */ //#define RESERVED (0x0200u) /* RESERVED */ //#define RESERVED (0x0400u) /* RESERVED */ //#define RESERVED (0x0800u) /* RESERVED */ //#define RESERVED (0x1000u) /* RESERVED */ //#define RESERVED (0x2000u) /* RESERVED */ //#define RESERVED (0x4000u) /* RESERVED */ //#define RESERVED (0x8000u) /* RESERVED */ /* UCSCTL1 Control Bits */ #define DISMOD_L (0x0001u) /* Disable Modulation */ //#define RESERVED (0x0002u) /* RESERVED */ //#define RESERVED (0x0004u) /* RESERVED */ //#define RESERVED (0x0008u) /* RESERVED */ #define DCORSEL0_L (0x0010u) /* DCO Freq. Range Select Bit : 0 */ #define DCORSEL1_L (0x0020u) /* DCO Freq. Range Select Bit : 1 */ #define DCORSEL2_L (0x0040u) /* DCO Freq. Range Select Bit : 2 */ //#define RESERVED (0x0080u) /* RESERVED */ //#define RESERVED (0x0100u) /* RESERVED */ //#define RESERVED (0x0200u) /* RESERVED */ //#define RESERVED (0x0400u) /* RESERVED */ //#define RESERVED (0x0800u) /* RESERVED */ //#define RESERVED (0x1000u) /* RESERVED */ //#define RESERVED (0x2000u) /* RESERVED */ //#define RESERVED (0x4000u) /* RESERVED */ //#define RESERVED (0x8000u) /* RESERVED */ /* UCSCTL1 Control Bits */ //#define RESERVED (0x0002u) /* RESERVED */ //#define RESERVED (0x0004u) /* RESERVED */ //#define RESERVED (0x0008u) /* RESERVED */ //#define RESERVED (0x0080u) /* RESERVED */ //#define RESERVED (0x0100u) /* RESERVED */ //#define RESERVED (0x0200u) /* RESERVED */ //#define RESERVED (0x0400u) /* RESERVED */ //#define RESERVED (0x0800u) /* RESERVED */ //#define RESERVED (0x1000u) /* RESERVED */ //#define RESERVED (0x2000u) /* RESERVED */ //#define RESERVED (0x4000u) /* RESERVED */ //#define RESERVED (0x8000u) /* RESERVED */ #define DCORSEL_0 (0x0000u) /* DCO RSEL 0 */ #define DCORSEL_1 (0x0010u) /* DCO RSEL 1 */ #define DCORSEL_2 (0x0020u) /* DCO RSEL 2 */ #define DCORSEL_3 (0x0030u) /* DCO RSEL 3 */ #define DCORSEL_4 (0x0040u) /* DCO RSEL 4 */ #define DCORSEL_5 (0x0050u) /* DCO RSEL 5 */ #define DCORSEL_6 (0x0060u) /* DCO RSEL 6 */ #define DCORSEL_7 (0x0070u) /* DCO RSEL 7 */ /* UCSCTL2 Control Bits */ #define FLLN0 (0x0001u) /* FLL Multipier Bit : 0 */ #define FLLN1 (0x0002u) /* FLL Multipier Bit : 1 */ #define FLLN2 (0x0004u) /* FLL Multipier Bit : 2 */ #define FLLN3 (0x0008u) /* FLL Multipier Bit : 3 */ #define FLLN4 (0x0010u) /* FLL Multipier Bit : 4 */ #define FLLN5 (0x0020u) /* FLL Multipier Bit : 5 */ #define FLLN6 (0x0040u) /* FLL Multipier Bit : 6 */ #define FLLN7 (0x0080u) /* FLL Multipier Bit : 7 */ #define FLLN8 (0x0100u) /* FLL Multipier Bit : 8 */ #define FLLN9 (0x0200u) /* FLL Multipier Bit : 9 */ //#define RESERVED (0x0400u) /* RESERVED */ //#define RESERVED (0x0800u) /* RESERVED */ #define FLLD0 (0x1000u) /* Loop Divider Bit : 0 */ #define FLLD1 (0x2000u) /* Loop Divider Bit : 1 */ #define FLLD2 (0x4000u) /* Loop Divider Bit : 1 */ //#define RESERVED (0x8000u) /* RESERVED */ /* UCSCTL2 Control Bits */ #define FLLN0_L (0x0001u) /* FLL Multipier Bit : 0 */ #define FLLN1_L (0x0002u) /* FLL Multipier Bit : 1 */ #define FLLN2_L (0x0004u) /* FLL Multipier Bit : 2 */ #define FLLN3_L (0x0008u) /* FLL Multipier Bit : 3 */ #define FLLN4_L (0x0010u) /* FLL Multipier Bit : 4 */ #define FLLN5_L (0x0020u) /* FLL Multipier Bit : 5 */ #define FLLN6_L (0x0040u) /* FLL Multipier Bit : 6 */ #define FLLN7_L (0x0080u) /* FLL Multipier Bit : 7 */ //#define RESERVED (0x0400u) /* RESERVED */ //#define RESERVED (0x0800u) /* RESERVED */ //#define RESERVED (0x8000u) /* RESERVED */ /* UCSCTL2 Control Bits */ #define FLLN8_H (0x0001u) /* FLL Multipier Bit : 8 */ #define FLLN9_H (0x0002u) /* FLL Multipier Bit : 9 */ //#define RESERVED (0x0400u) /* RESERVED */ //#define RESERVED (0x0800u) /* RESERVED */ #define FLLD0_H (0x0010u) /* Loop Divider Bit : 0 */ #define FLLD1_H (0x0020u) /* Loop Divider Bit : 1 */ #define FLLD2_H (0x0040u) /* Loop Divider Bit : 1 */ //#define RESERVED (0x8000u) /* RESERVED */ #define FLLD_0 (0x0000u) /* Multiply Selected Loop Freq. 1 */ #define FLLD_1 (0x1000u) /* Multiply Selected Loop Freq. 2 */ #define FLLD_2 (0x2000u) /* Multiply Selected Loop Freq. 4 */ #define FLLD_3 (0x3000u) /* Multiply Selected Loop Freq. 8 */ #define FLLD_4 (0x4000u) /* Multiply Selected Loop Freq. 16 */ #define FLLD_5 (0x5000u) /* Multiply Selected Loop Freq. 32 */ #define FLLD_6 (0x6000u) /* Multiply Selected Loop Freq. 32 */ #define FLLD_7 (0x7000u) /* Multiply Selected Loop Freq. 32 */ #define FLLD__1 (0x0000u) /* Multiply Selected Loop Freq. By 1 */ #define FLLD__2 (0x1000u) /* Multiply Selected Loop Freq. By 2 */ #define FLLD__4 (0x2000u) /* Multiply Selected Loop Freq. By 4 */ #define FLLD__8 (0x3000u) /* Multiply Selected Loop Freq. By 8 */ #define FLLD__16 (0x4000u) /* Multiply Selected Loop Freq. By 16 */ #define FLLD__32 (0x5000u) /* Multiply Selected Loop Freq. By 32 */ /* UCSCTL3 Control Bits */ #define FLLREFDIV0 (0x0001u) /* Reference Divider Bit : 0 */ #define FLLREFDIV1 (0x0002u) /* Reference Divider Bit : 1 */ #define FLLREFDIV2 (0x0004u) /* Reference Divider Bit : 2 */ //#define RESERVED (0x0008u) /* RESERVED */ #define SELREF0 (0x0010u) /* FLL Reference Clock Select Bit : 0 */ #define SELREF1 (0x0020u) /* FLL Reference Clock Select Bit : 1 */ #define SELREF2 (0x0040u) /* FLL Reference Clock Select Bit : 2 */ //#define RESERVED (0x0080u) /* RESERVED */ //#define RESERVED (0x0100u) /* RESERVED */ //#define RESERVED (0x0200u) /* RESERVED */ //#define RESERVED (0x0400u) /* RESERVED */ //#define RESERVED (0x0800u) /* RESERVED */ //#define RESERVED (0x1000u) /* RESERVED */ //#define RESERVED (0x2000u) /* RESERVED */ //#define RESERVED (0x4000u) /* RESERVED */ //#define RESERVED (0x8000u) /* RESERVED */ /* UCSCTL3 Control Bits */ #define FLLREFDIV0_L (0x0001u) /* Reference Divider Bit : 0 */ #define FLLREFDIV1_L (0x0002u) /* Reference Divider Bit : 1 */ #define FLLREFDIV2_L (0x0004u) /* Reference Divider Bit : 2 */ //#define RESERVED (0x0008u) /* RESERVED */ #define SELREF0_L (0x0010u) /* FLL Reference Clock Select Bit : 0 */ #define SELREF1_L (0x0020u) /* FLL Reference Clock Select Bit : 1 */ #define SELREF2_L (0x0040u) /* FLL Reference Clock Select Bit : 2 */ //#define RESERVED (0x0080u) /* RESERVED */ //#define RESERVED (0x0100u) /* RESERVED */ //#define RESERVED (0x0200u) /* RESERVED */ //#define RESERVED (0x0400u) /* RESERVED */ //#define RESERVED (0x0800u) /* RESERVED */ //#define RESERVED (0x1000u) /* RESERVED */ //#define RESERVED (0x2000u) /* RESERVED */ //#define RESERVED (0x4000u) /* RESERVED */ //#define RESERVED (0x8000u) /* RESERVED */ /* UCSCTL3 Control Bits */ //#define RESERVED (0x0008u) /* RESERVED */ //#define RESERVED (0x0080u) /* RESERVED */ //#define RESERVED (0x0100u) /* RESERVED */ //#define RESERVED (0x0200u) /* RESERVED */ //#define RESERVED (0x0400u) /* RESERVED */ //#define RESERVED (0x0800u) /* RESERVED */ //#define RESERVED (0x1000u) /* RESERVED */ //#define RESERVED (0x2000u) /* RESERVED */ //#define RESERVED (0x4000u) /* RESERVED */ //#define RESERVED (0x8000u) /* RESERVED */ #define FLLREFDIV_0 (0x0000u) /* Reference Divider: f(LFCLK)/1 */ #define FLLREFDIV_1 (0x0001u) /* Reference Divider: f(LFCLK)/2 */ #define FLLREFDIV_2 (0x0002u) /* Reference Divider: f(LFCLK)/4 */ #define FLLREFDIV_3 (0x0003u) /* Reference Divider: f(LFCLK)/8 */ #define FLLREFDIV_4 (0x0004u) /* Reference Divider: f(LFCLK)/12 */ #define FLLREFDIV_5 (0x0005u) /* Reference Divider: f(LFCLK)/16 */ #define FLLREFDIV_6 (0x0006u) /* Reference Divider: f(LFCLK)/16 */ #define FLLREFDIV_7 (0x0007u) /* Reference Divider: f(LFCLK)/16 */ #define FLLREFDIV__1 (0x0000u) /* Reference Divider: f(LFCLK)/1 */ #define FLLREFDIV__2 (0x0001u) /* Reference Divider: f(LFCLK)/2 */ #define FLLREFDIV__4 (0x0002u) /* Reference Divider: f(LFCLK)/4 */ #define FLLREFDIV__8 (0x0003u) /* Reference Divider: f(LFCLK)/8 */ #define FLLREFDIV__12 (0x0004u) /* Reference Divider: f(LFCLK)/12 */ #define FLLREFDIV__16 (0x0005u) /* Reference Divider: f(LFCLK)/16 */ #define SELREF_0 (0x0000u) /* FLL Reference Clock Select 0 */ #define SELREF_1 (0x0010u) /* FLL Reference Clock Select 1 */ #define SELREF_2 (0x0020u) /* FLL Reference Clock Select 2 */ #define SELREF_3 (0x0030u) /* FLL Reference Clock Select 3 */ #define SELREF_4 (0x0040u) /* FLL Reference Clock Select 4 */ #define SELREF_5 (0x0050u) /* FLL Reference Clock Select 5 */ #define SELREF_6 (0x0060u) /* FLL Reference Clock Select 6 */ #define SELREF_7 (0x0070u) /* FLL Reference Clock Select 7 */ #define SELREF__XT1CLK (0x0000u) /* Multiply Selected Loop Freq. By XT1CLK */ #define SELREF__REFOCLK (0x0020u) /* Multiply Selected Loop Freq. By REFOCLK */ #define SELREF__XT2CLK (0x0050u) /* Multiply Selected Loop Freq. By XT2CLK */ /* UCSCTL4 Control Bits */ #define SELM0 (0x0001u) /* MCLK Source Select Bit: 0 */ #define SELM1 (0x0002u) /* MCLK Source Select Bit: 1 */ #define SELM2 (0x0004u) /* MCLK Source Select Bit: 2 */ //#define RESERVED (0x0008u) /* RESERVED */ #define SELS0 (0x0010u) /* SMCLK Source Select Bit: 0 */ #define SELS1 (0x0020u) /* SMCLK Source Select Bit: 1 */ #define SELS2 (0x0040u) /* SMCLK Source Select Bit: 2 */ //#define RESERVED (0x0080u) /* RESERVED */ #define SELA0 (0x0100u) /* ACLK Source Select Bit: 0 */ #define SELA1 (0x0200u) /* ACLK Source Select Bit: 1 */ #define SELA2 (0x0400u) /* ACLK Source Select Bit: 2 */ //#define RESERVED (0x0800u) /* RESERVED */ //#define RESERVED (0x1000u) /* RESERVED */ //#define RESERVED (0x2000u) /* RESERVED */ //#define RESERVED (0x4000u) /* RESERVED */ //#define RESERVED (0x8000u) /* RESERVED */ /* UCSCTL4 Control Bits */ #define SELM0_L (0x0001u) /* MCLK Source Select Bit: 0 */ #define SELM1_L (0x0002u) /* MCLK Source Select Bit: 1 */ #define SELM2_L (0x0004u) /* MCLK Source Select Bit: 2 */ //#define RESERVED (0x0008u) /* RESERVED */ #define SELS0_L (0x0010u) /* SMCLK Source Select Bit: 0 */ #define SELS1_L (0x0020u) /* SMCLK Source Select Bit: 1 */ #define SELS2_L (0x0040u) /* SMCLK Source Select Bit: 2 */ //#define RESERVED (0x0080u) /* RESERVED */ //#define RESERVED (0x0800u) /* RESERVED */ //#define RESERVED (0x1000u) /* RESERVED */ //#define RESERVED (0x2000u) /* RESERVED */ //#define RESERVED (0x4000u) /* RESERVED */ //#define RESERVED (0x8000u) /* RESERVED */ /* UCSCTL4 Control Bits */ //#define RESERVED (0x0008u) /* RESERVED */ //#define RESERVED (0x0080u) /* RESERVED */ #define SELA0_H (0x0001u) /* ACLK Source Select Bit: 0 */ #define SELA1_H (0x0002u) /* ACLK Source Select Bit: 1 */ #define SELA2_H (0x0004u) /* ACLK Source Select Bit: 2 */ //#define RESERVED (0x0800u) /* RESERVED */ //#define RESERVED (0x1000u) /* RESERVED */ //#define RESERVED (0x2000u) /* RESERVED */ //#define RESERVED (0x4000u) /* RESERVED */ //#define RESERVED (0x8000u) /* RESERVED */ #define SELM_0 (0x0000u) /* MCLK Source Select 0 */ #define SELM_1 (0x0001u) /* MCLK Source Select 1 */ #define SELM_2 (0x0002u) /* MCLK Source Select 2 */ #define SELM_3 (0x0003u) /* MCLK Source Select 3 */ #define SELM_4 (0x0004u) /* MCLK Source Select 4 */ #define SELM_5 (0x0005u) /* MCLK Source Select 5 */ #define SELM_6 (0x0006u) /* MCLK Source Select 6 */ #define SELM_7 (0x0007u) /* MCLK Source Select 7 */ #define SELM__XT1CLK (0x0000u) /* MCLK Source Select XT1CLK */ #define SELM__VLOCLK (0x0001u) /* MCLK Source Select VLOCLK */ #define SELM__REFOCLK (0x0002u) /* MCLK Source Select REFOCLK */ #define SELM__DCOCLK (0x0003u) /* MCLK Source Select DCOCLK */ #define SELM__DCOCLKDIV (0x0004u) /* MCLK Source Select DCOCLKDIV */ #define SELM__XT2CLK (0x0005u) /* MCLK Source Select XT2CLK */ #define SELS_0 (0x0000u) /* SMCLK Source Select 0 */ #define SELS_1 (0x0010u) /* SMCLK Source Select 1 */ #define SELS_2 (0x0020u) /* SMCLK Source Select 2 */ #define SELS_3 (0x0030u) /* SMCLK Source Select 3 */ #define SELS_4 (0x0040u) /* SMCLK Source Select 4 */ #define SELS_5 (0x0050u) /* SMCLK Source Select 5 */ #define SELS_6 (0x0060u) /* SMCLK Source Select 6 */ #define SELS_7 (0x0070u) /* SMCLK Source Select 7 */ #define SELS__XT1CLK (0x0000u) /* SMCLK Source Select XT1CLK */ #define SELS__VLOCLK (0x0010u) /* SMCLK Source Select VLOCLK */ #define SELS__REFOCLK (0x0020u) /* SMCLK Source Select REFOCLK */ #define SELS__DCOCLK (0x0030u) /* SMCLK Source Select DCOCLK */ #define SELS__DCOCLKDIV (0x0040u) /* SMCLK Source Select DCOCLKDIV */ #define SELS__XT2CLK (0x0050u) /* SMCLK Source Select XT2CLK */ #define SELA_0 (0x0000u) /* ACLK Source Select 0 */ #define SELA_1 (0x0100u) /* ACLK Source Select 1 */ #define SELA_2 (0x0200u) /* ACLK Source Select 2 */ #define SELA_3 (0x0300u) /* ACLK Source Select 3 */ #define SELA_4 (0x0400u) /* ACLK Source Select 4 */ #define SELA_5 (0x0500u) /* ACLK Source Select 5 */ #define SELA_6 (0x0600u) /* ACLK Source Select 6 */ #define SELA_7 (0x0700u) /* ACLK Source Select 7 */ #define SELA__XT1CLK (0x0000u) /* ACLK Source Select XT1CLK */ #define SELA__VLOCLK (0x0100u) /* ACLK Source Select VLOCLK */ #define SELA__REFOCLK (0x0200u) /* ACLK Source Select REFOCLK */ #define SELA__DCOCLK (0x0300u) /* ACLK Source Select DCOCLK */ #define SELA__DCOCLKDIV (0x0400u) /* ACLK Source Select DCOCLKDIV */ #define SELA__XT2CLK (0x0500u) /* ACLK Source Select XT2CLK */ /* UCSCTL5 Control Bits */ #define DIVM0 (0x0001u) /* MCLK Divider Bit: 0 */ #define DIVM1 (0x0002u) /* MCLK Divider Bit: 1 */ #define DIVM2 (0x0004u) /* MCLK Divider Bit: 2 */ //#define RESERVED (0x0008u) /* RESERVED */ #define DIVS0 (0x0010u) /* SMCLK Divider Bit: 0 */ #define DIVS1 (0x0020u) /* SMCLK Divider Bit: 1 */ #define DIVS2 (0x0040u) /* SMCLK Divider Bit: 2 */ //#define RESERVED (0x0080u) /* RESERVED */ #define DIVA0 (0x0100u) /* ACLK Divider Bit: 0 */ #define DIVA1 (0x0200u) /* ACLK Divider Bit: 1 */ #define DIVA2 (0x0400u) /* ACLK Divider Bit: 2 */ //#define RESERVED (0x0800u) /* RESERVED */ #define DIVPA0 (0x1000u) /* ACLK from Pin Divider Bit: 0 */ #define DIVPA1 (0x2000u) /* ACLK from Pin Divider Bit: 1 */ #define DIVPA2 (0x4000u) /* ACLK from Pin Divider Bit: 2 */ //#define RESERVED (0x8000u) /* RESERVED */ /* UCSCTL5 Control Bits */ #define DIVM0_L (0x0001u) /* MCLK Divider Bit: 0 */ #define DIVM1_L (0x0002u) /* MCLK Divider Bit: 1 */ #define DIVM2_L (0x0004u) /* MCLK Divider Bit: 2 */ //#define RESERVED (0x0008u) /* RESERVED */ #define DIVS0_L (0x0010u) /* SMCLK Divider Bit: 0 */ #define DIVS1_L (0x0020u) /* SMCLK Divider Bit: 1 */ #define DIVS2_L (0x0040u) /* SMCLK Divider Bit: 2 */ //#define RESERVED (0x0080u) /* RESERVED */ //#define RESERVED (0x0800u) /* RESERVED */ //#define RESERVED (0x8000u) /* RESERVED */ /* UCSCTL5 Control Bits */ //#define RESERVED (0x0008u) /* RESERVED */ //#define RESERVED (0x0080u) /* RESERVED */ #define DIVA0_H (0x0001u) /* ACLK Divider Bit: 0 */ #define DIVA1_H (0x0002u) /* ACLK Divider Bit: 1 */ #define DIVA2_H (0x0004u) /* ACLK Divider Bit: 2 */ //#define RESERVED (0x0800u) /* RESERVED */ #define DIVPA0_H (0x0010u) /* ACLK from Pin Divider Bit: 0 */ #define DIVPA1_H (0x0020u) /* ACLK from Pin Divider Bit: 1 */ #define DIVPA2_H (0x0040u) /* ACLK from Pin Divider Bit: 2 */ //#define RESERVED (0x8000u) /* RESERVED */ #define DIVM_0 (0x0000u) /* MCLK Source Divider 0 */ #define DIVM_1 (0x0001u) /* MCLK Source Divider 1 */ #define DIVM_2 (0x0002u) /* MCLK Source Divider 2 */ #define DIVM_3 (0x0003u) /* MCLK Source Divider 3 */ #define DIVM_4 (0x0004u) /* MCLK Source Divider 4 */ #define DIVM_5 (0x0005u) /* MCLK Source Divider 5 */ #define DIVM_6 (0x0006u) /* MCLK Source Divider 6 */ #define DIVM_7 (0x0007u) /* MCLK Source Divider 7 */ #define DIVM__1 (0x0000u) /* MCLK Source Divider f(MCLK)/1 */ #define DIVM__2 (0x0001u) /* MCLK Source Divider f(MCLK)/2 */ #define DIVM__4 (0x0002u) /* MCLK Source Divider f(MCLK)/4 */ #define DIVM__8 (0x0003u) /* MCLK Source Divider f(MCLK)/8 */ #define DIVM__16 (0x0004u) /* MCLK Source Divider f(MCLK)/16 */ #define DIVM__32 (0x0005u) /* MCLK Source Divider f(MCLK)/32 */ #define DIVS_0 (0x0000u) /* SMCLK Source Divider 0 */ #define DIVS_1 (0x0010u) /* SMCLK Source Divider 1 */ #define DIVS_2 (0x0020u) /* SMCLK Source Divider 2 */ #define DIVS_3 (0x0030u) /* SMCLK Source Divider 3 */ #define DIVS_4 (0x0040u) /* SMCLK Source Divider 4 */ #define DIVS_5 (0x0050u) /* SMCLK Source Divider 5 */ #define DIVS_6 (0x0060u) /* SMCLK Source Divider 6 */ #define DIVS_7 (0x0070u) /* SMCLK Source Divider 7 */ #define DIVS__1 (0x0000u) /* SMCLK Source Divider f(SMCLK)/1 */ #define DIVS__2 (0x0010u) /* SMCLK Source Divider f(SMCLK)/2 */ #define DIVS__4 (0x0020u) /* SMCLK Source Divider f(SMCLK)/4 */ #define DIVS__8 (0x0030u) /* SMCLK Source Divider f(SMCLK)/8 */ #define DIVS__16 (0x0040u) /* SMCLK Source Divider f(SMCLK)/16 */ #define DIVS__32 (0x0050u) /* SMCLK Source Divider f(SMCLK)/32 */ #define DIVA_0 (0x0000u) /* ACLK Source Divider 0 */ #define DIVA_1 (0x0100u) /* ACLK Source Divider 1 */ #define DIVA_2 (0x0200u) /* ACLK Source Divider 2 */ #define DIVA_3 (0x0300u) /* ACLK Source Divider 3 */ #define DIVA_4 (0x0400u) /* ACLK Source Divider 4 */ #define DIVA_5 (0x0500u) /* ACLK Source Divider 5 */ #define DIVA_6 (0x0600u) /* ACLK Source Divider 6 */ #define DIVA_7 (0x0700u) /* ACLK Source Divider 7 */ #define DIVA__1 (0x0000u) /* ACLK Source Divider f(ACLK)/1 */ #define DIVA__2 (0x0100u) /* ACLK Source Divider f(ACLK)/2 */ #define DIVA__4 (0x0200u) /* ACLK Source Divider f(ACLK)/4 */ #define DIVA__8 (0x0300u) /* ACLK Source Divider f(ACLK)/8 */ #define DIVA__16 (0x0400u) /* ACLK Source Divider f(ACLK)/16 */ #define DIVA__32 (0x0500u) /* ACLK Source Divider f(ACLK)/32 */ #define DIVPA_0 (0x0000u) /* ACLK from Pin Source Divider 0 */ #define DIVPA_1 (0x1000u) /* ACLK from Pin Source Divider 1 */ #define DIVPA_2 (0x2000u) /* ACLK from Pin Source Divider 2 */ #define DIVPA_3 (0x3000u) /* ACLK from Pin Source Divider 3 */ #define DIVPA_4 (0x4000u) /* ACLK from Pin Source Divider 4 */ #define DIVPA_5 (0x5000u) /* ACLK from Pin Source Divider 5 */ #define DIVPA_6 (0x6000u) /* ACLK from Pin Source Divider 6 */ #define DIVPA_7 (0x7000u) /* ACLK from Pin Source Divider 7 */ #define DIVPA__1 (0x0000u) /* ACLK from Pin Source Divider f(ACLK)/1 */ #define DIVPA__2 (0x1000u) /* ACLK from Pin Source Divider f(ACLK)/2 */ #define DIVPA__4 (0x2000u) /* ACLK from Pin Source Divider f(ACLK)/4 */ #define DIVPA__8 (0x3000u) /* ACLK from Pin Source Divider f(ACLK)/8 */ #define DIVPA__16 (0x4000u) /* ACLK from Pin Source Divider f(ACLK)/16 */ #define DIVPA__32 (0x5000u) /* ACLK from Pin Source Divider f(ACLK)/32 */ /* UCSCTL6 Control Bits */ #define XT1OFF (0x0001u) /* High Frequency Oscillator 1 (XT1) disable */ #define SMCLKOFF (0x0002u) /* SMCLK Off */ #define XCAP0 (0x0004u) /* XIN/XOUT Cap Bit: 0 */ #define XCAP1 (0x0008u) /* XIN/XOUT Cap Bit: 1 */ #define XT1BYPASS (0x0010u) /* XT1 bypass mode : 0: internal 1:sourced from external pin */ #define XTS (0x0020u) /* 1: Selects high-freq. oscillator */ #define XT1DRIVE0 (0x0040u) /* XT1 Drive Level mode Bit 0 */ #define XT1DRIVE1 (0x0080u) /* XT1 Drive Level mode Bit 1 */ #define XT2OFF (0x0100u) /* High Frequency Oscillator 2 (XT2) disable */ //#define RESERVED (0x0200u) /* RESERVED */ //#define RESERVED (0x0400u) /* RESERVED */ //#define RESERVED (0x0800u) /* RESERVED */ #define XT2BYPASS (0x1000u) /* XT2 bypass mode : 0: internal 1:sourced from external pin */ //#define RESERVED (0x2000u) /* RESERVED */ #define XT2DRIVE0 (0x4000u) /* XT2 Drive Level mode Bit 0 */ #define XT2DRIVE1 (0x8000u) /* XT2 Drive Level mode Bit 1 */ /* UCSCTL6 Control Bits */ #define XT1OFF_L (0x0001u) /* High Frequency Oscillator 1 (XT1) disable */ #define SMCLKOFF_L (0x0002u) /* SMCLK Off */ #define XCAP0_L (0x0004u) /* XIN/XOUT Cap Bit: 0 */ #define XCAP1_L (0x0008u) /* XIN/XOUT Cap Bit: 1 */ #define XT1BYPASS_L (0x0010u) /* XT1 bypass mode : 0: internal 1:sourced from external pin */ #define XTS_L (0x0020u) /* 1: Selects high-freq. oscillator */ #define XT1DRIVE0_L (0x0040u) /* XT1 Drive Level mode Bit 0 */ #define XT1DRIVE1_L (0x0080u) /* XT1 Drive Level mode Bit 1 */ //#define RESERVED (0x0200u) /* RESERVED */ //#define RESERVED (0x0400u) /* RESERVED */ //#define RESERVED (0x0800u) /* RESERVED */ //#define RESERVED (0x2000u) /* RESERVED */ /* UCSCTL6 Control Bits */ #define XT2OFF_H (0x0001u) /* High Frequency Oscillator 2 (XT2) disable */ //#define RESERVED (0x0200u) /* RESERVED */ //#define RESERVED (0x0400u) /* RESERVED */ //#define RESERVED (0x0800u) /* RESERVED */ #define XT2BYPASS_H (0x0010u) /* XT2 bypass mode : 0: internal 1:sourced from external pin */ //#define RESERVED (0x2000u) /* RESERVED */ #define XT2DRIVE0_H (0x0040u) /* XT2 Drive Level mode Bit 0 */ #define XT2DRIVE1_H (0x0080u) /* XT2 Drive Level mode Bit 1 */ #define XCAP_0 (0x0000u) /* XIN/XOUT Cap 0 */ #define XCAP_1 (0x0004u) /* XIN/XOUT Cap 1 */ #define XCAP_2 (0x0008u) /* XIN/XOUT Cap 2 */ #define XCAP_3 (0x000Cu) /* XIN/XOUT Cap 3 */ #define XT1DRIVE_0 (0x0000u) /* XT1 Drive Level mode: 0 */ #define XT1DRIVE_1 (0x0040u) /* XT1 Drive Level mode: 1 */ #define XT1DRIVE_2 (0x0080u) /* XT1 Drive Level mode: 2 */ #define XT1DRIVE_3 (0x00C0u) /* XT1 Drive Level mode: 3 */ #define XT2DRIVE_0 (0x0000u) /* XT2 Drive Level mode: 0 */ #define XT2DRIVE_1 (0x4000u) /* XT2 Drive Level mode: 1 */ #define XT2DRIVE_2 (0x8000u) /* XT2 Drive Level mode: 2 */ #define XT2DRIVE_3 (0xC000u) /* XT2 Drive Level mode: 3 */ /* UCSCTL7 Control Bits */ #define DCOFFG (0x0001u) /* DCO Fault Flag */ #define XT1LFOFFG (0x0002u) /* XT1 Low Frequency Oscillator Fault Flag */ //#define RESERVED (0x0004u) /* RESERVED */ #define XT2OFFG (0x0008u) /* High Frequency Oscillator 2 Fault Flag */ //#define RESERVED (0x0010u) /* RESERVED */ //#define RESERVED (0x0020u) /* RESERVED */ //#define RESERVED (0x0040u) /* RESERVED */ //#define RESERVED (0x0080u) /* RESERVED */ //#define RESERVED (0x0100u) /* RESERVED */ //#define RESERVED (0x0200u) /* RESERVED */ //#define RESERVED (0x0400u) /* RESERVED */ //#define RESERVED (0x0800u) /* RESERVED */ //#define RESERVED (0x1000u) /* RESERVED */ //#define RESERVED (0x2000u) /* RESERVED */ //#define RESERVED (0x4000u) /* RESERVED */ //#define RESERVED (0x8000u) /* RESERVED */ /* UCSCTL7 Control Bits */ #define DCOFFG_L (0x0001u) /* DCO Fault Flag */ #define XT1LFOFFG_L (0x0002u) /* XT1 Low Frequency Oscillator Fault Flag */ //#define RESERVED (0x0004u) /* RESERVED */ #define XT2OFFG_L (0x0008u) /* High Frequency Oscillator 2 Fault Flag */ //#define RESERVED (0x0010u) /* RESERVED */ //#define RESERVED (0x0020u) /* RESERVED */ //#define RESERVED (0x0040u) /* RESERVED */ //#define RESERVED (0x0080u) /* RESERVED */ //#define RESERVED (0x0100u) /* RESERVED */ //#define RESERVED (0x0200u) /* RESERVED */ //#define RESERVED (0x0400u) /* RESERVED */ //#define RESERVED (0x0800u) /* RESERVED */ //#define RESERVED (0x1000u) /* RESERVED */ //#define RESERVED (0x2000u) /* RESERVED */ //#define RESERVED (0x4000u) /* RESERVED */ //#define RESERVED (0x8000u) /* RESERVED */ /* UCSCTL7 Control Bits */ //#define RESERVED (0x0004u) /* RESERVED */ //#define RESERVED (0x0010u) /* RESERVED */ //#define RESERVED (0x0020u) /* RESERVED */ //#define RESERVED (0x0040u) /* RESERVED */ //#define RESERVED (0x0080u) /* RESERVED */ //#define RESERVED (0x0100u) /* RESERVED */ //#define RESERVED (0x0200u) /* RESERVED */ //#define RESERVED (0x0400u) /* RESERVED */ //#define RESERVED (0x0800u) /* RESERVED */ //#define RESERVED (0x1000u) /* RESERVED */ //#define RESERVED (0x2000u) /* RESERVED */ //#define RESERVED (0x4000u) /* RESERVED */ //#define RESERVED (0x8000u) /* RESERVED */ /* UCSCTL8 Control Bits */ #define ACLKREQEN (0x0001u) /* ACLK Clock Request Enable */ #define MCLKREQEN (0x0002u) /* MCLK Clock Request Enable */ #define SMCLKREQEN (0x0004u) /* SMCLK Clock Request Enable */ #define MODOSCREQEN (0x0008u) /* MODOSC Clock Request Enable */ //#define RESERVED (0x0010u) /* RESERVED */ //#define RESERVED (0x0020u) /* RESERVED */ //#define RESERVED (0x0040u) /* RESERVED */ //#define RESERVED (0x0080u) /* RESERVED */ //#define RESERVED (0x0100u) /* RESERVED */ //#define RESERVED (0x0200u) /* RESERVED */ //#define RESERVED (0x0400u) /* RESERVED */ //#define RESERVED (0x0800u) /* RESERVED */ //#define RESERVED (0x1000u) /* RESERVED */ //#define RESERVED (0x2000u) /* RESERVED */ //#define RESERVED (0x4000u) /* RESERVED */ //#define RESERVED (0x8000u) /* RESERVED */ /* UCSCTL8 Control Bits */ #define ACLKREQEN_L (0x0001u) /* ACLK Clock Request Enable */ #define MCLKREQEN_L (0x0002u) /* MCLK Clock Request Enable */ #define SMCLKREQEN_L (0x0004u) /* SMCLK Clock Request Enable */ #define MODOSCREQEN_L (0x0008u) /* MODOSC Clock Request Enable */ //#define RESERVED (0x0010u) /* RESERVED */ //#define RESERVED (0x0020u) /* RESERVED */ //#define RESERVED (0x0040u) /* RESERVED */ //#define RESERVED (0x0080u) /* RESERVED */ //#define RESERVED (0x0100u) /* RESERVED */ //#define RESERVED (0x0200u) /* RESERVED */ //#define RESERVED (0x0400u) /* RESERVED */ //#define RESERVED (0x0800u) /* RESERVED */ //#define RESERVED (0x1000u) /* RESERVED */ //#define RESERVED (0x2000u) /* RESERVED */ //#define RESERVED (0x4000u) /* RESERVED */ //#define RESERVED (0x8000u) /* RESERVED */ /* UCSCTL8 Control Bits */ //#define RESERVED (0x0010u) /* RESERVED */ //#define RESERVED (0x0020u) /* RESERVED */ //#define RESERVED (0x0040u) /* RESERVED */ //#define RESERVED (0x0080u) /* RESERVED */ //#define RESERVED (0x0100u) /* RESERVED */ //#define RESERVED (0x0200u) /* RESERVED */ //#define RESERVED (0x0400u) /* RESERVED */ //#define RESERVED (0x0800u) /* RESERVED */ //#define RESERVED (0x1000u) /* RESERVED */ //#define RESERVED (0x2000u) /* RESERVED */ //#define RESERVED (0x4000u) /* RESERVED */ //#define RESERVED (0x8000u) /* RESERVED */ /************************************************************ * USCI A0 ************************************************************/ #define __MSP430_HAS_USCI_A0__ /* Definition to show that Module is available */ #define __MSP430_BASEADDRESS_USCI_A0__ 0x05C0 #define UCA0CTLW0_ (0x05C0u) /* USCI A0 Control Word Register 0 */ DEFCW( UCA0CTLW0 , UCA0CTLW0_) #define UCA0CTL1 UCA0CTLW0_L /* USCI A0 Control Register 1 */ #define UCA0CTL0 UCA0CTLW0_H /* USCI A0 Control Register 0 */ #define UCA0BRW_ (0x05C6u) /* USCI A0 Baud Word Rate 0 */ DEFCW( UCA0BRW , UCA0BRW_) #define UCA0BR0 UCA0BRW_L /* USCI A0 Baud Rate 0 */ #define UCA0BR1 UCA0BRW_H /* USCI A0 Baud Rate 1 */ #define UCA0MCTL_ (0x05C8u) /* USCI A0 Modulation Control */ DEFC( UCA0MCTL , UCA0MCTL_) #define UCA0STAT_ (0x05CAu) /* USCI A0 Status Register */ DEFC( UCA0STAT , UCA0STAT_) #define UCA0RXBUF_ (0x05CCu) /* USCI A0 Receive Buffer */ READ_ONLY DEFC( UCA0RXBUF , UCA0RXBUF_) #define UCA0TXBUF_ (0x05CEu) /* USCI A0 Transmit Buffer */ DEFC( UCA0TXBUF , UCA0TXBUF_) #define UCA0ABCTL_ (0x05D0u) /* USCI A0 LIN Control */ DEFC( UCA0ABCTL , UCA0ABCTL_) #define UCA0IRCTL_ (0x05D2u) /* USCI A0 IrDA Transmit Control */ DEFCW( UCA0IRCTL , UCA0IRCTL_) #define UCA0IRTCTL UCA0IRCTL_L /* USCI A0 IrDA Transmit Control */ #define UCA0IRRCTL UCA0IRCTL_H /* USCI A0 IrDA Receive Control */ #define UCA0ICTL_ (0x05DCu) /* USCI A0 Interrupt Enable Register */ DEFCW( UCA0ICTL , UCA0ICTL_) #define UCA0IE UCA0ICTL_L /* USCI A0 Interrupt Enable Register */ #define UCA0IFG UCA0ICTL_H /* USCI A0 Interrupt Flags Register */ #define UCA0IV_ (0x05DEu) /* USCI A0 Interrupt Vector Register */ DEFW( UCA0IV , UCA0IV_)