|

直流電機綜合測控系統的設計 采用PWM控制方式對直流電機進行速度控制、旋轉方向的控制和變速控制。 - 設計要求

- 詳細說明系統工作原理與設計方案;

- 用VHDL編寫設計程序;

- 給出系統仿真結果;

- 進行硬件驗證;

目 錄

1 引言1

1.1 課題研究背景3

1.2 課題研究的現狀4

1.3 可以主要研究內容及意義

2 PWM原理及課題原理6

2.1 PWM原理6

2.2課題原理7

3課程設計原理及模塊介紹

3.1 系統總體組成及框圖

3.2 電機轉速控制模塊

3.2.1 設計思想及模塊原理圖

3.2.2 轉速模塊VHDL設計語言

3.2.3 轉速模塊仿真結果

3.3 正反轉向控制模塊

3.3.1 設計思想及模塊原理圖

3.3.2 正反轉向模塊VHDL設計語言

3.3.3 正反轉向模塊仿真結果

3.4 轉速測定及顯示模塊

3.4.1 設計思想及模塊圖

3.4.2 轉速測定模塊CHDL設計語言

3.4.3 轉速測定仿真結果

3.5 消抖模塊

3.5.1 設計思想及原理圖

3.5.2 消抖模塊VHDL設計語言

3.5.3 消抖模塊仿真結果

4 硬件電路及測試結果

4.1 直流電機的介紹

4.2 紅外測速模塊

4.3 引腳配置

4.4 測試

5 結論34

參考文獻 35

附錄 36

一 引言 1.1 課題研究背景 電機作為機電能轉換裝置,其范圍已遍及國民經濟的各個領域。近些年來,隨著現代電力電子技術、控制技術和計算機技術的發展,電機的控制技術也得到了進一步的發展,電機應用已由過去簡單的起停控制、提供動力為目的的應用,上升到對其速度、位置、轉矩等進行精確的控制,使被驅動的機械符合預想的要求。采用功率器進行控制,將預定的控制方案、規劃指令轉變成期望的機械運動,這種新型控制技術已經不是傳統的“電機控制”、“電氣傳動”而是“運動控制”。運動控制使被控制機械運動實現精確地位置控制、速度控制、加速控制、轉矩或力的控制,以及這些被控制兩量的綜合控制。 1.2 課題研究的現狀 近幾年來,由于微電子技術與計算機技術的飛速發展及單片機的普及,將調速裝置向密集化、小型化和智能化方向發展。國外交直流系統數字化已經達到實用階段。由微處理器為技術核心的數字控制系統硬件電路的標準化程度高,需要成本低,并不受器件的溫度漂移所引起的影響。數字控制系統能夠有效的進行邏 輯判斷和復雜的運算,能做到不同于一般線性調節的最優化、適應性、非線性、智能化等控制規律。如采用微機控制產生PWM信號。用微機或單片機產生PWM信號波形,需要通過D/A轉換器產生鋸齒波電壓和設置參考電壓,通過外接模擬比較器輸出PWM波形,因此外圍電路比較復雜。單片機,雖然D S P 具 備生 成PWM信號及捕獲電機編碼器信號的能力,但其對IC生成 PWM信 號 的通 道數目及電機編碼器捕獲通道數目有限。對多個直流電機的控制很難滿足要求。 基于現場可編程門陣列FPGA對直流電機的控制策略, 為實現電動機數字控制提供了一種有效的方法。FPGA器 件具有集成度高、體積小、運算速度快、易于修改等特點。用FPGA來實現多 路PWM調控,內部自帶數模變換功能,不再需要外接數模轉換設備,形式簡單,誤差小、控制性能強。用單片機和DSP的控制都難以達到同樣的控制效果 1.3 課程的主要研究內容及意義 FPGA的開發語言(VHDL語言)是一種用于數字系統設計和測試的硬件描述語言,也是我們國家極力推廣的一種標準語言。本課題是以FPGA為控制核心,學習直流電機PWM的FPGA控制,通過PWM的控制,實現對直流電機的轉速測量、轉速調節和轉向控制。 設計直流電機控制系統能夠充分發揮電機的特性,通過本課題,一方面訓練我在查閱資料的基礎上,了解FPGA控制的一些基本技術,掌握其控制系統的分析方法與實現;另一方面通過本次設計,設計出相應的控制系統,以實現對直流電機轉速的測量、轉速的調節和轉向的控制,并以此培養自己的自學和動手能力,從而為今后參加工作或進一步深造打下良好的基礎。 2.1 PWM原理 脈沖寬度調制(PWM)是英文“Pulse Width Modulation”的縮寫,簡稱脈寬調制。它是利用微處理器的數字輸出來對模擬電路進行控制的一種非常有效的技術,廣泛應用于測量,通信,功率控制與變換等許多領域。 脈沖寬度調制(PWM)是一種對模擬信號電平進行數字編碼的方法。通過高分辨率計數器的使用,方波的占空比被調制用來對一個具體模擬信號的電平進行編碼。PWM信號仍然是數字的,因為在給定的任何時刻,滿幅值的直流供電要么完全有(ON),要么完全無(OFF)。電壓或電流源是以一種通(ON)或斷(OFF)的重復脈沖序列被加到模擬負載上去的。通的時候即是直流供電被加到負載上的時候,斷的時候即是供電被斷開的時候。只要帶寬足夠,任何模擬值都可以使用PWM進行編碼。 PWM的一個優點是從處理器到被控系統信號都是數字形式的,無需進行數模轉換。讓信號保持為數字形式可將噪聲影響降到最小。噪聲只有在強到足以將邏輯1改變為邏輯0或將邏輯0改變為邏輯1時,也才能對數字信號產生影響。

對噪聲抵抗能力的增強是PWM相對于模擬控制的另外一個優點,而且這也是在某些時候將PWM用于通信的主要原因。從模擬信號轉向PWM可以極大地延長通信距離。在接收端,通過適當的RC或LC網絡可以濾除調制高頻方波并將信號還原為模擬形式。

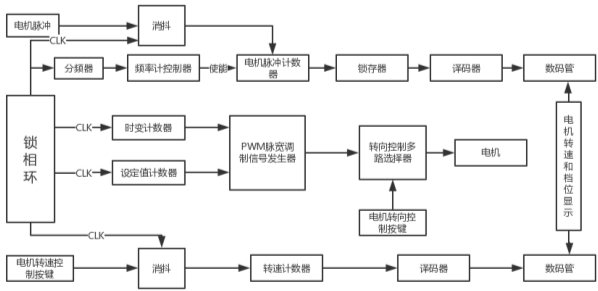

總之,PWM既經濟、節約空間、抗噪性能強,是一種值得廣大工程師在許多設計應用中使用的有效技術。 2.2 課題原理 一般的脈寬調制PWM信號是通過模擬比較器產生的,比較器的一端接給定的參考電壓,另一端接周期性線性增加的鋸齒波電壓。當鋸齒波電壓小于參考電壓時輸出低電平,當鋸齒波電壓大于參考電壓時輸出高電平。改變參考電壓就可以改變PWM波形中高電平的寬度。若用單片機產生PWM信號波形,需要通過DA裝換器產生鋸齒波電壓和設置參考電壓,通過外接模擬比較器輸出PWM波形,因此外圍電路比較復雜。 FPGA中的數字PWM控制與一般的模擬PWM控制不同。用FPGA產生PWM波形,只需FPGA內部資源就可以實現。用數字比較器代替比較器,其一端接設定值計數器輸出,另一端接線性遞增計數器輸出。當線性計數器的計數值小于設定值設定值時輸出低電平,當計數值大于設定值時輸出高電平。 3.1 系統總體組成及框圖 直流電機控制電路構思如圖1所示,整個設計大致有4個模塊組成。

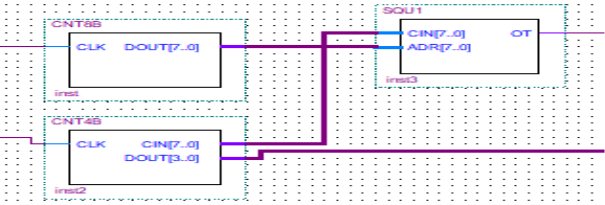

圖1 直流電機控制總系統圖 第一個模塊是PWM脈寬調制信號發生模塊。這個模塊也是用來控制轉速的模塊,通過設計兩個計數器的值,一個計數器的值是根據時鐘時刻改變的,改變的時鐘頻率來自鎖相環,這里把這個計數器叫做“時變計數器”,這是個8為計數器,輸出的數據相當于鋸齒波信號。另一個計數器的值是通過檔位按鍵來決定的,按鍵按下一次,計數器就相應的加一或者減一,這里把這個計數器叫做“設定值計數器”。這以為是個8為計數器,其中低4位設定為恒定1111,高4為由按鍵控制。這兩個計數模塊的值通過比較,就能輸出一個一定占空比的PWM波,通過設定計數器的值就能改變PWM波的占空比,這樣就控制了電機的轉速,于是也就通過手動按鍵控制電機的轉速。 第二個模塊是電機正反轉模塊。這個模塊是通過按鍵來控制的,當按下一次按鍵后,電機的轉向就改變一次。這個模塊我是通過用狀態機來實現正反轉狀態的改變,電機正轉是一個狀態,反轉是一個狀態,用狀態機書寫這個模塊會使電機正反轉模塊更加穩定。 第三個模塊是電機轉速測定顯示模塊。本課程是通過紅外光電測定轉速的,這個模塊的關鍵問題是產生一個1s的閘門時間,通過記下1s輸入的脈沖數并所存,然后譯碼通過數碼管顯示在硬件電路上。如圖3.1所示,外部脈沖通過消抖后,就直接進入1s輸入脈沖計數器,1s結束后,把記下的脈沖數所存起來,用譯碼管顯示出來。 第四個模塊是消抖模塊。消抖模塊是個必不可少的模塊。在本課程中,按鍵需要消抖,不消抖就會出現不穩定的現象,輸入脈沖也需要消抖,不消抖就出現技術不準。消抖的原理是,一個需要消抖的信號,和一個高頻率的脈沖信號,當消抖信號處于高電平時,高頻率信號同時開始計數,當計數達到預設的計數值時,高電平仍為高電平,則這個高電平信號有效,反之如果到達計數值時消抖信號變為低電平,則這個高電平無效。同理低電平一樣。 那么,由這4個模塊就構成了上圖的直流電機控制電路。 3.2 電機轉速控制模塊 3.2.1 設計思想及模塊原理圖 在用FPGA控制直流電機轉速時,其核心是改變每個PWM周期的占空比。在這里需要產生一個設定值計數器,一個時變計數器和一個數字比較器。原理圖如圖2所示。 具體地說,設定值計數器就是根據按鍵按下時選取的不同檔位,輸出一個不同的數值。本次設計速度分為十六檔,每增加一檔,轉速相應增加,十六檔時轉速達到最大。據此,首先要設計一個檔位調節模塊,當輸入不同的檔位數值時,要輸出一個計數值,這個數值規定了設定值計數器的輸出數值。當檔位增加時,設定值計數器的值相應增加,從而改變PWM信號占空比,使其占空比增大,電機轉速加快。設定值計數器的輸出加到比較器的一端,和時變計數器的數值進行比較。時變計數器的時鐘數值來自對鎖相環的分頻,時鐘數值能決定電機相應時間的快慢。 實驗室的電機一般都能達到100轉左右,所以計數器的位數不應低于7位,若更低的話,每改變一位數,對應的轉數還達不到一轉,這樣就不能對每一轉進行細分,也就無法精確控制電機的轉速。在設計中計數器位數設成了8位。 那么PWM信號的占空比具體是如何隨著檔位的不同而改變的呢?在前面已經設計好了一個設定值計數器和一個時變計數器,這兩個數值加在數字比較器輸入端進行比較,當設定值計數器的值大于時變計數器的值時,比較器輸出低電平;當設定值計數器的值小于時變計數器的值時,比較器輸出高電平。 因為設定值計數器的低四位恒為1,高四位由按鍵決定,當按鍵按下去一次,高四位就加1,因為這是四位,所以解釋了為什么了有十六個檔位。  圖 2 電機轉速模塊原理圖 圖 2 電機轉速模塊原理圖

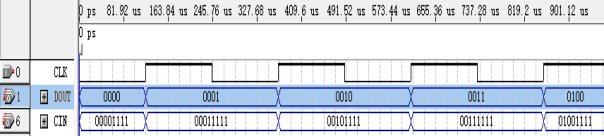

端口介紹: DOUT[7..0]:是8位時變計數器的輸出 CIN[7..0]:是8位設定值計數器輸出 DOUT[3..0]:是檔位的4位輸出 正好對應十六個檔位 OT:比較結果 3.2.2、轉速模塊VHDL設計語言 PWM脈寬調制信號:發生模塊當時變計數值小于設定值時輸出低電平,當時變計數值大于設定值時輸出高電平。 仿真結果如圖3 - USE IEEE.STD_LOGIC_1164.ALL;

- USE IEEE.STD_LOGIC_UNSIGNED.ALL;

- ENTITY SQU1 IS

- PORT ( CIN,ADR : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

- OT : OUT STD_LOGIC );

- END SQU1;

- ARCHITECTURE BHV OF SQU1 IS

- BEGIN

- PROCESS(CIN) BEGIN

- IF (ADR<CIN) THEN OT<='0';

- ELSE OT<='1'; END IF;

- END PROCESS;

- END BHV;

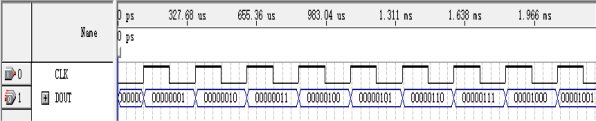

- 8為時變計數器:這個8為計數器是根據時鐘0計數的 仿真結果如圖4

- LIBRARY IEEE;

- USE IEEE.STD_LOGIC_1164.ALL;

- USE IEEE.STD_LOGIC_UNSIGNED.ALL;

- ENTITY CNT8B IS

- PORT (CLK : IN STD_LOGIC;

- DOUT: OUT STD_LOGIC_VECTOR(7 DOWNTO 0) );

- END CNT8B;

- ARCHITECTURE BHV OF CNT8B IS

- BEGIN

- PROCESS(CLK)

- VARIABLE CQ : STD_LOGIC_VECTOR(7 DOWNTO 0);

- BEGIN

- IF CLK'EVENT AND CLK = '1' THEN

- IF CQ<255 THEN --最大計數到255

- CQ := CQ + 1 ;

- ELSE CQ := (OTHERS=>'0') ;

- END IF;

- END IF;

- DOUT <= CQ;

- END PROCESS;

- END BHV;

- LIBRARY IEEE;

- USE IEEE.STD_LOGIC_1164.ALL;

- USE IEEE.STD_LOGIC_UNSIGNED.ALL;

- ENTITY CNT4B IS

- PORT (CLK : IN STD_LOGIC;

- CIN: OUT STD_LOGIC_VECTOR(7 DOWNTO 0); --8為設定值

- DOUT: OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ); --4位檔位信號

- END CNT4B;

- ARCHITECTURE BHV OF CNT4B IS

- SIGNAL CQ1 : STD_LOGIC_VECTOR(3 DOWNTO 0);

- BEGIN

- PROCESS(CLK)

- VARIABLE CQ : STD_LOGIC_VECTOR(3 DOWNTO 0);

- BEGIN

- CQ1 <="1111"; --低四位預設為1111

- IF CLK'EVENT AND CLK = '1' THEN --CLK上升沿到來時

- IF CQ<15 THEN

- CQ := CQ + 1 ;

- ELSE CQ := (OTHERS=>'0') ;

- END IF;

- END IF;

- DOUT <=CQ(3 DOWNTO 0);

- CIN <=CQ&CQ1;

- END PROCESS;

- END BHV;

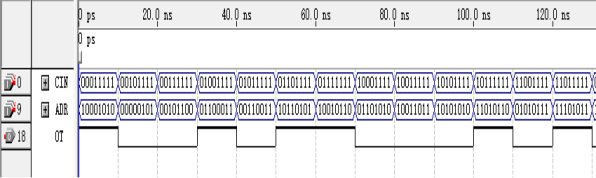

3.2.3、轉速模塊仿真結果 由仿真結果可以看出,確實滿足當時變計數值小于設定值時輸出低電平,當時變計數值大于設定值輸出高電平。

圖3 比較器仿真圖

圖4 時變計數器仿真圖

圖5 設定計數器仿真圖 3.3 正反轉向控制模塊 3.3.1 設計思想及原理圖 這個模塊就是按鍵來控制電機的轉向,正反向對應著2中狀態,因此可以通過按鍵來實現狀態的改變,每按一次狀態改變一次。當然這里應該還有一個使能控制,可以來啟動和暫停電機轉動。 工作原理 當按鍵K1第一次按下的時候,假定令M賦值給M0,則M1應賦值為低電平,當按鍵第二次按下的時候,則把M賦值給M1,則M0應賦值為低電平。如此反復的就實現了電機的正轉,反轉。當按鍵K3被按下時,則電機開始轉動,當K3再次被按下時,則電機停止轉動。設計原理圖如圖6 圖6 正反轉模塊原理圖 端口介紹 M :為比較器輸出的電平值 SL :按鍵K1的輸入端,用來控制正反轉、 M0,M1 :為電機的兩個輸入端。 K : 為按鍵K3的輸入端,用來控制電機的啟動和暫停

3.3.2 正反轉向模塊VHDL設計語言 仿真結果如圖7所示 - LIBRARY IEEE;

- USE IEEE.STD_LOGIC_1164.ALL;

- USE IEEE.STD_LOGIC_UNSIGNED.ALL;

- use ieee.std_logic_arith.all;

- ENTITY SLT IS --M為比較值

- PORT (SL, M, K : IN STD_LOGIC; --SL為正反轉按鍵

- m0, m1: OUT STD_LOGIC ); --K為啟動停止按鍵

- END SLT;

- ARCHITECTURE BHV OF SLT IS

- TYPE FSM_ST IS (S0,S1); --正反兩種狀態

- SIGNAL c_st, next_state: FSM_ST :=S0;

- BEGIN

- REG : PROCESS (SL)

- BEGIN

- IF SL='1'AND SL'EVENT THEN c_st <= next_state;--按鍵按下,次態變為現態

- END IF;

- END PROCESS REG ;

- COM : PROCESS (c_st, M) BEGIN

- IF K='1' THEN m0 <='0'; m1 <='0'; --如果有高電平,那么m0,m1都為0,則電機不轉

- ELSE

- CASE c_st IS

- WHEN S0 => m0 <= M; m1 <='0'; next_state <= S1;

- WHEN S1 => m1 <= M; m0 <='0'; next_state <= S0;

- END CASE;

- END IF;

- END PROCESS;

- END BHV;

程序分析,本模塊使用狀態機來實現電平的轉換,K為高電平時,輸出為0電機不動,低電平時,初始狀態為S0,當SL有上升沿變化的時候,初態就轉為次態。 3.3.3 正反轉向模塊仿真結果 根據圖7 可知,當檢測SL第一次上升沿變化的時候,M1的就和M相同,同時MO就為低電平,當檢測SL第二次上升沿變化的時候,M0的就和M相同,同時M1就為低電平,其后的過程中這兩種狀態就交替進行。當檢測到K為高電平時,M1和M2都為低電平。 圖7 正反轉向模塊仿真圖

3.4、轉速測定及顯示模塊 3.4.1 設計思想及模塊圖 設計這個模塊的關鍵問題是產生一個1s的閘門信號,記下1s鐘輸入的脈沖數,鎖存,然后譯碼輸出到硬件電路上。設計原理圖如圖8所示。 圖8 轉速測定模塊原理圖 端口介紹: C1: 為鎖相環輸出5MHz C0: 為鎖相環輸出4096Hz KIN: 為待測頻率 LEDA LEDB:為所存信號輸出

3.4.2轉速測定模塊CHDL設計語言 (1)分頻模塊:通過對鎖相環輸出的4096Hz時鐘進行分頻以獲得1 Hz時鐘,為頻率計控制模塊TF_CTRL提供1 S的閘門時間。程序如下: - LIBRARY IEEE ;

- USE IEEE.STD_LOGIC_1164.ALL;

- USE IEEE.STD_LOGIC_UNSIGNED.ALL;

- ENTITY CNT IS

- PORT(CLOCK : IN STD_LOGIC ;COUT : OUT STD_LOGIC);

- END ;

- ARCHITECTURE bhv OF CNT IS

- SIGNAL C1,C2 : STD_LOGIC_VECTOR(8 DOWNTO 0) ;

- SIGNAL M1,M2 : STD_LOGIC ;

- BEGIN

- PROCESS(CLOCK,C1) BEGIN

- IF RISING_EDGE(CLOCK) THEN

- IF (C1="111111111") THEN C1<="000000000"; ELSE C1<=C1+1; END IF;

- IF (C1="000000001") THEN M1<=NOT M1; ELSIF (C1="100000000") THEN M1<=NOT M1;

- END IF;END IF;

- END PROCESS;

- PROCESS (CLOCK,C2) BEGIN

- IF FALLING_EDGE(CLOCK) THEN

- IF(C2="111111111") THEN C2<="000000000"; ELSE C2<=C2+1;END IF;

- IF(C2="000000001") THEN M2<=NOT M2 ; ELSIF (C2="100000000") THEN M2<=NOT M2;

- END IF; END IF;

- END PROCESS;

- COUT<=M1 OR M2;

- END bhv;

- 頻率計控制模塊:這個模塊時產生測頻控制信號的,TF_CTRL計數使能信號CNT_EN能產生一個1s脈寬的周期信號,并對頻率計中的8位二進制電機脈沖計數器CNT10D的ENABL使能端進行同步控制,同時產生計數所存信號LOCK。程序如下:

- LIBRARY IEEE;

- USE IEEE.STD_LOGIC_1164.ALL;

- USE IEEE.STD_LOGIC_UNSIGNED.ALL;

- ENTITY TF_CTRL IS

- PORT (CLK1 : IN STD_LOGIC; -- 1Hz

- CNT_EN : OUT STD_LOGIC; -- 計數器時鐘使能

- CLR : OUT STD_LOGIC; -- 計數器清零

- LOCK : OUT STD_LOGIC ); -- 輸出鎖存信號

- END TF_CTRL;

- ARCHITECTURE behav OF TF_CTRL IS

- SIGNAL Div2CLK : STD_LOGIC;

- BEGIN

- PROCESS( CLK1 )

- BEGIN

- IF CLK1'EVENT AND CLK1 = '1' THEN

- Div2CLK <= NOT Div2CLK;

- END IF;

- END PROCESS;

- PROCESS (CLK1, Div2CLK)

- BEGIN

- IF CLK1='0' AND Div2CLK='0' THEN CLR<='1';-- 產生計數器清零信號

- ELSE CLR <= '0'; END IF;

- END PROCESS;

- LOCK <= NOT Div2CLK; CNT_EN <= Div2CLK;

- END behav;

(3)電機脈沖計數器:當ENABL高電平時允許計數;低電平時停止計數,并保持其所計的脈沖數。 - LIBRARY IEEE; --8位計數器

- USE IEEE.STD_LOGIC_1164.ALL;

- USE IEEE.STD_LOGIC_UNSIGNED.ALL;

- ENTITY CNT10D IS

- PORT (CLK : IN STD_LOGIC; -- 時鐘信號

- CLR : IN STD_LOGIC; -- 清零信號

- ENABL : IN STD_LOGIC; -- 計數使能信號

- COUT : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

- DOUT1 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

- DOUT2 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0)); -- 計數結果

- END CNT10D;

- ARCHITECTURE behav OF CNT10D IS

- SIGNAL CQ2 : STD_LOGIC_VECTOR(3 DOWNTO 0);

- SIGNAL CQ3 : STD_LOGIC_VECTOR(3 DOWNTO 0);

- BEGIN

- PROCESS(CLK, CLR, ENABL)

- BEGIN

- IF CLR = '1'

- THEN CQ2 <= (OTHERS=>'0'); CQ3 <= (OTHERS=>'0'); -- 清零

- ELSIF CLK'EVENT AND CLK = '1' THEN

- IF ENABL = '1' THEN

- IF CQ2>8 THEN CQ3<=CQ3+1; CQ2(3 DOWNTO 0)<="0000";

- ELSE CQ2 <=CQ2+1;

- END IF;

- END IF;

- END IF;

- END PROCESS;

- COUT <= CQ3&CQ2;

- DOUT1 <=CQ2;

- DOUT2 <=CQ3;

- END behav;

(4)鎖存模塊:鎖存信號LOAD的上升沿將計數器在前1秒鐘的計數 值鎖存進鎖存器LOCK8中,設置鎖存器的好處是數據顯示穩定,不會由于周期性的清0信號而不斷閃爍。程序如下: - LIBRARY IEEE; --8位鎖存器

- USE IEEE.STD_LOGIC_1164.ALL;

- ENTITY LOCK8 IS

- PORT ( LK : IN STD_LOGIC;

- D : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

- LEDA: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

- LEDB: OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

- END LOCK8;

- ARCHITECTURE behav OF LOCK8 IS

- BEGIN

- PROCESS(LK, D)

- BEGIN

- IF LK'EVENT AND LK = '1' THEN LEDA <= D(7 DOWNTO 4); LEDB <= D(3 DOWNTO 0);

- END IF;

- END PROCESS;

- END behav;

3.4.3、 轉速測定仿真結果 圖9 分頻模塊仿真結果 圖10 頻率計控制模塊仿真結果 圖11 電機脈沖計數模塊仿結果

圖12計數所存模塊仿真結果 3.5、 消抖模塊 3.5.1、設計思想及原理圖 為避免按鍵抖動和光耦模塊產生干擾信號,按鍵模塊和脈沖前應接入消抖模塊ERZP。此消抖模塊采用的是定時方式去毛刺。在本設計中,其中CLK的信號頻率為5MHZ,高電平持續的時間當CLK的計數到12的時候,即為有效高電平,低電平持續的時間當CLK的計數到7的時候,即為有效低電平。原理圖如圖13所示 圖13 消抖模塊原理圖 端口介紹: CLK: 消抖模塊的時鐘 KIN: 輸入的信號 KOUT: 消抖后的信號 3.5.2、消抖模塊VHDL設計語言 - LIBRARY IEEE;

- USE IEEE.STD_LOGIC_1164.ALL;

- USE IEEE.STD_LOGIC_UNSIGNED.ALL;

- ENTITY ERZP IS

- PORT(CLK,KIN : IN STD_LOGIC;

- KOUT : OUT STD_LOGIC );

- END;

- ARCHITECTURE BHV OF ERZP IS

- SIGNAL KL,KH : STD_LOGIC_VECTOR(3 DOWNTO 0);

- BEGIN

- PROCESS(CLK,KIN,KL,KH ) BEGIN

- IF CLK'EVENT AND CLK = '1' THEN

- IF(KIN='0') THEN KL<=KL+1;

- ELSE KL<="0000"; END IF;

- IF(KIN='1') THEN KH<=KH+1;

- ELSE KH<="0000"; END IF;

- IF(KH>"0101") THEN KOUT<='1';

- ELSIF (KL>"0101") THEN KOUT<='0';

- END IF; END IF;

- END PROCESS;

- END;

3.5.3 消抖模塊仿真結果 圖14 消抖模塊仿真結果

word格式的完整設計報告51黑下載地址:

基于VHDL的直流電機控制系統.7z

(113.49 KB, 下載次數: 80)

基于VHDL的直流電機控制系統.7z

(113.49 KB, 下載次數: 80)

2018-1-17 02:42 上傳

點擊文件名下載附件

文件有點大 分成兩個包了 下載積分: 黑幣 -5

本設計的完整的源碼下載地址:

http://www.zg4o1577.cn/bbs/dpj-105339-1.html

|