一 設計目的1)加深對數字電子知識的理解,鞏固本學期所學的知識。

2)熟悉集成元器件的選擇和集成電路芯片的邏輯功能及其使用方法。

3)掌握采用時序電路設計方法實現課題要求

4)掌握各芯片的邏輯功能及使用方法。

5)了解數字顯示電子鐘的組成及工作原理。

6)熟悉數字鐘的設計與制作。

二 設計任務1)時鐘的“時”用兩位顯示,即為24小時進制。

2)時鐘的“分”、“秒”各用兩位00——59顯示,為六十進制計數。

3)有校時功能,可以分別對時及分秒進行單獨校時,使其校正到標準時間。

4)系統有鬧鐘功能,可以進行5秒蜂鳴報時。

5)為了保證計時的穩定及準確須由晶體振蕩器提供表針時間基準信號。

三 設計要求

- 時鐘的“時”要求用兩位顯示;上、下午用發光管作為標志;

- 時鐘的“分”、“秒”要求各用兩位顯示;

- 整個系統要有校時部分(可以手動,也可以自動),校時時不能產生進位;

4)系統要有鬧鐘部分,聲音要響5秒(可以是一聲一聲的響,也可以連續響)。

四 數字時鐘原理框圖

該系統的工作原理是:

- 由石英晶體多諧振蕩器和分頻器產生1HZ標準秒脈沖。

- “秒電路”、“分電路”均為00—59的六十進制計數、譯碼、顯示電路;

- “時電路”為00—23的二十四進制計數、譯碼、顯示電路。

五 電路設計

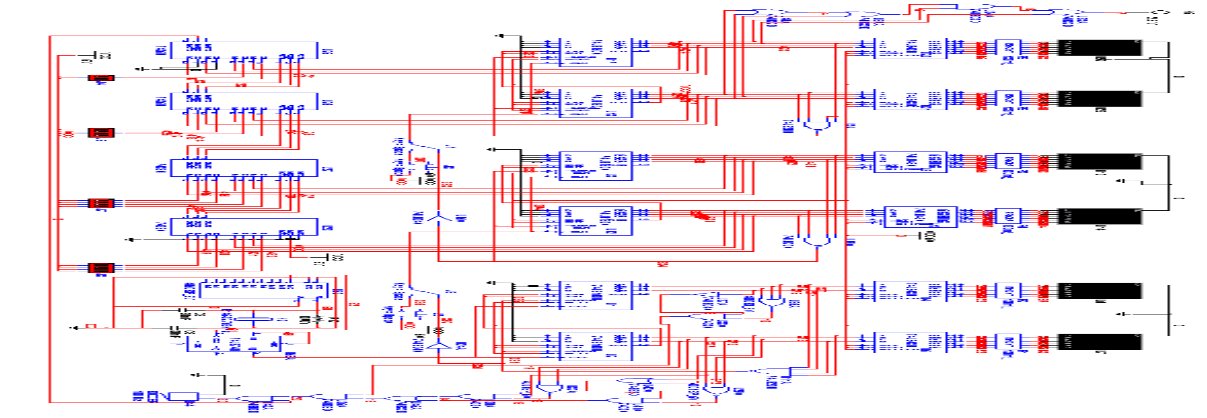

整體電路設計:

在進行電路設計時,考慮到整體集成電路的承受能力,我們在選擇器件時盡可能的選用同種型號的器件。在進行芯片選擇時我們選用TTL集成芯片,在確保功能完整的前提下,整個電路盡可能的少用芯片。

5.1 秒脈沖電路設計

它是數字電子鐘的核心部分,它的精度和穩定度決定于數字中的質量。通常晶體振蕩器發出的脈沖經過整形、分頻獲得1Hz的秒脈沖。

多諧振蕩器電路與分頻電路如下圖所示。多諧振蕩器與分頻電路為計數器提供計數脈沖和為計數器提供校時脈沖。

圖1晶體振蕩器電路與分頻電路

可得多諧振蕩器的頻率為1Hz,R1為10M歐,C1為15~20pF,C2為5~30pF

使多諧振蕩器產生頻率為1Hz的方波信號。

5.2 晶體振蕩器工作原理

晶體振蕩器產生32.768K赫茲的頻率,經過十五分頻電路后產生1赫茲的方波,進而送到74ls160進行計數。十五分頻電路是有一片CD4060在加上一片74ls74產生。其中CD4060是14分頻,74ls74是一個D觸發器,在這里相當于一個二分頻。

圖二 D觸發器二分頻示意圖

圖3 4060引腳圖

5.3時、分、秒計數器電路

一般采用10進制計數器來實現時間計數單元計數功能,要實現這一要求,可選用的中規模集成計數器較多,這里推薦74LS160。

圖4 74ls60

如果采用反饋清零方式時在計數一遍后進入重新計數時時間間隔不是一個時間脈沖而是兩個,會造成計數不準,例如十進制從0000—0001—0010—……1001—1010(此狀態雖不會顯示但已經出來)—0000。 故現在采用反饋置數法實現,以十進制為例0000——0001——0010——……1001 ——0000(不會出現1010狀態,故很準) 其接法電路如圖5圖6。

秒信號經秒計數器、分計數器、時計數器之后。分別得到顯示電路,以便實現用數字顯示時、分、秒的要求。“秒”和“分”計數器應為六十進制,而“時”計數器應為二十四進制。

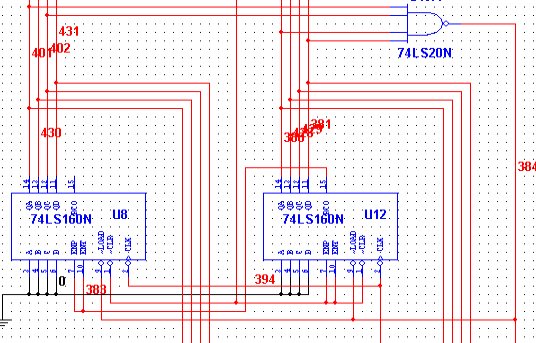

(1) 六十進制計數器。它由兩塊中規模集成十進制計數器74LS160,一塊組成十進制,另一塊組成六進制。采用置數法時,當高位出現0101狀態,低位為1001狀態,即計到59(第60個脈沖),如圖5所示六十進制計數器。

(2) 二十四進制計數器。它由兩塊中規模集成十進制計數器74LS160構成。當高位出現0010狀態,低位為0011狀態,即計到第24個來自“分”計數器的進位信號時,產生反饋置數信號,如圖6所示為二十四進制計數器。

圖 5兩塊74LS160構成的六十進制計數器

采用置數法74LS160 的3、4、5、6引腳接地,低位的7、10、1引腳和高位1引腳接高電平,高位7、10引腳接低位15引腳。其14—11引腳接顯示譯碼器的7、1、2、6引腳。

圖6兩塊74LS160構成的二十四進制計數器

5.4 譯碼顯示電路

選用器件時應當注意譯碼器和顯示器件相互配合。一是驅動功率要足夠大,二是邏輯電平要匹配秒計數器、分計數器、和時計數器的計數分別輸送給各自的顯示譯碼器74LS48,在數送給各自的數碼管,顯示出時、分、秒的計時。電路如圖7所示為計數、譯碼顯示電路。

圖7譯碼顯示電路

圖8 74LS48引腳圖

這里采用74LS48作為顯示譯碼器,A0~A3接74LS160的QA~QD端3、 4、 5引腳都接高電平,9~15端接七段數碼管。七段數碼管引腳圖如下圖(共陰極)

圖9 七段數碼管引腳圖

5.5校時電路

在剛接通電源或者時鐘走時出現誤差時,則需要進行時間的校準。因此,應截斷時分的直接計數通路,并采用正常計數信號與校時信號可以切換的電路接入其中。故我們設計了對時、分、秒各自校時的電路。設計原理是:將74ls160的兩個使能端接在一起后接到單刀雙擲開關的公共端,再將進位端和高電平分別接到另外兩端。當開關按下時接入高電平,反之便會接到進位端。

圖10 校時部分電路

5.6 定時電路設計

每當數字時鐘計時與所設定的時間相同時開始發出5s的響聲,響聲是從第1s開始到第6s,響聲的頻率一樣,即所發出的聲音是一樣的沒有變化。定時電路即邏輯見下圖。

圖11 定時響5s真值表

由卡諾圖可以計算出定時響5s的邏輯,其邏輯電路連接見下圖

圖12 響5s邏輯電路連接

鬧鐘電路的工作原理是利用秒的計數器控制其響5s,控制5s的電路與控制時間相等的電路用一個與門連接就可以構成定時電路。控制時間的電路如下圖所示

圖13 定時電路

5.7 顯示上下午電路

顯示上下午電路的工作原理是當小時模塊的計數器跳過12的時候,指示上下午的發光二極管通過邏輯電路的輸出而變亮,而且其亮將一直持續到23:59,控制顯示上下午的邏輯真值表如下變所示:

圖14 顯示上下午真值表

根據真值表用卡諾圖可以得到顯示上下午的邏輯表達式,根據邏輯表達式用TTL門電路可以電路連線圖如下:

圖15 顯示上下午邏輯電路

六 元器件清單

由multisim生成的元器件清單如下所示:

| | | |

| | | |

| | | |

| | | |

| | | |

| | | |

| | | |

| | | |

| | | |

| | | |

| | | |

| | | |

| 1 K  電阻 | |

|

| 2.2 K  滑動變阻器 | |

|

| 200  電阻 | |

|

| | |

|

| 10 K  電阻 | |

|

圖16 multisim輸出器件

七 總電路圖

八總結與收獲

八總結與收獲

十多天的數字電子課程設計馬上就要畫上圓滿的句號,在這期間的收獲很多,高興過沮喪過,當電路終于能夠符合設計指標和要求的時候,心情無比的舒暢。但是mutisim本身的一個缺陷使得無法在仿真的時候使用晶振加上4060產生1赫茲的方波,但是在現實的情況下,這樣是完全能夠產生的。所以在做仿真的時候就用了555多諧振蕩電路來代替,以檢驗其他功能模塊是否符合設計的要求。在這次課設期間是我更加熟練的掌握了仿真軟件multisim的一些用法,原來沒有發現的功能在這次做課設的時候學會了,我想這是一大收獲。另外這次課設也讓我更加了解一些元器件的功能如74ls160,74ls40以及一些門電路邏輯功能的算法。