�(xi��ng)Ŀ�ֹ���

1���I(l��ng)�ϡ����ӡ����ӵij��͡�

2�����ӵ��b�ӡ��{(di��o)ԇ��

3������ľ���(xi��)�c����

4���Y�ϵ��ռ��c��������(sh��)�(y��n)��(b��o)�濂�Y(ji��)��

һ���n�}���w�����c��(sh��)ʩ��(sh��)Ӗ(x��n)�r(sh��)�g����ʮ���ܵ���ʮ���ܣ�

��ʮ�����ռ����ϣ����ӳ��ͣ�

��ʮ���܌�(xi��)����

��ʮ�����{(di��o)ԇ����(xi��)��(sh��)�(y��n)��(b��o)�棻

��ʮ���ܴ��q��

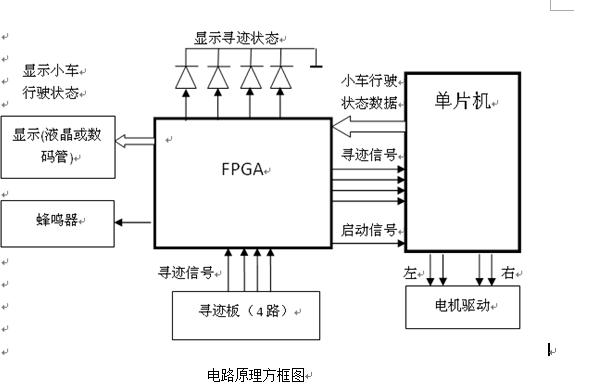

�����n�}Ŀ��(bi��o)��1�����ջ���C51��Ƭ�C(j��)��FPGAģ��(sh��)���Ӳ��ϵ�y(t��ng)�O(sh��)Ӌ(j��)�ͳ����O(sh��)Ӌ(j��)��

2���W(xu��)��(hu��)������Ӯa(ch��n)Ʒ�Ĺ����O(sh��)Ӌ(j��)�c�΄�(w��)���������M(j��n)��С����Ӯa(ch��n)Ʒ�������O(sh��)Ӌ(j��)��

3��ͨ�^(gu��)����ѭ�EС܇(ch��)ܛ��ϵ�y(t��ng)�O(sh��)Ӌ(j��)�����C(j��)�{(di��o)ԇ���O(sh��)Ӌ(j��)��ܛ�����ܲ������{(di��o)ԇ��

4�����B(y��ng)�F(tu��n)�(du��)������������ͨ��������(chu��ng)�������Լ��M��������

�����n�}Ҫ�� 1.����Ҫ��

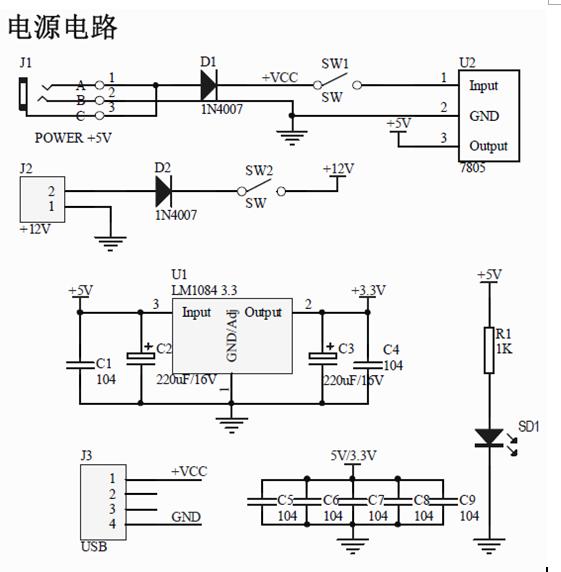

��1��ݔ���Դ��12V��

��2������ǰ�M(j��n)�����D(zhu��n)�����D(zhu��n)���Ԅ�(d��ng)ͣ܇(ch��)�Ĺ��ܣ�

��3���ܸ���(j��)�ṩ��8��ѭ�E·���M(j��n)�Ќ��E��

2.�l(f��)�]����

��1�����I����(d��ng)�� ��2���D(zhu��n)����ʾ�� ��3���Q̖(h��o)��ʾ�� ժҪ����ѭ�EС܇(ch��)��AT89C51��Ƭ�C(j��)����ƺ��ģ�����ֱ��늙C(j��)���Դ�·�Լ������·��(g��u)�ɡ�ϵ�y(t��ng)AT89C51ͨ�^(gu��)I/O����С܇(ch��)ǰ�M(j��n)���D(zhu��n)���E�ɹ������M�ɹ���̽�y(c��)����ɡ�

�ġ�С܇(ch��)ѭ�Eԭ���� ������ѭ�EС܇(ch��)��AT89C51��Ƭ�C(j��)����Ŀ���ϵ�y(t��ng)���ù������M�ɹ���̽�y(c��)��������������ֵ���Ը��S��?ch��)��h(hu��n)���⾀��׃����׃������(d��ng)�⾀���䵽������r(sh��)���⾀���䏊(qi��ng)�ң��⾀���䵽�ھ�����r(sh��)���⾀�����^������˹����ڰ��ͺھ������Ϸ��r(sh��)����ֵ��(hu��)�l(f��)�����@��׃��������ֵ��׃��ֵ��(j��ng)�^(gu��)���^���Ϳ���ݔ���ߵ��ƽ����(j��ng)��Ƭ�C(j��)̎����ݔ��������̖(h��o)�o늙C(j��)�(q��)��(d��ng)�·����(l��i)����늙C(j��)���(q��)��(d��ng)����������(g��)�^(gu��)�̲���Ҫ�ˁ�(l��i)���ƣ���(d��ng)��ͬ�Ĺ������z�y(c��)���ھ��r(sh��)��늙C(j��)��(hu��)�в�ͬ���D(zhu��n)��(d��ng)���Ķ���(sh��)�F(xi��n)�˺�(ji��n)�ε����ܿ��ơ�

�塢Ӳ���O(sh��)Ӌ(j��)1�����w�O(sh��)Ӌ(j��)

�·ԭ������D

2����Ƭ�C(j��)����ϵ�y(t��ng)ģ�K�O(sh��)Ӌ(j��)

�҂�����AT89C52Ƭ�C(j��)��Сϵ�y(t��ng)�·������(g��)ϵ�y(t��ng)�Ŀ���ϵ�y(t��ng)����ؓ(f��)؟(z��)����С܇(ch��)���\(y��n)��(d��ng)��B(t��i)��

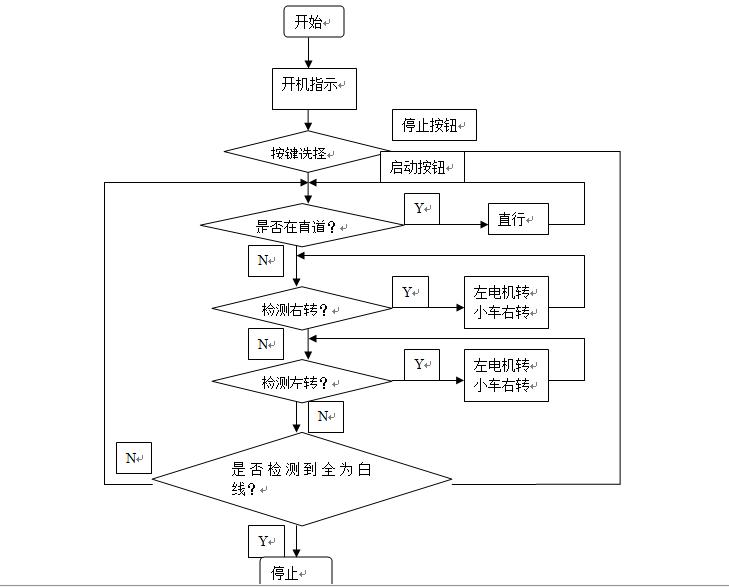

��1������(d��ng)С܇(ch��) С܇(ch��)�ڽ��յ�FPGA���^(gu��)��(l��i)�Ć���(d��ng)ָ����xȡ���E��̖(h��o)������(j��)���E��̖(h��o)�_��С܇(ch��)���\(y��n)�Р�B(t��i)����С܇(ch��)���\(y��n)�Р�B(t��i)����FPGA��ͬ�r(sh��)����(j��)����(y��ng)�㷨���(q��)��(d��ng)С܇(ch��)������늙C(j��)ǰ�M(j��n)�� ��2������ǰ�M(j��n) ��(d��ng)���E�����g�ɂ�(g��)�������z�y(c��)���ھ�������һ��(g��)�z�y(c��)���ھ���ɂ�(g��)ͬ�r(sh��)�z�y(c��)���ھ�����С܇(ch��)������ǰ�M(j��n)�� ��3�� ��Տ� ��(d��ng)����˵Ă������z�y(c��)���ھ����Ҷ�3��(g��)�������z�y(c��)����ɫ�r(sh��)��С܇(ch��)��(y��ng)��Տ��� ��4�� �ҹՏ� ��(d��ng)���Ҷ˵Ă������z�y(c��)���ھ������3��(g��)�������z�y(c��)����ɫ�r(sh��)��С܇(ch��)��(y��ng)�ҹՏ��� ��5������ ��(d��ng)4��(g��)���������z�y(c��)����ɫ��С܇(ch��)���ˡ� ��6�� ͣ܇(ch��) ��(d��ng)4��(g��)������ͬ�r(sh��)�B�m(x��)��Ιz�y(c��)���ھ������B�m(x��)3�Σ���С܇(ch��)ͣ܇(ch��)��С܇(ch��)ͣ܇(ch��)�l(f��)��һ��(g��)ͣ܇(ch��)��(bi��o)־��̖(h��o)�ͽoFPGA�� 3�����Eģ�K���O(sh��)Ӌ(j��)

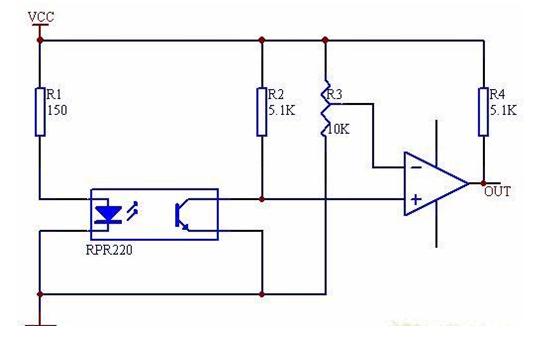

���E�����^(gu��)��(l��i)��4·�z�y(c��)��̖(h��o)�͵�FPGA�壬F(xi��n)PGA����4·��̖(h��o)�ͳ���4��(g��)LED���@ʾ��B(t��i)���z�y(c��)���ھ�������t�磩��ͬ�r(sh��)����4·��̖(h��o)�͵���Ƭ�C(j��)��

4���@ʾģ�K���O(sh��)Ӌ(j��)

�҂����õ��ǔ�(sh��)�a���@ʾ�� ��1�� С܇(ch��)����(d��ng) С܇(ch��)����(d��ng)�r(sh��)���@ʾ��1���� ��2��С܇(ch��)��� С܇(ch��)��Օr(sh��)���@ʾ��2���� ��3�� С܇(ch��)�ҹ� С܇(ch��)�ҹՕr(sh��)���@ʾ��3���� ��4��С܇(ch��)ǰ�M(j��n) С܇(ch��)ǰ�M(j��n)�r(sh��)���@ʾ��4���� ��5�� С܇(ch��)���� С܇(ch��)���˕r(sh��)���@ʾ��5���� ��6�� ͣ܇(ch��) С܇(ch��)ͣ܇(ch��)�r(sh��)���@ʾ��6����

5����ʾ��ģ�K���O(sh��)Ӌ(j��)

(1) С܇(ch��)����(d��ng) С܇(ch��)����(d��ng)ǰ�l(f��)��3��ཡ�ཡ�ཡ���������ʾ���Y(ji��)����F(xi��n)PGA�l(f��)��һ��(g��)����(d��ng)��̖(h��o)�o��Ƭ�C(j��)���Ķ�����(d��ng)С܇(ch��)�� (2) ͣ܇(ch��) С܇(ch��)ͣ܇(ch��)�r(sh��)��F(xi��n)PGA����һ������(l��)������(l��)���ŽY(ji��)������ʾС܇(ch��)������΄�(w��)�� 6��FPGAģ�K���O(sh��)Ӌ(j��) ��1�� ���E��̖(h��o)̎�� ���E���^(gu��)��(l��i)����̖(h��o)һ�����͵�LED���@ʾ���E��B(t��i)����һ����Ҫ������̖(h��o)�͵���Ƭ�C(j��)ȥ̎���� ��2�� С܇(ch��)��B(t��i)�@ʾ ��С܇(ch��)���\(y��n)�Р�B(t��i)�Ô�(sh��)�a���@ʾ����(l��i)�� ��3�� ��ʾ�� С܇(ch��)����(d��ng)ǰ���l(f��)��3��ʾ����С܇(ch��)ͣ܇(ch��)��һ������(l��)�� ��4�� С܇(ch��)����(d��ng) С܇(ch��)�ڰl(f��)��3��ʾ����FPGA�l(f��)��һ��(g��)�_(k��i)ʼָ��o��Ƭ�C(j��)���Ķ�����(d��ng)С܇(ch��)ǰ�M(j��n)�� ��5�� С܇(ch��)ͣ܇(ch��) С܇(ch��)ͣ܇(ch��)��FPGA���յ���Ƭ�C(j��)��ͣ܇(ch��)ָ��_(k��i)ʼ��������(l��)��ֱ��һ������(l��)�����ꮅ�� 7��늙C(j��)�(q��)��(d��ng)ģ�K�O(sh��)Ӌ(j��) �҂��x��늙C(j��)�(q��)��(d��ng)оƬL298N��L298N��ΉK�����·����늉������������ͨ���(q��)��(d��ng)����ֱ���nj�(du��)늙C(j��)�M(j��n)�п��ƣ��o(w��)����x�·��ͨ�^(gu��)��Ƭ�C(j��)��I/Oݔ���׃���ƶ˵��ƽ�������Ԍ�(du��)늙C(j��)�M(j��n)�������D(zhu��n)��ֹͣ�IJ������dz����㣬���ܝM��ֱ���p��늙C(j��)�Ĵ����Ҫ���{(di��o)ԇ�r(sh��)�������ϱ����ó���ݔ�댦(du��)��(y��ng)�Ĵaֵ���܉�?q��)��F(xi��n)��(du��)��(y��ng)�Ą�(d��ng)�����±�����ʹ�ܡ�ݔ�����_��ݔ�����_��߉�P(gu��n)ϵ��

����ܛ���O(sh��)Ӌ(j��) ����С܇(ch��)�Ŀ���ʹ��ATMEL��˾��AT89C51��Ƭ�C(j��)�������O(sh��)Ӌ(j��)�ϣ�ͨ�^(gu��)��(du��)�z�y(c��)��̖(h��o)�IJɼ���������(sh��)��(j��)���Д��С܇(ch��)���\(y��n)�Р�B(t��i)���M(j��n)������С܇(ch��)�غھ���

���������̈D

��늙C(j��)�D(zhu��n) С܇(ch��)���D(zhu��n)

|

��늙C(j��)�D(zhu��n) С܇(ch��)���D(zhu��n)

|

�ߡ������O(sh��)Ӌ(j��)��1����Ƭ�C(j��)C�Z(y��)�Գ����O(sh��)Ӌ(j��)�� #include<reg51.h> #define uchar unsigned char #define uint unsigned int unsigned char w0=0; unsigned char w1=0; unsigned char t=0; sbit RT1=P1^0; sbit RT2=P1^1; sbit LT1=P1^2; sbit LT2=P1^3; sbit IN1=P0^0; sbit IN2=P0^1; sbit IN3=P0^2; sbit IN4=P0^3; sbit ENA=P0^4; sbit ENB=P0^5; void delay(int z) { while(z--); } void init() { TMOD=0x01; TH0=(65536-100)/256; TL0=(65536-100)%256; EA=1; ET0=1; TR0=1; } void time0()interrupt 1 { if(t<w0) ENA=1; else ENA=0; if(t<w1) ENB=1; else ENB=0; t++; if(t>=100) {t=0;} } void qianjin() { w0=30; w1=30; } void turn_left1() {w0=0; w1=50; } void turn_left2() {w0=0; w1=60; } void turn_right1() {w0=50; w1=0; } void turn_right2() {w0=60; w1=0; } void xunji() { uchar flag; if((RT1==1)&&(RT2==1)&&(LT1==1)&&(LT2==1)) {flag=0;}//ֱ�� else if((RT1==0)&&(RT2==1)&&(LT1==1)&&(LT2==1)) {flag=1;}//���D(zhu��n)1 else if((RT1==0)&&(RT2==0)&&(LT1==1)&&(LT2==1)) {flag=2;}//2 else if((RT1=��1)&&(RT2==1)&&(LT1==0)&&(LT2==1)) {flag=3;}//���D(zhu��n)1 else if((RT1==1)&&(RT2==1)&&(LT1==0)&&(LT2==0)) {flag=4;}//2 switch(flag) { case0:qianjin(); break; case1:turn_righ1t(); break; case2:turn_right2(); break; case3:turn_left1(); break; case4:turn_left2(); break; } } void main() {init(); w0=30; w1=30; while(1) { IN1=1; IN2=0; IN3=1; IN4=0; ENA=1; ENB=1; while(1) {xunji(); } } } 2��ѭ�E�����O(sh��)Ӌ(j��)�� #include<reg52.h> #define uchar unsigned char #define uint unsigned int uint tt=0,flag=0,flag1=0,flag2=0,num=0; sbit in1=P2^0; sbit in2=P2^1; sbit in3=P2^2; sbit in4=P2^3; sbit a=P0^0; sbit b=P0^1; sbit c=P0^2; sbit d=P0^3; sbit ENA=P2^4; sbit ENB=P2^5; sbit control=P1^0; sbit FPGA1=P1^1; sbit FPGA2=P1^2; sbit FPGA3=P1^3; sbit FPGA4=P1^4; sbit buzzer=P1^5; void init_time(); void delay(unsigned int z); void Turn_left() { in1=0; in2=0; in3=1; in4=0; } void Turn_right() { in1=1; in2=0; in3=0; in4=0; } void Go() { in1=1; in2=0; in3=1; in4=0; } void Back() { in1=0; in2=1; in3=0; in4=1; } void Stop() { in1=1; in2=1; in3=1; in4=1; } void Go_left_right() { in1=1; in2=0; in3=0; in4=1; } /*void Go_right() { in1=0; in2=1; in3=0; in4=0; }*/ void FPGA_display() { FPGA1=a; FPGA2=b; FPGA3=c; FPGA4=d; } void FPGA_display1() { FPGA1=a&0; FPGA2=b|1; FPGA3=c|1; FPGA4=d&0; } void main() { uint i=10; init_time(); delay(2); control=0; buzzer=1; //P0=0xff; //P1=0xff; //delay(2000); //delay(2000); //Go(); //delay(100); while(!control) { delay(2); FPGA_display1(); //delay(200); //delay(200); } if(control==1) { delay(300); Go(); delay(100); Go(); delay(100); while(2) { if((a==0&&b==0&&c==1&&d==1)||(a==0&&b==0&&c==0&&d==1)||(a==0&&b==0&&c==1&&d==0)) Turn_right();FPGA_display(); delay(30); if((a==1&&b==1&&c==0&&d==0)||(a==1&&b==0&&c==0&&d==0)||(a==0&&b==1&&c==0&&d==0)) Turn_left();FPGA_display(); delay(30); if(a==0&&b==1&&c==1&&d==0) Go();FPGA_display(); delay(9); if(a==0&&b==0&&c==0&&d==0) { Back();FPGA_display(); delay(10); Back(); delay(10); Back(); flag1++; flag2++; if(flag2==13) flag2=0; if(flag1==8) flag1=0; } if(flag1==7) { flag1=0; Go(); delay(60); Go(); delay(60); Go(); delay(60); Go(); delay(60); } delay(5); if(a==1&&b==1&&c==1&&d==1) { flag++; if(flag==12) flag=4; } if(flag==1||flag==2||flag==3) { Stop(); //Turn_right(); delay(100); Stop(); delay(100); Back(); delay(100); Back(); delay(100); Back(); delay(300); Back(); delay(300); Turn_right(); delay(500); Turn_right(); delay(500); Turn_right(); delay(500); //Back(); //delay(200); //Turn_left(); Turn_right(); delay(500); //Turn_left(); Turn_right(); delay(400); //Turn_left(); Turn_right(); delay(300); //Turn_left(); Turn_right(); delay(200); flag=4; Go(); delay(10); } //if(flag>=2) //{ // Go(); // delay(50); //} //Go(); //Back(); } } } void delay(unsigned int z) { unsigned int i,j; for(i=z;i>0;i--) for(j=110;j>0;j--); } void init_time() { TMOD=0x01; TH0=(65536-25000)/256; TL0=(65536-25000)%256; EA=1; TR0=1; ET0=1; } void time_0(void) interrupt 1 { TH0=(65536-20000)/256; TL0=(65536-20000)%256; tt++; num++; if(num==500) { num=0; buzzer=0; } //delay(1); if(tt>=9) tt=0; if(tt<=4) { ENA=1; ENB=1; } else { ENA=0; ENB=0; } } |

����TQQ:125739409;���g(sh��)����QQȺ281945664

����TQQ:125739409;���g(sh��)����QQȺ281945664