里面有sdram的時序

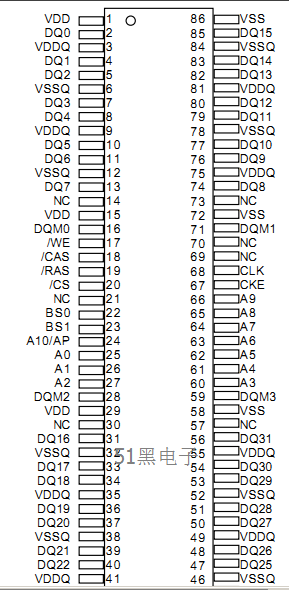

em638325引腳圖:

Overview

The EM638325 SDRAM is a high-speed CMOS synchronous DRAM containing 64 Mbits. It is internally configured

as a quad 512K x 32 DRAM with a synchronous interface (all signals are registered on the positive edge of the clock

signal, CLK). Each of the 512K x 32 bit banks is organized as 2048 rows by 256 columns by 32 bits. Read and write

accesses to the SDRAM are burst oriented; accesses start at a selected location and continue for a programmed number

of locations in a programmed sequence. Accesses begin with the registration of a BankActivate command which is then

followed by a Read or Write command.

The EM638325 provides for programmable Read or Write burst lengths of 1, 2, 4, 8, or full page, with a burst

termination option. An auto precharge function may be enabled to provide a self-timed row precharge that is initiated at

the end of the burst sequence. The refresh functions, either Auto or Self Refresh are easy to use.

By having a programmable mode register, the system can choose the most suitable modes to maximize its

performance. These devices are well suited for applications requiring high memory bandwidth.

Features

· Clock rate: 200/183/166/143/125/100 MHz

· Fully synchronous operation

· Internal pipelined architecture

· Four internal banks (512K x 32bit x 4bank)

· Programmable Mode

- CAS# Latency: 2 or 3

- Burst Length: 1, 2, 4, 8, or full page

- Burst Type: interleaved or linear burst

- Burst-Read-Single-Write

· Burst stop function

· Individual byte controlled by DQM0-3

· Auto Refresh and Self Refresh

· 4096 refresh cycles/64ms

· Single +3.3V ± 0.3V power supply

· Interface: LVTTL

· Package: 400 x 875 mil, 86 Pin TSOP II, 0.50mm

pin pitch

· Lead Free Package available

完整的pdf格式文檔51黑下載地址:

datasheet.pdf

(781.1 KB, 下載次數: 4)

datasheet.pdf

(781.1 KB, 下載次數: 4)

2018-10-12 16:49 上傳

點擊文件名下載附件

|