|

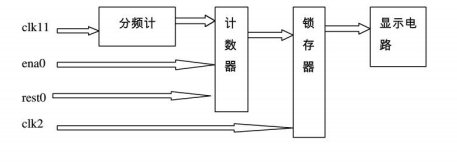

���� FPGA �ǬF(xi��n)���ɾ����T��У�Field Programmable Gate Array���ĺ��Q��FPGA���������_�l(f��)ϵ�y(t��ng)���_�l(f��)��Ҏ(gu��)ģ��(sh��)�ּ����·���¼��g��������Ӌ��C�o���OӋ���L�Ƴ����F(xi��n)�Ñ�߉��ԭ��D�����������̻���Ӳ�������Z�Եȷ�ʽ�����OӋݔ�룻Ȼ��һϵ���D�Q�����ԄӲ��ֲ�����ģ�M������^�̣������������FPGA�����Ĕ�(sh��)���ļ�����FPGA������ʼ�����@�Ӿ͌��F(xi��n)�˝M���Ñ�Ҫ��Č��ü����·�������_�����Ñ������OӋ���������ƺ��������a�����·��Ŀ�ġ� FPGA��һ�N�붨�Ƶļ����·�������c��ֱ�������Ñ������ИO����`���Ժ�ͨ���ԣ��_�l(f��)Ч�ʸߣ�Ӳ���yԇ�͌��F(xi��n)��ݣ������ɿ��Ժö��Ҽ��g�S�o���Ρ� �S����Ӽ��g�İl(f��)չ�������·��Ҏ(gu��)ģԽ��Խ���s�̶�ҲԽ��Խ�ߡ�������˴�Ҏ(gu��)ģ�ĺ͏��s�̶ȵ��·�OӋ���}�����y(t��ng)���T�����������@���^�ڬ�����y�Թ�������VHDL�Z�Ծ��Џ���Ĺ��ܣ����w��V�������������������ڏ��T�����·��ֱ��ϵ�y(t��ng)��������������;C�ϡ����溆Ҫ��B��VHDL�Z�ԡ� VHDL��Ӣ��ȫ����Very-High-Speed Intergrated Circuit Hardware Description Language�Q����1982�ꡣ1987��ף�VHDL��IEEE�������������_�J��˜�Ӳ�������Z�ԡ���IEEE������VHDL�Ę˜ʰ汾��IEEE-1076�����Q87�棩֮��EDA��˾���^�Ƴ����Լ���VHDL�OӋ�h(hu��n)�����������Լ����OӋ���߿��Ժ�VHDL�ӿڡ��˺�VHDL������OӋ�I��õ��ˏV���Ľ��ܣ�����ȡ����ԭ�еķǘ˜ʵ�Ӳ�������Z�ԡ�1993�꣬IEEE��VHDL�M������ӆ���ĸ��ߵij���Ӵκ�ϵ�y(t��ng)���������ϔUչVHDL�ă��ݣ��������°汾��VHDL����IEEE�˜ʵ�1076-1993�汾�����Q93�棩���F(xi��n)�ڣ�VHDL��Verilog����IEEE�Ĺ��I(y��)�˜�Ӳ�������Z�ԣ��ֵõ�����EDA��˾��֧�֡�����ӹ����I���ѳɞ����ϵ�ͨ��Ӳ�������Z�ԡ��Ќ����J�飺���µ����o�У�VHDL�cVerilog�Z�Ԍ��Г���ֵĔ�(sh��)��ϵ�y(t��ng)�OӋ�΄ա�VHDL��Ҫ����������(sh��)��ϵ�y(t��ng)�ĽY�����О顢���ܺͽӿڡ����˺����S�����Ӳ���������Z���⣬VHDL���Z����ʽ�������L���c�䷨��ʮ�������һ���Ӌ��C���Z�ԡ�VHDL�ij���Y�����c�nj�һ헹����OӋ������Q�OӋ���w��������һ��Ԫ����һ���·ģ�K��һ��ϵ�y(t��ng)���ֳ��ⲿ����Q��ҕ���֣����˿ڣ��̓Ȳ�����Q����ҕ���֣������OӋ���w�ăȲ����ܺ��㷨��ɲ��֡��ڌ�һ���OӋ���w���x���ⲿ�����һ����Ȳ��_�l(f��)��ɺ��������OӋ�Ϳ���ֱ���{���@�����w���@�N���OӋ���w�ֳɃ��ⲿ�ֵĸ�����VHDLϵ�y(t��ng)�OӋ�Ļ����c�� Quartus II��Altera��˾�Ƴ���CPLD/FPGA���ɻ��_�l(f��)ܛ������������OӋݔ�롢߉�C�ϡ������c���������桢�r�������Ӳ������������PLD�OӋ���̡�Quartus���ṩ�˶�N�OӋݔ�뷽ʽ�����ٵľ��g��ֱ�������������̡������Ѻõ��Ñ����棬 ���ٵľC���ٶȺ���(y��u)���ľC�Ϻ��m�书�ܡ�Quartus II�Ԏ��깦��ģ�K�죬���p�p���Ñ��Ĺ��������ӿ��OӋ�ٶȡ�Quartus II ���÷����������ڹ����з����κ��OӋ�����M�й��ܷ��桢�r������z��OӋ��߉���ܺ�Ӌ���OӋ�ăȲ����r�Ƿ�����OӋ�����������Է��������OӋ��������OӋ���κβ��֡�֧�ֿɾ���ϵ�y(t��ng)��SOPC���ʹ�Ҏ(gu��)ģFPGA�OӋ�_�l(f��)����ϵ�y(t��ng)���OӋ��Ƕ��ʽܛ���_�l(f��)���ɾ���߉�OӋ��һ�w����һ�N�C���Ե��_�l(f��)ƽ�_�� ԓܛ��֧��Altera��˾��Stratix ��Stratix GX��Stratix��MAX3000A��MAX 7000B��MAX 7000AE��MAX ��FLEX6000��FLEX10Kϵ�С�Cyclone��Cyclone��APEX ��APEX20K��ACEX1Kϵ�С� 1 ���w�OӋ���� �OӋ����FPGA��Ӌ��(sh��)����Ҫ���@ʾ1��0-9999����λӋ��(sh��)����������4��ģ�K��10��ʮ�M��Ӌ��(sh��)����(li��n)���ɣ����Կ����@ʾ���l�ʷ�����1-9999HZ������l��Ӌ�Ĺ��ָܷ���Ă�ģ�K�����lӋ��Ӌ��(sh��)����ݔ���i�������g�a�@ʾ�·������ģ�K����VHDL�Z����������Quartus���M�з��档���OӋ���Ô�(sh��)�ط��lӋ���Ԍ���̖���F(xi��n)��ͬ���l��ݔ����̖����Ӌ��(sh��)��ݔ�롣�i������һ���ⲿ�}�_���ƿ��Կ����@ʾ�����@ʾ���ڡ���ϵ�y(t��ng)���������r��ݔ����̖���ṩ�l�ʣ����^���l�����l���a��Ӌ��(sh��)��̖����Ӌ��(sh��)��ģ�K��Ӌ��(sh��)ģ�K��ݔ����}�_����(sh��)�M��Ӌ��(sh��)��(sh��)�Y����Ӌ��(sh��)�Y�������i�����У����Cϵ�y(t��ng)���Է�(w��n)���@ʾ��(sh��)����Ӌ��(sh��)�Y���܉��@ʾ���߶Δ�(sh��)�a�@ʾ���ϡ�

�D1-1���w�OӋ���� 2������ģ�K�OӋ������ 2.1���l�����OӋ 2.1.1���l���OӋԭ�� Ƕ��ʽ�O��Ʒ�N����������ܲҲʮ�־���ЩǶ��ʽ�O����VoIP�Ԓ�����ε�܇�dϵ�y(t��ng)�����εęC픺еȣ������������΄Ն�һ�����ܺ��Σ����Ӌ�������ʹ惦���g�������ޡ������@Щ�O���M����ֲ�@Ȼ�Dz��F(xi��n)���ġ���ˣ���Ƕ��ʽ�O����x���ϣ����Ŀ����ֲ��Ŀ���O�䶨λ�ھ���һ��Ӌ�������ʹ惦���g���и߶�Ƕ��ʽ�O���ϡ����^�д����Ե�Ƕ��ʽ�O��������и߶�PDA���и߶������Ԓ���и߶˙C픺еȡ����⣬���˼ӿ���ֲ���ٶȣ��p���_�l(f��)���ڣ���ˣ���Ƕ��ʽ�O���Ӳ��ƽ�_�x���X86�wϵ�Y����Ӳ��ƽ�_���ڔ�(sh��)��߉�·�OӋ�У����l����һ�N�����·��ͨ�^���l���Եõ���Ҫ�ĕr��l�ʡ���Ҋ�ķ��l���ж��M�Ʒ��l����ż��(sh��)�η��l�����攵(sh��)�η��l����ռ�ձȿ��{�ķ��l����С��(sh��)���l�������l�ķ����ܶ��Ҋ�ľ������üӷ������r���̖�M�з��l����ȻҲ��������һЩ���õ��·�Y���팍�F(xi��n)�� ��(sh��)�ط��l���Ĺ�������ݔ��˽o����ͬ��(sh��)���r������ݔ��ĕr���̖�в�ͬ�ķ��l�ȣ�����һ��N���l�������l���ĕr�������ԭ�r����ڵ�N�����l��׃?y��u)�ԭ���?/N������һ��8λӋ��(sh��)�������ݔ�딵(sh��)D��Ȼ��Ӌ��(sh��)���������t���^D���ĕr�����Ӌ��(sh��)������r��ݔ��full׃?y��u)���ƽ������full��������̖����fout�M��ȡ�����������N=2D��Ӌ��(sh��)һ�κ�������Ӌ��(sh��)�������M��ֱ��ݔ�뱻�x����ֵ�����ڔ�(sh��)�ط��l��(sh��)�����b�d��ͬ��Ӌ��(sh��)��ʼֵ�r�����в�ͬ�l�ʵ������̖���Ķ��õ���ͬ��ݔ������(sh��)�ط��l��������Ӌ��(sh��)ֵ�ɲ����A�õļӷ�Ӌ��(sh��)���OӋ��ɵġ� 2.1.2Դ�����η��� module clk_gen (clk_33m, //system input clock; rst, //system reset; clk_1, //output 1hz clock clk_8, //output 8hz clock clk_16, //output 16hz clock clk_32, //output 32hz clock clk_32k); //output 32khz clock

input clk_33m,rst; output clk_1,clk_8,clk_16,clk_32,clk_32k;

wire clk_33m,rst; reg [24:0] count; wire clk_32k,clk_1,clk_8,clk_16,clk_32;

//************* clock generator****************************

always @(posedge clk_33m or negedge rst) if (!rst) count<=25'd0; else count<=count+1'b1;

assign clk_1=count[24]; assign clk_32k=count[9]; assign clk_8=count[21]; assign clk_16=count[20]; assign clk_32=count[19];

endmodule

�D2-1 ���l���r�����

2.1.3���l��RTL �·�D

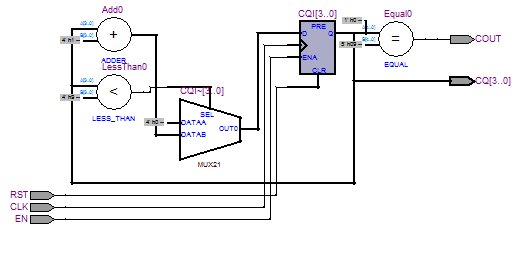

�D2-2 ���l��RTL�·�D 2.2Ӌ��(sh��)�����OӋ 2.2.1���l���OӋԭ�� Ӌ��(sh��)��һ�N��λ������\�㣬Ӌ��(sh��)�����nj��F(xi��n)�@�N�\���߉�·��Ӌ��(sh��)���ڔ�(sh��)��ϵ�y(t��ng)����Ҫ�nj��}�_�Ă���(sh��)�M��Ӌ��(sh��)���Ԍ��F(xi��n)�y����Ӌ��(sh��)�Ϳ��ƵĹ��ܣ�ͬ�r���з��l���ܣ�Ӌ��(sh��)�����ɻ�����Ӌ��(sh��)��Ԫ��һЩ�����T���M�ɣ�Ӌ��(sh��)��Ԫ�t��һϵ�о��д惦��Ϣ���ܵĸ���|�l(f��)�����ɣ��@Щ�|�l(f��)����RS�|�l(f��)����T�|�l(f��)����D�|�l(f��)����JK�|�l(f��)���ȡ�Ӌ��(sh��)���ڔ�(sh��)��ϵ�y(t��ng)�Б��ÏV�����������Ӌ��C�Ŀ������Ќ�ָ���ַ�M��Ӌ��(sh��)���Ա����ȡ����һ�lָ����\���������˷��������\��rӛ�¼ӷ����p���Δ�(sh��)�������ڔ�(sh��)�փx���Ќ��}�_��Ӌ��(sh��)�ȵȡ�Ӌ��(sh��)�������Á��@ʾ�aƷ�Ĺ�����B(t��i)��һ����f��Ҫ���Á���ʾ�aƷ�ѽ�����˶��ٷݵ������퓹���������Ҫ��ָ������Ӌ��(sh��)����λ��(sh��)����Ҋ����3λ��4λ�ġ����@Ȼ��3λ��(sh��)��Ӌ��(sh��)���������@ʾ��999��4λ��(sh��)���������@ʾ��9999���ڔ�(sh��)����Ӽ��g�Б��õ����ĕr��߉�·��Ӌ��(sh��)�����H�����ڌ��r��}�_Ӌ��(sh��)��߀�������ڷ��l�����r���a����(ji��)���}�_���}�_�����Լ��M�Д�(sh��)���\��ȡ����Dz��o���@ʾӋ��Y����һ�㶼��Ҫͨ�^���LCD��LED�������@ʾ�� 2.2.2��ʮ�M��Ӌ��(sh��)�� odule COUNT_60 (clk, //count input clock; rst, //system reset; rco, //carry output q); //BCD code output

input clk,rst; output reg rco; output [6:0] q;

wire clk,rst; reg [6:0] q; reg en;

//*********************************************************

always @(posedge clk or negedge rst)

if (!rst) q[3:0]<=4'd0; else if(q[3:0]==4'd8) begin q[3:0]<=q[3:0]+1'b1; en<=1'b1; end else if (q[3:0]==4'd9) begin q[3:0]<=4'd0; en<=1'b0; end else begin q[3:0]<=q[3:0]+1'b1; en<=1'b0; end

always @(posedge clk or negedge rst)

if (!rst) q[6:4]<=3'd0; else if (en) begin if (q[6:4]==3'd5) begin q[6:4]<=3'd0; rco<=1'b1; end else begin q[6:4]<=q[6:4]+1'b1; rco<=1'b0; end end else ;

Endmodule 2.2.3RTL�·�D

�D2-3��ʮ�M��Ӌ��(sh��)��RTL�·�D 2.3�i�������OӋ2.3.1�i�����OӋԭ�����^�i����������ݔ���˵Ġ�B(t��i)�����Sݔ��˵Ġ�B(t��i)׃����׃�����H�����i����̖�rݔ��Ġ�B(t��i)�����浽ݔ����ֱ����һ���i����̖����r�Ÿ�׃�����͵��i����߉�·��D �|�l(f��)���·����LED�͔�(sh��)�a���@ʾ���棬Ҫ�S��һ����(sh��)�����@ʾ������Ҫ���m(x��)�Ŀ��ٵ�ˢ�¡����������Ķΰ�λ��(sh��)�a�ܵ��@ЩҪ�xͨ���@ʾ�O���ϡ�������܉���ܵ�ˢ���l��֮�ȣ����ÿ��ʮ�����Ҫˢ��һ�Ρ��@�ʹ��ռ����̎������̎��r�g��������̎������̎��������߀���M��̎�����Ĺ��ġ��i������ʹ�ÿ��Դ��ľ���̎�������@����ĉ�������̎�����є�(sh��)����ݔ?sh��)��i�����������i����i������ݔ�����_���һֱ���֔�(sh��)����B(t��i)ֱ����һ���i���µĔ�(sh��)����ֹ���@���ڔ�(sh��)�a�ܵ��@ʾ���ݲ�׃֮ǰ��̎������̎��r�g��IO���_�����ጷš����Կ�����̎����̎���ĕr�g�H�����@ʾ���ݰl(f��)��׃���ĕr���@�������@ʾ�r�g��ֻ�Ƿdz��ٵ�һ�����֡���̎������̎���������и���ĕr�g���(zh��)���������΄ա��@�����i������LED�͔�(sh��)�a���@ʾ���������:��(ji��)ʡ�ˌ��F��MCU�r�g��

2.3.2�i����Դ�����η��� module sem_drive (oSEG0, oSEG1, oSEG2, oSEG3, oSEG4, oSEG5, oSEG6, oSEG7, //output to 8 SEG iDIG ); //input 8-BCD code (4*8=32bit) input [31:0] iDIG; output [6:0] oSEG0,oSEG1,oSEG2,oSEG3,oSEG4,oSEG5,oSEG6,oSEG7;

wire [31:0] iDIG; wire [6:0] oSEG0,oSEG1,oSEG2,oSEG3,oSEG4,oSEG5,oSEG6,oSEG7;

SEG7_LUT U0 (.oSEG(oSEG0),.iDIG(iDIG[3:0])); SEG7_LUT U1 (.oSEG(oSEG1),.iDIG(iDIG[7:4])); SEG7_LUT U2 (.oSEG(oSEG2),.iDIG(iDIG[11:8])); SEG7_LUT U3 (.oSEG(oSEG3),.iDIG(iDIG[15:12])); SEG7_LUT U4 (.oSEG(oSEG4),.iDIG(iDIG[19:16])); SEG7_LUT U5 (.oSEG(oSEG5),.iDIG(iDIG[23:20])); SEG7_LUT U6 (.oSEG(oSEG6),.iDIG(iDIG[27:24])); SEG7_LUT U7 (.oSEG(oSEG7),.iDIG(iDIG[31:28]));

Endmodule �D2-4 �i�����r�����D 2.2.3�i����RTL �·�D �D2-5 �i����RTL�·�D 2.4�@ʾ���ֵ��OӋ 2.4.1�߶Δ�(sh��)�a���@ʾԭ�� �����˙C����ʽ��Ƭ�Cϵ�y(t��ng)���f�����H��Ҫ푑��Ñ�ݔ�룬ͬ�rҲ��Ҫ��һЩ�y����Ϣݔ���@ʾ���@Щ�@ʾ��Ϣ�����ṩ���r�Ĕ�(sh��)����D�νY�����Ա�������ϵ�y(t��ng)�Ġ�B(t��i)���M�з���̎����Ŀǰ����õ���LED��(sh��)�a���@ʾ����ɱ�������ʹ�ú��㣬�����@ʾ��(sh��)�ֻ�ׂ��ض����ַ�����(sh��)�a�ܔ�(sh��)�a�ܵ�һ�N�ǰ댧�w�l(f��)����������(sh��)�a�ܿɷ֞��߶Δ�(sh��)�a�ܺͰ˶Δ�(sh��)�a�ܣ��^(q��)�e���ڰ˶Δ�(sh��)�a�ܱ��߶Δ�(sh��)�a�ܶ�һ���l(f��)����O�܆�Ԫ���������Ԫ�ǰl(f��)����O�ܡ���(sh��)�a��ͨ�^���䲻ͬ�Ĺ��_ݔ�������������ʹ��l(f��)�����Ķ��@ʾ����(sh��)���܉��@ʾ�r�g�����ڡ��ضȵ����п��Ô�(sh��)�ֱ�ʾ�ą���(sh��)��������������e�Ǽ���I���ØO��V�������@ʾ�������{����ˮ��������ȵȡ��^�����(sh��)��ˮ���õĶ��ǔ�(sh��)�a�ܣ��������Ҳ��Һ�����c�ɹ����� 2.4.2�߶Δ�(sh��)�a���@ʾԴ�����η���module SEG7_LUT (oSEG, //output SEG7 code iDIG); //input BCD code input [3:0] iDIG; output [6:0] oSEG; reg [6:0] oSEG;

// --a-- // | | // f b // | | // --g-- // | | // e c // | | // --d-- O DP

always @(iDIG) case(iDIG) //gfedcba 4'h0: oSEG = 7'b1000000; //display 0; 4'h1: oSEG = 7'b1111001; //display 1; 4'h2: oSEG = 7'b0100100; //display 2; 4'h3: oSEG = 7'b0110000; //display 3; 4'h4: oSEG = 7'b0011001; //display 4; 4'h5: oSEG = 7'b0010010; //display 5; 4'h6: oSEG = 7'b0000010; //display 6; 4'h7: oSEG = 7'b1111000; //display 7; 4'h8: oSEG = 7'b0000000; //display 8; 4'h9: oSEG = 7'b0010000; //display 9; // 4'ha: oSEG = 7'b0001000; //display A; 4'ha: oSEG = 7'b0111111; //display - for clock; 4'hb: oSEG = 7'b0000011; //display B; 4'hc: oSEG = 7'b1000110; //display C; 4'hd: oSEG = 7'b0100001; //display D; 4'he: oSEG = 7'b0000110; //display E; 4'hf: oSEG = 7'b0001110; //display F; endcase

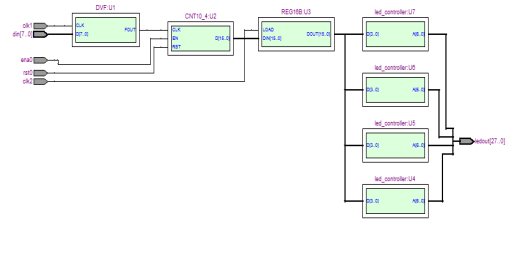

Endmodule 3ϵ�y(t��ng)플��OӋ 3.1������µ��OӋ���� ���^��������OӋ����,���Dz��ÿ���ȫ������оƬ�S�̼���aƷ�Y���������Z,�ڹ��ܼ����OӋ�aƷ�M�ж��x,���Y�Ϲ��ܷ��漼�g,�Դ_���OӋ�����_��,�ܶ��x��ɺ�,����߉�C�ϼ��g,�ѹ��������D�Q��ijһ���w�Y��оƬ�ľW���ļ�,ݔ���o�S�̵IJ��ֲ������M�в��ֲ��������ֲ����Y��߀�ɷ��˻�ͬһ������,�M�а������͕ܺr��ĺ���C,�Ա��C���ֲ������������T�ӕr�;��ӕr����Ӱ��OӋ�����ܡ� ��������OӋ�����ă�(y��u)Խ�����@����Ҋ�ġ�����,���ڹ�����������ȫ������оƬ�Y��,���OӋ������A��,�OӋ���ɲ���оƬ�Y���ļs��,���о����M�ЮaƷ�OӋ,�����˂��y(t��ng)�OӋ�������������������OӋ�L�U,���s�����OӋ���ڡ����,�OӋ�������õõ����C��Ŀǰ����ӮaƷ����ģ�K���l(f��)չ�����^ģ�K�����nj������OӋ�ɹ��M����,�M�Ϻ�������,�a��ȫ�µĻ������OӋ,����������OӋ�����Ĺ����������cоƬ�Y���o�P����˿�����һ�NIP�ķ�ʽ�M�д�n,�Ա㌢�����������á� ����,�OӋҎ(gu��)ģ�����ߡ����ε��Z������������ɏ��s�Ĺ���,������Ҫ�ֹ��L�D�����ģ�оƬ�x������`��OӋ�������^�̵ĕr�g�Ȳ��ø��N�Y��оƬ�����ͬһ��������,�Ķ����OӋҎ(gu��)ģ���ٶȡ�оƬ�r��ϵ�y(t��ng)����Ҫ��ȷ����M��ƽ��,�x����ѽY���� 3.2플��OӋԴ��������沨�� module sem_drive (oSEG0, oSEG1, oSEG2, oSEG3, oSEG4, oSEG5, oSEG6, oSEG7, //output to 8 SEG iDIG ); //input 8-BCD code (4*8=32bit) input [31:0] iDIG; output [6:0] oSEG0,oSEG1,oSEG2,oSEG3,oSEG4,oSEG5,oSEG6,oSEG7;

wire [31:0] iDIG; wire [6:0] oSEG0,oSEG1,oSEG2,oSEG3,oSEG4,oSEG5,oSEG6,oSEG7;

SEG7_LUT U0 (.oSEG(oSEG0),.iDIG(iDIG[3:0])); SEG7_LUT U1 (.oSEG(oSEG1),.iDIG(iDIG[7:4])); SEG7_LUT U2 (.oSEG(oSEG2),.iDIG(iDIG[11:8])); SEG7_LUT U3 (.oSEG(oSEG3),.iDIG(iDIG[15:12])); SEG7_LUT U4 (.oSEG(oSEG4),.iDIG(iDIG[19:16])); SEG7_LUT U5 (.oSEG(oSEG5),.iDIG(iDIG[23:20])); SEG7_LUT U6 (.oSEG(oSEG6),.iDIG(iDIG[27:24])); SEG7_LUT U7 (.oSEG(oSEG7),.iDIG(iDIG[31:28]));

endmodule 3.2.1ϵ�y(t��ng)플�RTL �·�D

�D3-1ϵ�y(t��ng)플�RTL �·�D 4���Y ���@���OӋ�������˺ܶ����H�ԵĆ��}���ڌ��H�OӋ�вŰl(f��)�F(xi��n)����������Փ�ԵĖ|���c�ڌ��H�\���е�߀����һ���ij���ģ�������Щ���}����Ҫ��������⣬����Ҫ����ظ�����ǰ���e�`˼�S��һ�І��}���Ҫ���Լ�һ�cһ�εĽ�Q�����ڽ�Q���^�̮�������l(f��)�F(xi��n)�Լ����w�ٵ����������ڽ̲Ĺ���ϵ�y(t��ng)��������DZ��^���εģ���Ҫ�ǽ�Q�����OӋ�еĆ��}���������OӋ��һ�����`��Ė|��������ӳ�����Q���}��߉˼�S�̈́�(chu��ng)��������������һ���OӋ���`�����ڡ�����������OӋ�^���д֕r�g�����ڳ�������ġ��ܶ��ӳ����ǿ��Խ��b�����ϵģ�������㕽Ӹ����ӳ�������P�I�Ć��}���ڣ��@��Ҫ��ϵ�y(t��ng)�ĽY������Ϥ��ͨ�^�@���OӋ��Ҳ�l(f��)�F(xi��n)���������ڵIJ���֮̎���mȻ���X��Փ���ѽ����գ������\�õ����`���^�����������벻���������^һ��Ŭ���ŵ��Խ�Q��

������Word��ʽ�ęn51�����d��ַ��

Ф��ȫ20125024033.doc

(422 KB, ���d��(sh��): 17)

Ф��ȫ20125024033.doc

(422 KB, ���d��(sh��): 17)

2018-11-21 17:03 �ς�

�c���ļ������d����

���d�e��: �ڎ� -5

|

����TQQ:125739409;���g����QQȺ281945664

����TQQ:125739409;���g����QQȺ281945664