出租車計費器 一 實驗任務及要求

1. 能實現計費功能,計費標準為:按行駛里程收費,起步費為10.00元,

并在車行3公里后再按2元/公里,當計費器計費達到或超過一定收費(如20元)時,

每公里加收50%的車費,車停止不計費。

2. 實現預置功能:能預置起步費、每公里收費、車行加費里程。

3. 實現模擬功能:能模擬汽車啟動、停止、暫停、車速等狀態。

4. 設計動態掃描電路:將車費顯示出來,有兩位小數。

5. 用Verilog語言設計符合上述功能要求的出租車計費器,并用層次化設計方法設計該電路。

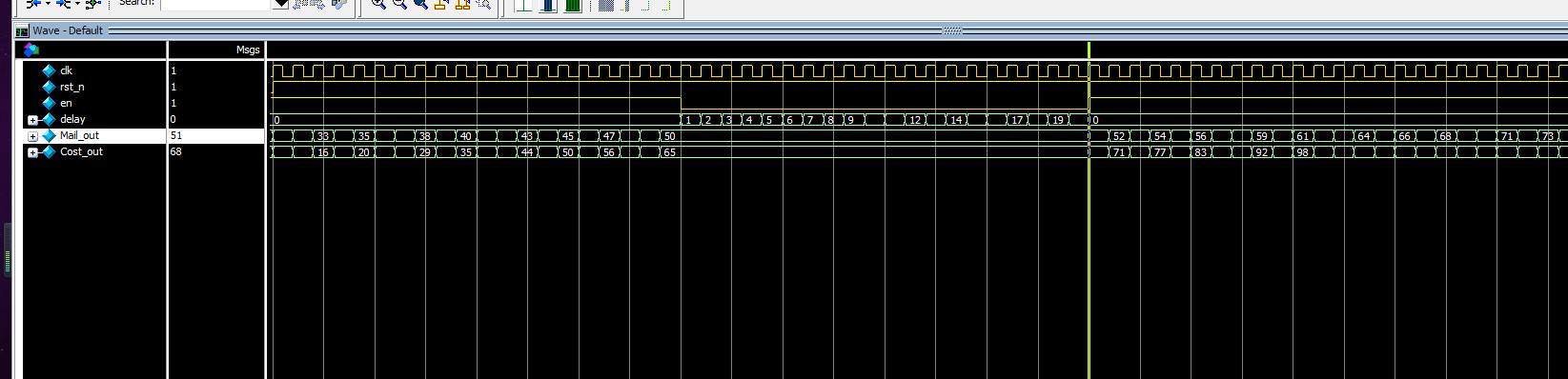

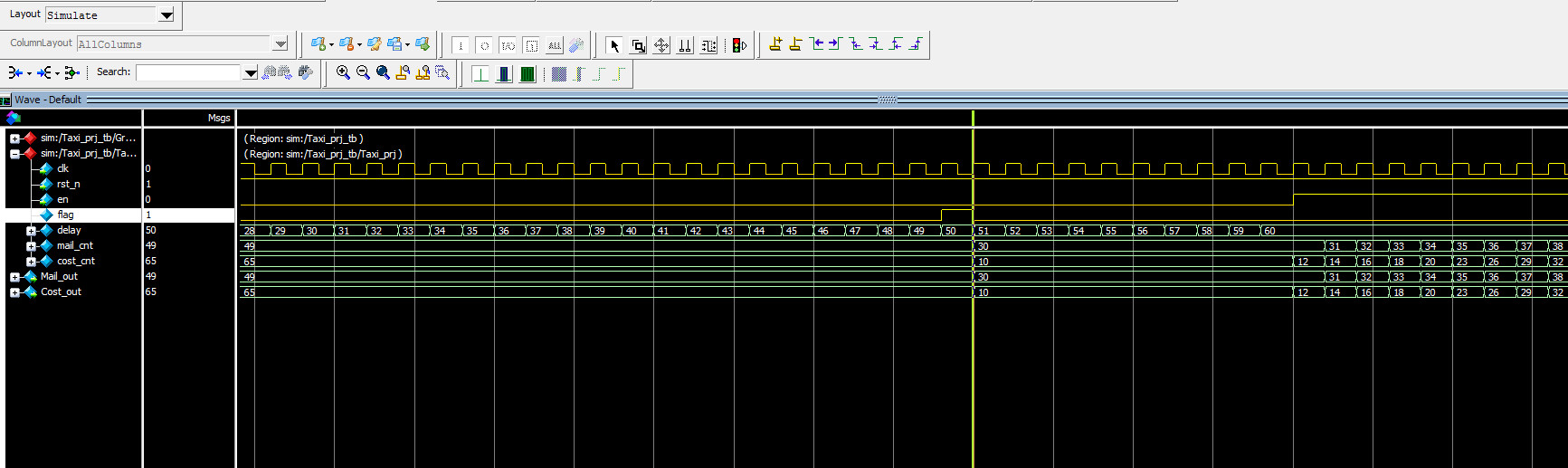

6. 各計數器的計數狀態用功能仿真的方法驗證,并通過有關波形確認電路設計是否正確。

7. 完成電路全部設計后,通過系統實驗箱下載驗證設計的正確性。 計費器按里程收費,每100米開始一次計費。

code: 代碼文檔

doc:設計文檔

img:圖片

prj:工程文檔

tb:仿真文檔

pro_log:工程文檔備份

源碼:

- module Taxi_prj(

- clk,

- rst_n,

- en,

- //delay,

- Mail_out,

- Cost_out

- );

- input clk,rst_n;

- input en;

-

- reg flag;

- reg[9:0] delay;

- output [9:0]Mail_out;

- output [9:0]Cost_out;

-

- reg [9:0] mail_cnt;

- reg [9:0] cost_cnt;

-

- always @(posedge clk or negedge rst_n)

- begin

- if(!rst_n)

- mail_cnt <= 9'd30;

- else if(cost_cnt !=9'd10 && en ==1 && flag ==0)

- mail_cnt <= mail_cnt + 1'b1;//100m

- else if(flag == 1)

- mail_cnt <= 9'd30;

- end

-

- always @(posedge clk or negedge rst_n)

- begin

- if(!rst_n)

- cost_cnt <= 9'd10;

- else if(flag==0 && en)begin

- if(cost_cnt <= 9'd19)//8km

- cost_cnt <= cost_cnt + 9'd2;//2yuan

- else if(cost_cnt >= 9'd20)

- begin

- cost_cnt <= cost_cnt + 9'd3;//2yuan

- end

- end

- else if(flag == 1)

- cost_cnt <= 9'd10;

- //mail_cnt <= 9'd30;

- end

-

- always @(posedge clk or negedge rst_n)

- begin

- if(!rst_n) begin

- delay <= 9'd0;

- flag <= 0;

- end

- else if(en == 0) begin //停車開始計數

- delay <= delay + 9'd1;

- if(delay == 9'd49)begin

- flag <= 1;

- end

- else

- flag <= 0;

- end

-

- end

-

- // always @(posedge clk or negedge rst_n)

- // if(!rst_n)begin

- // if(delay == 9'd49)

- ……………………

- …………限于本文篇幅 余下代碼請從51黑下載附件…………

全部資料51hei下載地址:

taxi.rar

(3.22 MB, 下載次數: 91)

taxi.rar

(3.22 MB, 下載次數: 91)

2018-12-11 11:31 上傳

點擊文件名下載附件

|