自己上課時候寫的小作業,主要用FPGA和VHDL實現了一小鬧鐘,由于我的Altera的開發板資源有限

數碼管用了4個,點陣用了一個。

主要功能:1.能正常跑表,設置跑表時間

2.鬧鈴聲音可以由高到底,三種頻率(你可以在我的基礎上加)

3.懶人起床模式

4.多人使用模式

還有些小功能在我的論文里,有興趣的可以看看(請用Quartus 12.0以上版本打開,不然備注沒法看)

不足之處:if用的太多導致邏輯單元爆炸了,你們 需要優化的的話,多用case代替if

基于FPGA的智能鬧鐘的設計與實現

序言: 本FPGA的智能鬧鐘的是基于Altera Cyclone IV EP系列芯片開發設計的。由于實驗平臺的限制,外設設備選擇了一個4管數碼管,蜂鳴器,獨立按鍵4個,撥碼開關4個和8X8的Led點陣一個。

1.帶有設置功能的時鐘表(設置時間用Led點陣顯示字母S來表示)。 2.帶有設置功能的鬧鈴(設置時間用Led點陣顯示數字1或2來表示)。 3.多人使用模式(這里設置了用戶1,用戶2,使用狀態用Led點陣來顯示)。 4.自然醒的鈴音(在鬧鈴響的時候,使用蜂鳴器的聲音逐漸變大的模式,符合人體規律,任意獨立按鍵可以關閉鬧鈴)。 5.懶人起床模式(通過撥碼開關設置,開啟時,會在60秒內,響3次,每次10秒。兩次之間間隔10秒,可以通過任意的獨立按鍵關閉本次響鈴,但是,下次仍會響,直到3次結束)。  設計方案 設計方案

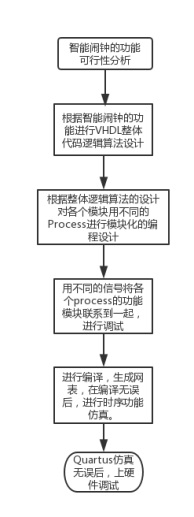

整體設計的流程圖如下

本系統使用的50MHz的晶振,故此,用一個Process進行分頻,1Hz用于正常的時間記時間。此外生成一個1000Hz用于時鐘時間在數碼管上顯示時選管。(運用動態掃描的方式來驅動數碼管)。而使用者,只需要通過把撥碼開關1撥到ON且撥碼開關2在OFF的時候,才能對時鐘的時間進行設置。 鬧鈴模式的基本實現邏輯是:使用一個IF語句,當設置的秒,分的所有值與正常時鐘跑表時間一致的時候讓邏輯標志值為真,驅動鬧鈴的process。使用者,只需要把撥碼開關2撥到OFF,其余的隨意設置,才能對鬧鈴的時間進行設置。鬧鈴時,按任意的獨立按鍵可以關閉鬧鈴。 通過撥碼開關3,在ON時表示用戶1在使用鬧鐘,在OFF時表示用戶2在使用鬧鐘。 通過使用分頻器分出3種不同的頻率,設置3種頻率驅動蜂鳴器的總時間為10秒,每種頻率分別占用3.333秒左右。 通過撥碼開關4,撥碼開關撥到ON的時候,開啟懶人模式,徹底的關閉懶人模式只有將撥碼開關撥到OFF或等3次鬧鈴結束的時候。如果在鬧鈴的期間,隨意的按一下獨立按鍵開關會終止本次鬧鈴,但是下次鬧鈴仍會繼續。

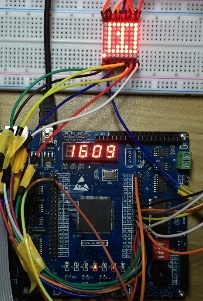

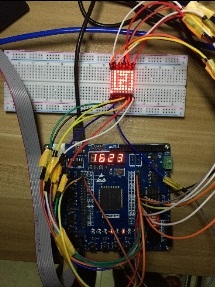

用戶1在正常使用時的硬件效果圖 用戶1在正常使用時的硬件效果圖

圖1 表示用戶1設置鬧鈴中 圖2 表示用戶1正常使用中

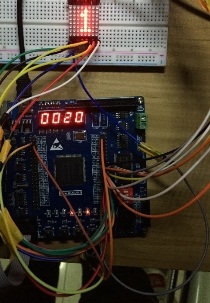

圖3 表示用戶2正常使用中 圖4 表示用戶2設置鬧鈴中 圖3 表示用戶2正常使用中 圖4 表示用戶2設置鬧鈴中

圖5 表示用戶1或者2再設置時鐘時間中

圖6 表現用戶2鬧鈴中

通過這次FPGA的課程設計,我對FPGA的整體認識上了一個新的臺階,以前的實驗課只是從事單個的邏輯功能芯片的實現,而此次基于FPGA的智能鬧鐘的設計與實現寫了足足600行的代碼,大大的提高了我的編程和邏輯分析能力。也初步具備分析和設計一個較為復雜的項目的能力。此外,在這次課程設計中我也認識到我的不足之處,首先,在編程風格上的缺陷,自己對FPGA的寄存器和邏輯單元這兩個最重要的資源理解不到位,導致自己在編程的過程中沒有節約這兩項資源。例如,過多的使用IF-ELSE語句而不用CASE語句導致產生大量的優先級的編碼器從而使得只寫了600行代碼后發現邏輯單元不夠用了。其次,本次設計中,時序和邏輯比較復雜,后期的自學中才發現,應對復雜的邏輯設計,VHDL中的有限狀態機(Finite State Machine)能很好的應對,遠比不斷地使用邏輯標志方便和高效。可以說,這次課程設計收益頗多,需要進一步的學習和總結。才能早日在FPGA的設計與開發中取得一定的成績。

全部資料51hei下載地址:

|