文中應用了MATLAB和VHDL聯合設計,提出基于電路分割技術實現通信系統發送端根升余弦波形成型濾波器查表法的FPGA結構,節省了ROM單元,討論其ROM初始化時波形數據的組織方法,完成了該結構VHDL實現,最后給出使用查找表在FPGA上實現基帶脈沖成型濾波器的設計方法和ModelSim環境下的仿真結果

方案1:卷積法的原理,是用一系列乘法和加法對信號進行流水線運算,需要消耗大量的乘法器和加法器,設計較復雜,并有一定的延時。這是一種分布式算法的設計結構,將傳統的乘法運算和累加運算加以改進,轉變為移位、累加運算,降低了硬件消耗,當運算數據的字寬較小時,極大的降低了硬件電路的復雜度,提高了響應速度;但當運算數據的字長較長時,則需要更多的移位迭代運算而不適合高速處理的需求。

方案2:查表法的原理,采用二進制基帶信號的連續查表法實現在FPGA上完成信號的脈沖成型,原理是預先將所有可能的成形后的基帶波形樣本存入ROM,根據輸入序列,從ROM中查找對應輸出波形,這種方法簡單直觀、速度快,且當碼間樣點增加時,僅增長地址電路即可,不影響運行時間,可在一定的精度內高效的實現脈沖成型濾波。

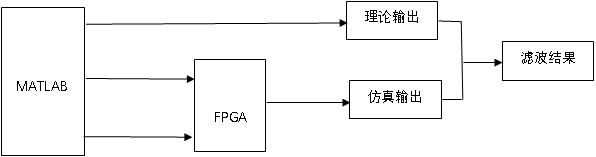

總體框圖

框圖

本次設計首先利用MATLAB中的FDAtool工具設計出一個采樣頻率為10MHZ、截止頻率為50KHZ、滾降系數為0.35的升余弦滾降濾波器,通過FDAtool導出16點系數,然后將系數進行放大、取整,以便于在FPGA中使用,最后通過QuartusII進行Verilog語言編寫濾波器算法,然后通過Modesim仿真結果和MATLAB仿真結果的比較來驗證該濾波器的正確性

(1) 首先,在MATLAB command window 命令窗內輸入 FDAtool命令,按Enter,出現FDAtool界面,FDAtool界面如圖所示。

(2)設置本課題要求的平方根升余弦濾波器的參數,設置的參數見界面如圖所示。本次課題采用海明窗,Fc設置為20KHZ,滾降系數設置為0.35,采樣頻率設置為10MHZ,階數設置為17,即n=16。然后點擊點擊“designfilter”按鈕。 (3)查看平方根升余弦濾波器的幅度響應圖 (4)接著用MATLAB中simulink,構建濾波器仿真模塊,simulink仿真如圖所示。 二 FPGA 以下是用FIR核實現平方根升余弦滾降濾波器的步驟: (1)打開Quartus II 軟件,新建一個“project”。點擊“tool”打開“IP Catalog”界面。

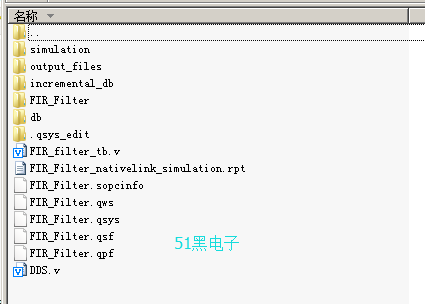

(2)在“Import from file”里導入濾波器系其頻譜圖如所示。 導入的系數是前面MATLAB FDAtool中生成的濾波器系數。 (3)將我們準備好的測試文件FIR_filter_tb.v和DDS .v拷貝至工程目錄文件夾下,文件添加界面如圖所示。

Assignment->setting->EDA tool setting->simulation->testbenches添加仿真文件。 (4)ModelSim仿真 直接啟動仿真軟件Modelsim-Altera,并顯示仿真波形數據(模擬形式顯示) data1 信號為 24KHz 正弦波,量化位寬為 12bit data2 信號為 240KHz 正弦波,量化位寬為 12bit data_in 信號為 data1 和 data2 的疊加信號,量化位寬為13bit

data_out 信號為 data_in信號經過 FIR 數字濾波后的輸出,量化位寬為 28bit。仿真結果如圖所示。 最后可知 matlab和FPGA的濾波結果相同。 - 附 錄

- FIR_filter_tb.v

- // --------------------------------------------------------------------

- // >>>>>>>>>>>>>>>>>>>>>>>>> COPYRIGHT NOTICE <<<<<<<<<<<<<<<<<<<<<<<<<

- // --------------------------------------------------------------------

- // Module: FIR_filter_tb

- //

- // Author: Step

- //

- // Description: FIR_filter_tb

- //

- // --------------------------------------------------------------------

- // Code Revision History :

- // --------------------------------------------------------------------

- `timescale 1ps/1ps

-

- module FIR_filter_tb;

-

- parameter PERIOD = 20;

- reg clk, rst_n;

- wire signed [26:0] data_out;

-

- initial begin

- clk = 0;

- rst_n = 0;

- #100;

- rst_n = 1;

- #6000;

- $stop;

- end

- always #10 clk = ~clk;

-

- wire signed[9:0] data1;

- DDS dds_24k

- (

- .clk_in(clk), //clock in

- .rst_n_in(rst_n), //reset, active low

- .dds_en_in(1), //dds work enable

- .f_increment(24'h60000), //frequency increment

- .p_increment(0), //phase increment

- .dac_data_out(data1) //data out

- );

-

- wire signed[9:0] data2;

- DDS dds_240k

- (

- .clk_in(clk), //clock in

- .rst_n_in(rst_n), //reset, active low

- .dds_en_in(1), //dds work enable

- .f_increment(24'h3c0000), //frequency increment

- .p_increment(0), //phase increment

- .dac_data_out(data2) //data out

- );

-

- wire signed[10:0] data_in = data1 + data2;

- FIR_Filter u0 (

- .ast_sink_data (data_in), // avalon_streaming_sink.data

- .ast_sink_valid (1), // .valid

- .ast_sink_error (0), // .error

- .ast_source_data (data_out), // avalon_streaming_source.data

- .ast_source_valid (), // .valid

- .ast_source_error (), // .error

- .clk (clk), // clk.clk

- .reset_n (rst_n) // rst.reset_n

- );

-

- endmodule

-

- DDS.v

- // --------------------------------------------------------------------

- // >>>>>>>>>>>>>>>>>>>>>>>>> COPYRIGHT NOTICE <<<<<<<<<<<<<<<<<<<<<<<<<

- // --------------------------------------------------------------------

- // Module: DDS

- //

- // Author: Step

- //

- // Description: DDS

- //

- // --------------------------------------------------------------------

- // Code Revision History :

- // --------------------------------------------------------------------

- module DDS

- (

- input clk_in, //clock in

- input rst_n_in, //reset, active low

- input dds_en_in, //dds work enable

- input [23:0] f_increment, //frequency increment

- input [23:0] p_increment, //phase increment

- output dac_clk_out, //clock out

- output [9:0] dac_data_out //data out

- );

- reg [23:0] phase_accumulator;

- wire [23:0] phase;

- //wire [9:0] dac_data_out;

- assign dac_clk_out = clk_in;

- //next_phase = phase_accumulator + f_increment;

- always @(posedge clk_in or negedge rst_n_in)

- begin

- if(!rst_n_in) phase_accumulator <= 23'b0;

- else if(dds_en_in) phase_accumulator <= phase_accumulator + f_increment;

- end

- assign phase = phase_accumulator + p_increment; // phase is the high 8 bits

- lookup_table lookup_table_uut

- (

- .phase(phase[23:16]),

- .dac_data_out(dac_data_out)

- );

- endmodule

- /**************************************************

- module: lookup_table

- **************************************************/

- module lookup_table

- (

- input [7:0] phase,

- output reg [9:0] dac_data_out

- );

- wire [5:0] address = phase[5:0];

- wire [1:0] sel = phase[7:6];

- wire [9:0] sine;

- always@(sel or sine)

- case (sel)

- 2'b00 : dac_data_out = {1'b0, sine[9:1]};

- 2'b01 : dac_data_out = {1'b0, sine[9:1]};

- 2'b10 : dac_data_out = {1'b1, 9'h1ff-sine[9:1]};

- 2'b11 : dac_data_out = {1'b1, 9'h1ff-sine[9:1]};

- endcase

- sine_table sine_table_uut

- (

- .sel(sel),

- .address(address),

- .sine(sine)

- );

-

- endmodule

- /**************************************************

- module: sine_table

- **************************************************/

- module sine_table

- (

- input [1:0] sel,

- input [5:0] address,

- output reg [9:0] sine

- );

- reg [5:0] table_addr;

- always @(sel or address)

- case (sel)

- 2'b00: table_addr = address;

- 2'b01: table_addr = 6'h3f - address;

- 2'b10: table_addr = address;

- 2'b11: table_addr = 6'h3f - address;

- endcase

- always @(table_addr)

- case(table_addr)

- 6'h0: sine=10'h000;

- 6'h1: sine=10'h019;

- 6'h2: sine=10'h032;

- 6'h3: sine=10'h04B;

- 6'h4: sine=10'h064;

- 6'h5: sine=10'h07D;

- 6'h6: sine=10'h096;

- 6'h7: sine=10'h0AF;

- 6'h8: sine=10'h0C4;

- 6'h9: sine=10'h0E0;

- 6'ha: sine=10'h0F9;

- 6'hb: sine=10'h111;

- 6'hc: sine=10'h128;

- 6'hd: sine=10'h141;

- 6'he: sine=10'h159;

- 6'hf: sine=10'h170;

- 6'h10: sine=10'h187;

- 6'h11: sine=10'h19F;

- 6'h12: sine=10'h1B5;

- 6'h13: sine=10'h1CC;

- 6'h14: sine=10'h1E2;

- 6'h15: sine=10'h1F8;

- 6'h16: sine=10'h20E;

- 6'h17: sine=10'h223;

- 6'h18: sine=10'h238;

- 6'h19: sine=10'h24D;

- 6'h1a: sine=10'h261;

- 6'h1b: sine=10'h275;

- 6'h1c: sine=10'h289;

- 6'h1d: sine=10'h29C;

- 6'h1e: sine=10'h2AF;

- 6'h1f: sine=10'h2C1;

- 6'h20: sine=10'h2D3;

- 6'h21: sine=10'h2E5;

- 6'h22: sine=10'h2F6;

- 6'h23: sine=10'h307;

- 6'h24: sine=10'h317;

- 6'h25: sine=10'h326;

- 6'h26: sine=10'h336;

- 6'h27: sine=10'h344;

- 6'h28: sine=10'h353;

- 6'h29: sine=10'h360;

- 6'h2a: sine=10'h36D;

- 6'h2b: sine=10'h37A;

- 6'h2c: sine=10'h386;

- 6'h2d: sine=10'h392;

- 6'h2e: sine=10'h39C;

- 6'h2f: sine=10'h3A7;

- 6'h30: sine=10'h3B1;

- 6'h31: sine=10'h3BA;

- 6'h32: sine=10'h3C3;

- 6'h33: sine=10'h3CB;

- 6'h34: sine=10'h3D3;

- 6'h35: sine=10'h3DA;

- 6'h36: sine=10'h3E0;

- 6'h37: sine=10'h3E6;

- 6'h38: sine=10'h3EB;

- 6'h39: sine=10'h3F0;

- 6'h3a: sine=10'h3F3;

- 6'h3b: sine=10'h3F7;

- 6'h3c: sine=10'h3FA;

- 6'h3d: sine=10'h3FC;

- 6'h3e: sine=10'h3FE;

- 6'h3f: sine=10'h3FF;

- endcase

- endmodule

全部資料51hei下載地址:

FIR_Filter.zip

(1.14 MB, 下載次數: 28)

FIR_Filter.zip

(1.14 MB, 下載次數: 28)

2019-4-17 14:01 上傳

點擊文件名下載附件

|