- 設(shè)計(jì)一個(gè)數(shù)字式競(jìng)賽搶答器,可以判斷第一輪搶答者,并具備計(jì)分功能。

- 搶答器可以容納4組參賽者同時(shí)搶答,每組設(shè)置1個(gè)按鈕供搶答者使用。設(shè)置搶答器使能信號(hào),當(dāng)此信號(hào)有效時(shí),若參賽者按下?lián)尨痖_關(guān),則搶答器能判斷出第一搶答者并指示該組搶答成功,其他組參賽者的搶答者的搶答開關(guān)不起作用。若提前搶答,則對(duì)相應(yīng)的參賽者發(fā)出報(bào)警。

- 系統(tǒng)具有清零功能。當(dāng)清零復(fù)位信號(hào)有效時(shí),搶答器對(duì)前一輪搶答的第一搶答者判斷結(jié)果進(jìn)行清零,恢復(fù)為初始狀態(tài)。

- 數(shù)字式競(jìng)賽搶答器還具有計(jì)分功能。如果搶答成功的參賽者滿足得分條件,則增加相應(yīng)的分?jǐn)?shù),答錯(cuò)不扣分。

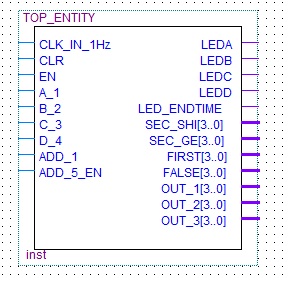

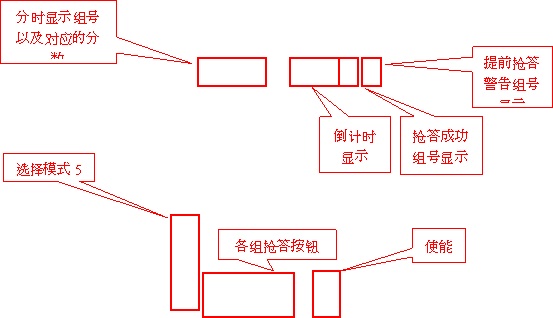

(二)系統(tǒng)設(shè)計(jì)方案根據(jù)系統(tǒng)設(shè)計(jì)要求可知,系統(tǒng)由4個(gè)主要的電路模塊組成,分別是第一判斷電路、計(jì)分電路、20s倒計(jì)時(shí)電路和顯示電路。   其中,第一判斷電路主要完成最快搶答者的判斷功能;計(jì)分電路存儲(chǔ)每組競(jìng)賽者的分?jǐn)?shù);顯示電路則顯示搶答器的狀態(tài)和各組的分?jǐn)?shù)。因此,數(shù)字式競(jìng)賽搶答器的輸入信號(hào)包括復(fù)位信號(hào)CLR、搶答器使能信號(hào)EN_KEY_IN、4組參賽者的搶答按鈕A_1/B_2/C_3/D_4以及加分信號(hào)ADD_1,加5分使能信號(hào)ADD_5_EN;輸出信號(hào)包括4組參賽者搶答狀態(tài)的顯示LEDx(x表示參賽者編號(hào))及其對(duì)應(yīng)的得分SCOREX、搶答器搶答成功的組別顯示,最先搶答組顯示FIRST[3..0],提前搶答組顯示FALSE[3..0],輪流輸出各組號(hào)以及分?jǐn)?shù)OUT_1,OUT_2,OUT_3等。系統(tǒng)框圖如圖所示:

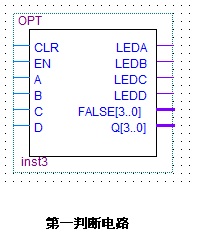

1. 搶答器的工作流程如下:如果參賽者在搶答器使能信號(hào)EN有效前按下?lián)尨鸢粹o,報(bào)警信號(hào)FALSE[3..0]的對(duì)應(yīng)位輸出高電平,以示警告;當(dāng)EN信號(hào)有效時(shí),搶答器開始工作,將報(bào)警信號(hào)FALSE清零,A、B、C、D,4個(gè)搶答者誰先按下?lián)尨鸢粹o,則搶答成功,對(duì)應(yīng)的顯示燈LEDx亮起,并通過顯示電路模塊顯示其參賽編FIRST[3..0];搶答成功的選手進(jìn)入答題階段,如正確回答問題,則加分信號(hào)ADD有效,計(jì)分模塊給相應(yīng)的參賽組加分,每個(gè)參賽組得分的個(gè)位、十位、百位分別通過信號(hào)OUT_BCD1[3..0]、OUT_BCD2[3..0]、OUT_BCD3[3..0]、顯示。 如果復(fù)位信號(hào)CLR有效,使得搶答器在下一輪搶答前,其搶答成功的組別判斷恢復(fù)為始狀態(tài),以便重新開始新一輪搶答。復(fù)位信號(hào)不改變競(jìng)賽者的現(xiàn)有得分。 2.流程圖:(三)主要模塊設(shè)計(jì)1.0 第一判斷電路第一判斷電路模塊具有第一搶答信號(hào)的鑒別和鎖存功能,其電路框圖如圖所示。 其中,CLR為復(fù)位信號(hào),當(dāng)該信號(hào)高電平有效時(shí),電路無論處于何種狀態(tài)都恢復(fù)為初始狀態(tài)即所有的輸出信號(hào)都為0;EN為搶答使能信號(hào),該信號(hào)高電平有效;A、B、C、D為搶答按鈕,高電平有效。  當(dāng)使能信號(hào)EN為低電平時(shí),如果有參賽者按下?lián)尨鸢粹o,則提前搶答報(bào)警信號(hào)FALSE[3.0]的對(duì)應(yīng)位輸出高電平,以示警告;當(dāng)使能信號(hào)EN為高電平時(shí),首先將提前搶答報(bào)警信號(hào)FALSE [3.0]復(fù)位清零,然后根據(jù)選手按下?lián)尨鸢粹oA、B、C、D的先后順廳選擇最先搶答的信號(hào),其對(duì)應(yīng)的搶答狀態(tài)顯示信號(hào)LEDA~LEDD輸出高電平,搶答成功組別編號(hào)由信號(hào)Q[3..0]輸出,并鎖存搶答器此時(shí)的 狀態(tài),直到清零信號(hào)有效為止。在每一輪新的搶答之前,都要使用復(fù)位清零信號(hào)CLR,清除上一輪搶答對(duì)判斷電路留下的使用痕跡,使電路恢復(fù)初始狀態(tài)。

1.1 第一判斷電路波形仿真圖

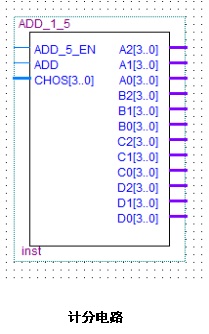

2.0 計(jì)分電路  計(jì)分電路在參賽者搶答成功后,根據(jù)其比賽情況進(jìn)行比較分?jǐn)?shù)的調(diào)整,其電路框圖如右圖所示。該模塊輸入信號(hào)為加分信號(hào)ADD_1和組別選擇信號(hào)CHOS[3.0]。 其中加分信號(hào)ADD_1高電平有效,有效時(shí)對(duì)組別選擇信號(hào)CHOS[3..0]選擇的參數(shù)組進(jìn)行加分;組別選擇輸入信號(hào)CHOS[3..0]即第一判斷電路模塊的輸出信號(hào)Q [3.0]。輸出信號(hào)分別對(duì)應(yīng)4組競(jìng)賽者的得分,以百分制表示。每組分?jǐn)?shù)在比賽開始時(shí)預(yù)設(shè)為100分,每答對(duì)1題(即加分選擇信號(hào)對(duì)相應(yīng)參賽組有效)加1分,答錯(cuò)不扣分。得分的各位、十位、百位表示為寬為4的邏輯矢量,使之方便與顯示電路級(jí)聯(lián),從而輸出比賽得分。 當(dāng)加5分使能信號(hào)ADD_5_EN為高電平時(shí)ADD每按一次加5分

2.1 計(jì)分電路波形仿真圖

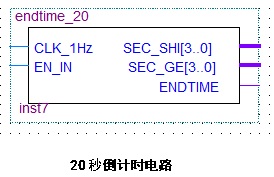

3.0 倒計(jì)時(shí)電路倒計(jì)時(shí)電路用來記錄正常搶答開始后的時(shí)間,定時(shí)為20秒,在20秒內(nèi)搶答有效,否則該題作廢。其電路圖如右圖:

其中,CLK_1Hz是時(shí)鐘信號(hào),頻率為1Hz,用來計(jì)時(shí),間隔為1秒;EN_IN是使能信號(hào),高電平有效開始倒計(jì)時(shí),ENDTIME輸出信號(hào),用來提示時(shí)間到,連接LED燈,當(dāng)時(shí)間為0時(shí)輸出高電平,led燈點(diǎn)亮。SEC_SHI[3..0]、SEC_GE[3..0]分別是倒計(jì)時(shí)的十位和各位,連接帶譯碼器的數(shù)碼管,用來顯示倒計(jì)時(shí)的時(shí)間。

3.1 倒計(jì)時(shí)電路波形仿真圖

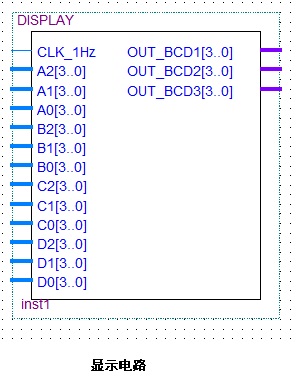

4.0 顯示電路  顯示電路用來輪流顯示各組的得分情況。由于實(shí)驗(yàn)箱數(shù)碼管有限,所以采用了數(shù)碼管分時(shí)復(fù)用的方法來顯示各組的得分情況。其電路框圖如右圖:

顯示電路中A2[3..0]、A1[3..0]、A0[3..0];B2[3..0]、B1[3..0]、B0[3..0];C2[3..0]、C1[3..0]、C0[3..0]。是各組分?jǐn)?shù)的百位、十位、以及各位。OUT_BCD1[3..0]、OUT_BCD2[3..0]、OUT_BCD3[3..0]用來輸出至帶有譯碼器的數(shù)碼管,用于分時(shí)顯示各組號(hào)以及對(duì)應(yīng)的分?jǐn)?shù)。CLK_1Hz是輸入的時(shí)鐘信號(hào),頻率為1Hz,用來間隔1秒輪流顯示。 其分時(shí)顯示流程如下: 4.1 顯示電路波形仿真

4.2顯示電路分時(shí)顯示各組分?jǐn)?shù)流程圖:

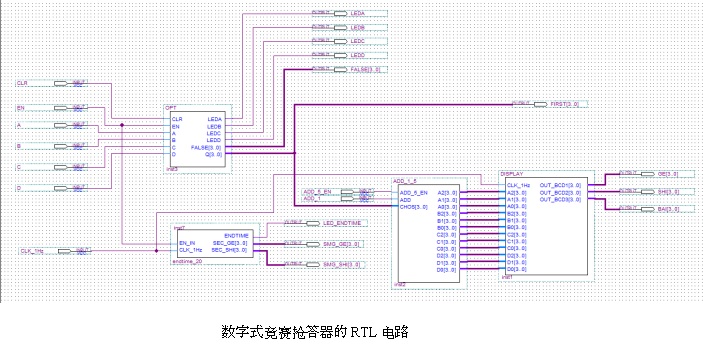

(四)系統(tǒng)整體原理圖 上述VHDL源程序構(gòu)成了一個(gè)具有搶答、計(jì)分、倒計(jì)時(shí)警報(bào)功能的數(shù)字系統(tǒng),通過仿真生成的RTL電路如圖所示:

圖中,輸出FALSE[3..0]、GE[3..0] 、SHI[3..0]、BAI[3..0] 、FIRST[3..0]、SMG_GE[3..0] 、SMG_SHI[3..0]還需要通過LED共陰極譯碼器譯碼顯示為十進(jìn)制數(shù),譯碼顯示電路部分在此略過。值得注意的是第一搶答判斷電路模塊的輸出信號(hào)Q[3..0],它既是整個(gè)數(shù)字式搶答器輸出的一部分,顯示搶答成功的選手編號(hào),又作為計(jì)分模塊的輸入信號(hào),以它為依據(jù)對(duì)相應(yīng)的選手進(jìn)行加分操作。

(五)系統(tǒng)波形仿真第一搶答判斷模塊的仿真波形如下圖所示。從圖中可以看出,當(dāng)清零復(fù)位信號(hào)CLR高電平有效時(shí),電路狀態(tài)立刻被恢復(fù)為全0的初始狀態(tài)。在搶答使能信號(hào)無效時(shí)搶答,輸出警告信號(hào),提前搶答者對(duì)應(yīng)的組號(hào)會(huì)用數(shù)碼管輸出,以示警告。 當(dāng)搶答使能信號(hào)高電平有效時(shí),最先搶答的選手對(duì)應(yīng)的顯示燈LEDx亮起,Q[3..0]輸出搶答成功的選手編號(hào)。仿真結(jié)果與系統(tǒng)設(shè)計(jì)要求的功能相吻合。 輸入信號(hào)CHOS[3.0]以十進(jìn)制的形式表示,1,2,3,4,8分別代表選擇AB、C、D4組選手在加分信號(hào)ADD_1的上升沿對(duì)選中的參賽者進(jìn)行加分,從高至低依次為百位、十位、個(gè)位。 1

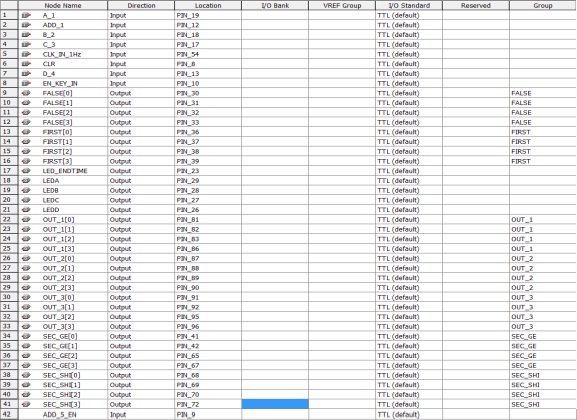

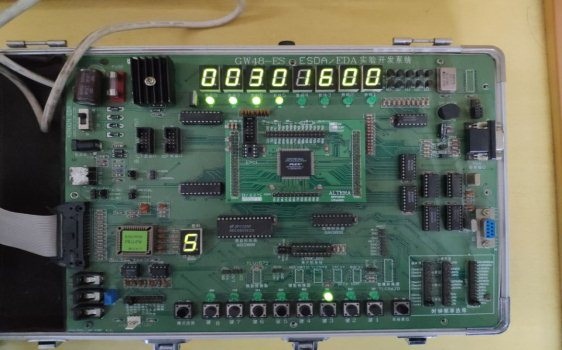

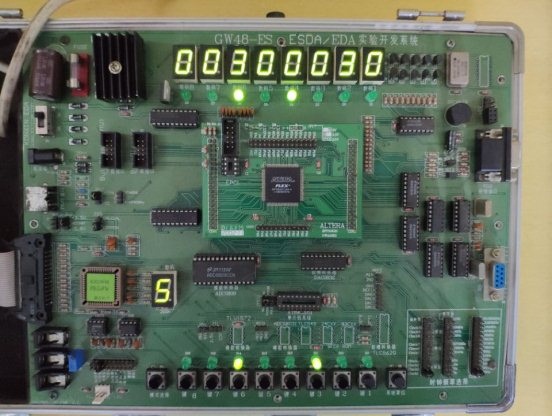

(七)模式選擇根據(jù)實(shí)際情況,應(yīng)選擇:模式5. 選擇理由:模式5帶有譯碼器芯片,可以減少譯碼電路。帶有對(duì)應(yīng)的led燈以及數(shù)碼管,便于顯示對(duì)應(yīng)的組號(hào)。同時(shí)模式5有8個(gè)鍵控高低電平發(fā)生器,可以滿足搶答器電路的需求。  (八)引腳綁定 (八)引腳綁定

(九)試驗(yàn)箱測(cè)試圖 【1】開始搶答。   【2】3號(hào)組搶答成功。  【3】進(jìn)行加分,加5分。 【4】清零,準(zhǔn)備下一次搶答。

(十)總結(jié):于個(gè)人,通過這次設(shè)計(jì),我進(jìn)一步加深了對(duì)電子設(shè)計(jì)的了解。并進(jìn)一步熟練了對(duì)QuartusII軟件的操作,基本掌握了VHDL這門硬件編程語言。EDA也不像學(xué)習(xí)理論般那么空洞,有了更加貼切的了解及運(yùn)用。做設(shè)計(jì)時(shí),先查閱相關(guān)知識(shí),把原理吃透,確定一個(gè)大的設(shè)計(jì)方向,在按照這個(gè)方向分模塊的把要實(shí)現(xiàn)的功能用流程圖的形式展示。最后參照每個(gè)模塊把輸入和輸出引腳設(shè)定,運(yùn)用我們所學(xué)的VHDL語言進(jìn)行編程。總之,通過這次的設(shè)計(jì),進(jìn)一步了解了EDA技術(shù),收獲很大,對(duì)軟件編程、排錯(cuò)調(diào)試、相關(guān)儀器設(shè)備的使用技能等方面得到較全面的鍛煉和提高

- 程序:

- --頂層模塊的VHDL

- LIBRARY IEEE;

- USE IEEE.STD_LOGIC_1164.ALL;

- ENTITY TOP_ENTITY IS

- PORT

- (

- CLK_IN_1Hz:IN STD_LOGIC;

- CLR:IN STD_LOGIC; --清零信號(hào)

- EN_KEY_IN:IN STD_LOGIC; --搶答開始信號(hào) 高電平有效

- A_1,B_2,C_3,D_4:IN STD_LOGIC;

- ADD_1:IN STD_LOGIC; --加分信號(hào)

- LEDA,LEDB,LEDC,LEDD,LED_ENDTIME:OUT STD_LOGIC;

- SEC_SHI:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

- SEC_GE:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

- FIRST:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

- FALSE:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

- OUT_1:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); --顯示個(gè)位 十位 百位

- OUT_2:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

- OUT_3:OUT STD_LOGIC_VECTOR(3 DOWNTO 0)

- );

- END ENTITY TOP_ENTITY;

- ARCHITECTURE RTL OF TOP_ENTITY IS

- COMPONENT OPT IS

- PORT (

- CLR:IN STD_LOGIC; --復(fù)位信號(hào)

- EN :IN STD_LOGIC; --搶答使能信號(hào)

- A,B,C,D:IN STD_LOGIC; --搶答按鈕

- LEDA:OUT STD_LOGIC;

- LEDB:OUT STD_LOGIC;

- LEDC:OUT STD_LOGIC;

- LEDD:OUT STD_LOGIC;

- FALSE:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); --提前搶答警報(bào)

- Q:OUT STD_LOGIC_VECTOR(3 DOWNTO 0) --搶答成功組顯示

- );

- END COMPONENT OPT;

- COMPONENT COUNTER IS

- PORT

- (

- ADD_1:IN STD_LOGIC; --加分信號(hào)

- CHOS:IN STD_LOGIC_VECTOR(3 DOWNTO 0); --參賽組選擇信號(hào)

- A2,A1,A0:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); --各組計(jì)分信號(hào)

- B2,B1,B0:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

- C2,C1,C0:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

- D2,D1,D0:OUT STD_LOGIC_VECTOR(3 DOWNTO 0)

- );

- END COMPONENT COUNTER;

- COMPONENT OUTPUT IS --提前搶答警告

- PORT

- (

- DIN:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

- DOUT:OUT STD_LOGIC_VECTOR(3 DOWNTO 0)

- );

- END COMPONENT OUTPUT;

- COMPONENT endtime_20 IS

- PORT

- (

- CLK_1Hz :IN STD_LOGIC; --時(shí)鐘信號(hào)

- EN_in :IN STD_LOGIC; --使能 計(jì)時(shí)開始

- SEC_SHI:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); --秒各位 BCD 4位2進(jìn)制輸出

- SEC_GE:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); --秒百位 BCD 4位2進(jìn)制輸出

- ENDTIME:OUT STD_LOGIC --時(shí)間到警報(bào) 接蜂鳴器

- );

- END COMPONENT endtime_20;

- COMPONENT DISPLAY IS

- PORT

- (

- CLK_1Hz:IN STD_LOGIC;

- A2,A1,A0:IN STD_LOGIC_VECTOR(3 DOWNTO 0); --各組計(jì)分信號(hào)

- B2,B1,B0:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

- C2,C1,C0:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

- D2,D1,D0:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

- OUT_BCD1:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); --輸出個(gè)十百位

- OUT_BCD2:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

- OUT_BCD3:OUT STD_LOGIC_VECTOR(3 DOWNTO 0)

- );

- END COMPONENT DISPLAY;

- SIGNAL Q:STD_LOGIC_VECTOR(3 DOWNTO 0);

- SIGNAL AA2,AA1,AA0:STD_LOGIC_VECTOR(3 DOWNTO 0);

- SIGNAL BB2,BB1,BB0:STD_LOGIC_VECTOR(3 DOWNTO 0);

- SIGNAL CC2,CC1,CC0:STD_LOGIC_VECTOR(3 DOWNTO 0);

- SIGNAL DD2,DD1,DD0:STD_LOGIC_VECTOR(3 DOWNTO 0);

- BEGIN

- U1:OPT PORT MAP(CLR,EN_KEY_IN,A_1,B_2,C_3,D_4,LEDA,LEDB,LEDC,LEDD,FALSE,Q);

- U2:COUNTER PORT MAP(ADD_1,Q,AA2,AA1,AA0,BB2,BB1,BB0,CC2,CC1,CC0,DD2,DD1,DD0);

- U3:OUTPUT PORT MAP(Q,FIRST);

- U4:DISPLAY PORT MAP(CLK_IN_1Hz,AA2,AA1,AA0,BB2,BB1,BB0,CC2,CC1,CC0,DD2,DD1,DD0,OUT_1,OUT_2,OUT_3);

- U5:endtime_20 PORT MAP(CLK_IN_1Hz,EN_KEY_IN,SEC_SHI,SEC_GE,LED_ENDTIME);

- END ARCHITECTURE RTL;

- --第一搶答判斷 電路 的VHDL程序

- LIBRARY IEEE;

- USE IEEE.STD_LOGIC_1164.ALL;

- ENTITY OPT IS

- PORT (

- CLR:IN STD_LOGIC; --復(fù)位信號(hào)

- EN :IN STD_LOGIC; --搶答使能信號(hào)

- A,B,C,D:IN STD_LOGIC; --搶答按鈕

- LEDA:OUT STD_LOGIC:='0'; --搶答成功 對(duì)應(yīng)組的led燈點(diǎn)亮

- LEDB:OUT STD_LOGIC:='0';

- LEDC:OUT STD_LOGIC:='0';

- LEDD:OUT STD_LOGIC:='0';

- FALSE:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); --提前搶答警報(bào)

- Q:OUT STD_LOGIC_VECTOR(3 DOWNTO 0) --搶答成功組顯示

- );

- END ENTITY OPT;

- ARCHITECTURE RTL OF OPT IS

- SIGNAL TMP:STD_LOGIC_VECTOR(3 DOWNTO 0);

- SIGNAL TAG:STD_LOGIC;

- BEGIN

- TMP<=A&B&C&D;

- PROCESS(CLR,EN,A,B,C,D,TMP,TAG)

- BEGIN --設(shè)置鎖存標(biāo)志位

- IF CLR='1' THEN

- Q<="0000";

- LEDA<='0';

- LEDB<='0';

- LEDC<='0';

- LEDD<='0';

- FALSE<="0000";

- TAG<='0';

- ELSIF EN='0' THEN

- IF TAG='0' THEN

- IF A='1' THEN

- FALSE(0)<='1';

- END IF;

- IF B='1' THEN

- FALSE(1)<='1';

- END IF;

- IF C='1' THEN

- FALSE(2)<='1';

- END IF;

- IF D='1' THEN

- FALSE(3)<='1';

- END IF;

- END IF;

- ELSE

- FALSE<="0000";

- IF TAG='0' THEN

- IF TMP="1000" THEN

- LEDA<='1';

- LEDB<='0';

- LEDC<='0';

- LEDD<='0';

- Q<="0001";

- TAG<='1';

- ELSIF TMP="0100"THEN

- LEDA<='0';

- LEDB<='1';

- LEDC<='0';

- LEDD<='0';

- Q<="0010";

- TAG<='1';

- ELSIF TMP="0010"THEN

- LEDA<='0';

- LEDB<='0';

- LEDC<='1';

- LEDD<='0';

- Q<="0011";

- TAG<='1';

- ELSIF TMP="0001"THEN

- LEDA<='0';

- LEDB<='0';

- LEDC<='0';

- LEDD<='1';

- Q<="0100";

- TAG<='1';

- ELSE

- LEDA<='Z';

- LEDB<='Z';

- LEDC<='Z';

- LEDD<='Z';

- Q<="ZZZZ";

- END IF;

- END IF;

- END IF;

- END PROCESS;

- END RTL;

-

- --計(jì)分電路的VHDL程序 ADD_1 ADD_5

- LIBRARY IEEE;

- USE IEEE.STD_LOGIC_1164.ALL;

- USE IEEE.STD_LOGIC_UNSIGNED.ALL;

- USE IEEE.STD_LOGIC_ARITH.ALL;

- ENTITY ADD_1_5 IS

- PORT

- (

- ADD_5_EN,ADD:IN STD_LOGIC; --加分信號(hào)

- CHOS:IN STD_LOGIC_VECTOR(3 DOWNTO 0); --參賽組選擇信號(hào)

- A2,A1,A0:OUT STD_LOGIC_VECTOR(3 DOWNTO 0):="0000"; --各組計(jì)分信號(hào)

- B2,B1,B0:OUT STD_LOGIC_VECTOR(3 DOWNTO 0):="0000";

- C2,C1,C0:OUT STD_LOGIC_VECTOR(3 DOWNTO 0):="0000";

- D2,D1,D0:OUT STD_LOGIC_VECTOR(3 DOWNTO 0):="0000"

- );

- END ENTITY ADD_1_5;

- ARCHITECTURE RTL OF ADD_1_5 IS

- BEGIN

- PROCESS(ADD,ADD_5_EN,CHOS)

- VARIABLE POINTS_A2,POINTS_A1,POINTS_A0:STD_LOGIC_VECTOR(3 DOWNTO 0):="0000";

- VARIABLE POINTS_B2,POINTS_B1,POINTS_B0:STD_LOGIC_VECTOR(3 DOWNTO 0):="0000";

- VARIABLE POINTS_C2,POINTS_C1,POINTS_C0:STD_LOGIC_VECTOR(3 DOWNTO 0):="0000";

- VARIABLE POINTS_D2,POINTS_D1,POINTS_D0:STD_LOGIC_VECTOR(3 DOWNTO 0):="0000";

- BEGIN

- IF ADD_5_EN='1' THEN

- IF ADD='1' AND ADD'EVENT THEN

- CASE CHOS IS

- WHEN "0001" => FOR I IN 0 TO 4 LOOP

- IF POINTS_A0="1001" THEN

- POINTS_A0:="0000";

- IF POINTS_A1="1001" THEN

- POINTS_A1:="0000";

- IF POINTS_A2="1001" THEN --十位分9

- POINTS_A2:="0000"; --十位清零

- ELSE

- POINTS_A2:=POINTS_A2+'1';

- END IF;

- ELSE

- POINTS_A1:=POINTS_A1+'1';

- END IF;

- ELSE

- POINTS_A0:=POINTS_A0+'1';

- END IF;

- END LOOP;

- WHEN "0010" => FOR I IN 0 TO 4 LOOP

- IF POINTS_B0="1001" THEN

- POINTS_B0:="0000";

- IF POINTS_B1="1001" THEN

- POINTS_B1:="0000";

- IF POINTS_B2="1001" THEN --十位分9

- POINTS_B2:="0000"; --十位清零

- ELSE

- POINTS_B2:=POINTS_B2+'1';

- END IF;

- ELSE

- POINTS_B1:=POINTS_B1+'1';

- END IF;

- ELSE

- POINTS_B0:=POINTS_B0+'1';

- END IF;

- END LOOP;

- WHEN "0011" => FOR I IN 0 TO 4 LOOP

- IF POINTS_C0="1001" THEN

- POINTS_C0:="0000";

- IF POINTS_C1="1001" THEN

- POINTS_C1:="0000";

- IF POINTS_C2="1001" THEN --十位分9

- POINTS_C2:="0000"; --十位清零

- ELSE

- POINTS_C2:=POINTS_C2+'1';

- END IF;

- ELSE

- POINTS_C1:=POINTS_C1+'1';

- END IF;

- ELSE

- POINTS_C0:=POINTS_C0+'1';

- END IF;

- END LOOP;

- WHEN "0100" => FOR I IN 0 TO 4 LOOP

- IF POINTS_D0="1001" THEN

- POINTS_D0:="0000";

- IF POINTS_D1="1001" THEN

- POINTS_D1:="0000";

- IF POINTS_D2="1001" THEN --十位分9

- POINTS_D2:="0000"; --十位清零

- ELSE

- POINTS_D2:=POINTS_D2+'1';

- END IF;

- ELSE

- POINTS_D1:=POINTS_D1+'1';

- END IF;

- ELSE

- POINTS_D0:=POINTS_D0+'1';

- END IF;

- END LOOP;

- WHEN OTHERS => NULL;

- END CASE;

- END IF;

- ELSE

- IF ADD='1' AND ADD'EVENT THEN

- CASE CHOS IS

- WHEN "0001" => IF POINTS_A0="1001" THEN

- POINTS_A0:="0000";

- IF POINTS_A1="1001" THEN

- POINTS_A1:="0000";

- IF POINTS_A2="1001" THEN --十位分9

- POINTS_A2:="0000"; --十位清零

- ELSE

- POINTS_A2:=POINTS_A2+'1';

- END IF;

- ELSE

- POINTS_A1:=POINTS_A1+'1';

- END IF;

- ELSE

- POINTS_A0:=POINTS_A0+'1';

- END IF;

- WHEN "0010" => IF POINTS_B0="1001" THEN

- POINTS_B0:="0000";

- IF POINTS_B1="1001" THEN

- POINTS_B1:="0000";

- IF POINTS_B2="1001" THEN --十位分9

- POINTS_B2:="0000"; --十位清零

- ELSE

- POINTS_B2:=POINTS_B2+'1';

- END IF;

- ELSE

- POINTS_B1:=POINTS_B1+'1';

- END IF;

- ELSE

- POINTS_B0:=POINTS_B0+'1';

- END IF;

- WHEN "0011" => IF POINTS_C0="1001" THEN

- POINTS_C0:="0000";

- IF POINTS_C1="1001" THEN

- POINTS_C1:="0000";

- IF POINTS_C2="1001" THEN --十位分9

- POINTS_C2:="0000"; --十位清零

- ELSE

- POINTS_C2:=POINTS_C2+'1';

- END IF;

- ELSE

- POINTS_C1:=POINTS_C1+'1';

- END IF;

- ELSE

- POINTS_C0:=POINTS_C0+'1';

- END IF;

- WHEN "0100" => IF POINTS_D0="1001" THEN

- POINTS_D0:="0000";

- IF POINTS_D1="1001" THEN

- POINTS_D1:="0000";

- IF POINTS_D2="1001" THEN --十位分9

- POINTS_D2:="0000"; --十位清零

- ELSE

- POINTS_D2:=POINTS_D2+'1';

- END IF;

- ELSE

- POINTS_D1:=POINTS_D1+'1';

- END IF;

- ELSE

- POINTS_D0:=POINTS_D0+'1';

- END IF;

- WHEN OTHERS => NULL;

- END CASE;

- END IF;

- END IF;

- A2<=POINTS_A2;A1<=POINTS_A1;A0<=POINTS_A0;

- B2<=POINTS_B2;B1<=POINTS_B1;B0<=POINTS_B0;

- C2<=POINTS_C2;C1<=POINTS_C1;C0<=POINTS_C0;

- D2<=POINTS_D2;D1<=POINTS_D1;D0<=POINTS_D0;

- END PROCESS;

- END RTL;

- --顯示提前搶答組電路的VHDL程序

- LIBRARY IEEE;

- USE IEEE.STD_LOGIC_1164.ALL;

- ENTITY OUTPUT IS

- PORT

- (

- DIN:IN STD_LOGIC_VECTOR(3 DOWNTO 0); --輸入提前搶答的組號(hào)

- DOUT:OUT STD_LOGIC_VECTOR(3 DOWNTO 0) --輸出提前搶答的組號(hào)

- );

- END ENTITY OUTPUT;

- ARCHITECTURE RTL OF OUTPUT IS

- BEGIN

- PROCESS(DIN)

- BEGIN

- CASE DIN IS

- WHEN"0001"=>DOUT<="0001";

- WHEN"0010"=>DOUT<="0010";

- WHEN"0011"=>DOUT<="0011";

- WHEN"0100"=>DOUT<="0100";

- WHEN OTHERS=>DOUT<="0000";

- END CASE;

- END PROCESS;

- END RTL;

- --動(dòng)態(tài)各組分?jǐn)?shù)顯示 輪流顯示

- LIBRARY IEEE;

- USE IEEE.STD_LOGIC_1164.ALL;

- USE IEEE.STD_LOGIC_UNSIGNED.ALL;

- ENTITY DISPLAY IS

- PORT

- (

- CLK_1Hz:IN STD_LOGIC;

- A2,A1,A0:IN STD_LOGIC_VECTOR(3 DOWNTO 0); --各組計(jì)分信號(hào)

- B2,B1,B0:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

- C2,C1,C0:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

- D2,D1,D0:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

-

- OUT_BCD1:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); --輸出個(gè)十百位

- OUT_BCD2:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

- OUT_BCD3:OUT STD_LOGIC_VECTOR(3 DOWNTO 0)

- );

- END ENTITY DISPLAY;

- ARCHITECTURE BEHAVE OF DISPLAY IS

- SIGNAL FILG:STD_LOGIC_VECTOR(2 DOWNTO 0):="000";

- BEGIN

- PROCESS(CLK_1Hz,FILG)

- BEGIN

- IF CLK_1Hz'EVENT AND CLK_1Hz='1' THEN

- FILG<=FILG+'1';

- END IF;

-

- CASE FILG IS --動(dòng)態(tài)循環(huán)顯示

- WHEN "000" => OUT_BCD1<="0001"; --第一輪顯示組號(hào)

- WHEN "001" => OUT_BCD1<=A0; --第二輪顯示分?jǐn)?shù)

- OUT_BCD2<=A1;

- OUT_BCD3<=A2;

-

- WHEN "010" => OUT_BCD1<="0010";

- WHEN "011" => OUT_BCD1<=B0;

- OUT_BCD2<=B1;

- OUT_BCD3<=B2;

-

- WHEN "100" => OUT_BCD1<="0011";

- WHEN "101" => OUT_BCD1<=C0;

- OUT_BCD2<=C1;

- OUT_BCD3<=C2;

-

- WHEN "110" => OUT_BCD1<="0100";

- WHEN "111" => OUT_BCD1<=D0;

- OUT_BCD2<=D1;

- OUT_BCD3<=D2;

- END CASE;

- END PROCESS;

- END ARCHITECTURE BEHAVE;

-

- --20秒倒計(jì)時(shí) 顯示

- LIBRARY IEEE;

- USE IEEE.STD_LOGIC_1164.ALL;

- USE IEEE.STD_LOGIC_UNSIGNED.ALL;

- USE IEEE.STD_LOGIC_ARITH.ALL;

- ENTITY endtime_20 IS

- PORT

- (

- CLK_1Hz :IN STD_LOGIC; --時(shí)鐘信號(hào)

- EN_IN :IN STD_LOGIC; --使能 計(jì)時(shí)開始

- SEC_SHI:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); --秒各位 BCD 4位2進(jìn)制輸出

- SEC_GE:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); --秒百位 BCD 4位2進(jìn)制輸出

- ENDTIME:OUT STD_LOGIC --時(shí)間到警報(bào) 接蜂鳴器

- );

- END ENTITY endtime_20 ;

- ARCHITECTURE BEHAVE OF endtime_20 IS

- SIGNAL CONTER_20:STD_LOGIC_VECTOR(4 DOWNTO 0):="00000";

- BEGIN

- PROCESS(CLK_1Hz,EN_IN)

- BEGIN

- IF EN_IN='1' THEN

- IF CLK_1Hz='1' AND CLK_1Hz'EVENT THEN

- CASE CONTER_20 IS

- WHEN "00000" =>SEC_SHI<="0010"; --20

- SEC_GE<="0000";

- CONTER_20<=CONTER_20+'1';

-

- ENDTIME<='0';

- WHEN "00001" =>SEC_GE<="1001";--19

- SEC_SHI<="0001";

- CONTER_20<=CONTER_20+'1';

-

- WHEN "00010" =>SEC_GE<="1000";--18

- SEC_SHI<="0001";

- CONTER_20<=CONTER_20+'1';

-

- WHEN "00011" =>SEC_GE<="0111";--17

- SEC_SHI<="0001";

- CONTER_20<=CONTER_20+'1';

-

- WHEN "00100" =>SEC_GE<="0110";--16

- SEC_SHI<="0001";

- CONTER_20<=CONTER_20+'1';

-

- WHEN "00101" =>SEC_GE<="0101";--15

- SEC_SHI<="0001";

- CONTER_20<=CONTER_20+'1';

-

- WHEN "00110" =>SEC_GE<="0100";--14

- SEC_SHI<="0001";

- CONTER_20<=CONTER_20+'1';

- ……………………

- …………限于本文篇幅 余下代碼請(qǐng)從51黑下載附件…………

全部資料51hei下載地址:

END_DESITN_SECOND.rar

(3.36 MB, 下載次數(shù): 54)

END_DESITN_SECOND.rar

(3.36 MB, 下載次數(shù): 54)

2019-12-12 08:27 上傳

點(diǎn)擊文件名下載附件

vhdl數(shù)字搶答器 下載積分: 黑幣 -5

|