數字電子鐘是一種用數字顯示秒、分、時、日的計時裝置,與傳統的機械鐘相比,它具有走時準確,顯示直觀、無機械傳動裝置、具有更長的使用壽命等優點,因而得到了廣泛的應用。數字電子鐘由以下幾部分組成:秒脈沖發生器、校時電路、六十進制秒、二十四進制計時計數器。由設計要求可知我們還需要一個七進制計時計數器。

數字電子鐘要完成顯示需要6個數碼管,然后要實現時、分、秒的計時需要60進制計數器和24進制計數器。頻率振蕩器可以由晶體振蕩器分頻來提供,也可以由555定時來產生脈沖并分頻為1HZ。方案可以采用74LS160同步十進制加法計數器或采用74LS161十六進制計數器或74LS192十進制異步清零計數器,而小時的24進制也可以采用上述方案。由于我對74LS160的功能比較熟悉,故我分別用六塊74LS160芯片來實現,兩個60進制和一個24進制的秒、分、時計數。

方案一:石英晶體振蕩器

工作原理:由晶體振蕩器產生的脈沖經集成電路后變成1Hz脈沖,再經74LS160計數器分頻得到了所需要的1Hz穩定脈沖。但晶體振蕩器的電路圖比較復雜,而且晶體振蕩器的中阻值要求10MHz以上。

方案二:555定時器

工作原理:R1=1kΩ,R2=720kΩ,C=1uF,Cf=100nF,Ri=100Ω可以直接產生1Hz的時鐘脈沖。因為通過555定時器改裝過的多諧振蕩器發出的脈沖頻率具有一定的穩定性,而且電路比晶體振蕩器簡單所以在這里我采用的是555定時器。

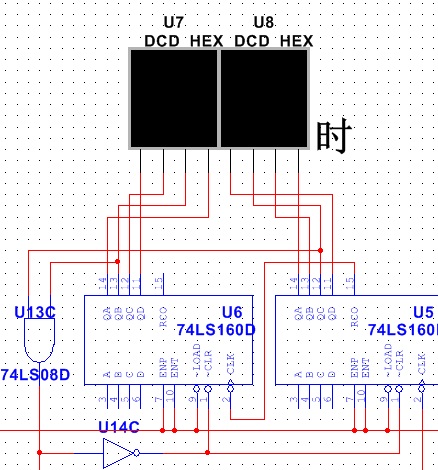

(2)時間計數器電路:時間計數電路由秒個位和秒十位計數器、分個位和分十位計數器其中秒個位和秒十位計數器、分個位和分十位計數器為60進制計數器,時個位和時十位計數器為24進制計數器。電路圖如圖2所示。

圖2. 60進制計數電路 (3)24小時計數器:由時個位和時十位計數器電路構成24進制計數器。電路圖如圖3所示。

圖3. 24進制計數電路 (4)校時電路:由于數字鐘的初始時間不一定是標準時間,而且在數字鐘的運行過程中可能出現誤差,所以需要校時電路來對“時、分”顯示數字進行校對調整。我這里有自動校正和手動校正,在設計中發現手動校正的脈沖不穩定,會有延遲的情況;所以我加了一個由脈沖自動校正時間的電路,在調時間時只需要把自動校正的開關合上,當時間走到你想要的時間時再打開自動校時開關即可。電路圖如圖4所示。

圖4.校時電路圖 (5)整點報時電路:一般時鐘都應具備整點報時電路功能,即在時間出現整點前數秒內,數字鐘會自動報時。我這里采用的是蜂鳴器在整點前的十秒內,以響鈴的方式提醒。電路圖如圖5所示。

圖5.整點報時電路

(6)秒脈沖產生器: 由振蕩器與分頻器組合產生秒脈沖信號。 理論計算:555定時器的脈沖時間是由于RC充放電確定的。 根據三要素公式  充電過程  充電時間  放電過程  放電時間  一個周期時間  頻率

首先確定C1=1uF ,R2=720K?,需要輸出頻率f=1HZ,充放電時間算為1s ,可以確定 R1=1K?。555定時器電路如圖6所示。

圖6. 555定時器電路圖

圖10.仿真波形圖

圖11. 60進制仿真電路

圖12. 24進制仿真電路

五、總結與體會 首先,在設計電路過程中,Multisim仿真軟件軟件給我們的設計提供了很大的便利,它提供大量的元器件庫,提供修改電路設計的靈活性、提供實驗室在數量、質量上難以相比的虛擬儀器、儀表,使設計時間大為縮短,設計過程更直觀、方便。 其次,在設計剛開始時我選用的是74LS192芯片,電路連接完成后運作時,每個數碼管的十位出現的是數字9而不是0,相當于它提前了一個脈沖;出現的問題主要是我們對同步置數、異步置零方面的知識沒有理解透徹,還有就是在操作過程中我們發現在計數器的進位端出現不能進位的情況,解決這些問題花了我們將近兩天的時間,最終我選擇的是74LS160芯片才沒出現以上情況,這主要還要怪我們沒有認真學好知識。

完整的Word格式文檔51黑下載地址:

文檔.doc

(323.42 KB, 下載次數: 75)

文檔.doc

(323.42 KB, 下載次數: 75)

2020-1-6 22:01 上傳

點擊文件名下載附件

下載積分: 黑幣 -5

|