③ 用EDA上的8只八段數碼管分兩屏分別顯示年、月、日和時、分、秒,即在一定時間段內顯示年、月、日(如20080101),然后在另一時間段內顯示時、分、秒(如00123625),兩個時間段能自動倒換。

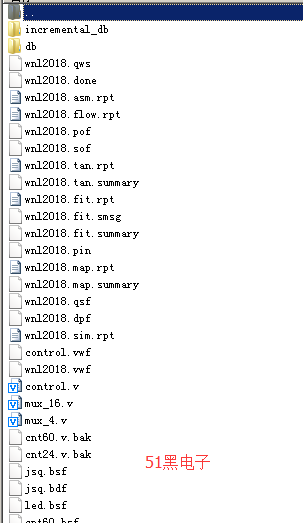

用verilogHDL語言該設計中總體包括顯示部分、計時部分、控制部分、校時部分、年月日部分以及分頻功能再加上自己的創新。然后調試出來,下載到箱驗證。

模塊(control),校時選擇模塊(mux_4)和顯示選擇模塊(mux_16)還有奇數月份報時模塊(led),分頻模塊(fenping);奇月報時模塊為創新模塊,它當在月份為奇數的時候燈光全亮,偶數的時候全滅。

當k=0時,開關j1,j2,j3校秒時分然后將信號分別送到jsq模塊的jm(校秒)、jf(校分)、js(校時)。當k=1時,開關j1,j2,j3校年月日然后將信號分別送到wnl2018模塊的jr(校日)、jy(校月)、jn(校年)。

clrn是異步清除輸入端,低電平有效;clk是時鐘輸入端,上升沿有效;jm、jf和js分別是校秒、校分、校時輸入端;qm[7..0]、qf[7..0]、qs[7..0]分別是年、月、日的輸出端;cout是進位。

clk是1秒時鐘輸入端,k1和k2是控制輸入端,當k1k2=00或11時是自動顯示模式,控制數碼顯示器用8秒鐘時間顯示年、月、日,另外8秒時鐘時間顯示時、分、秒;當k1k2=01時,僅顯示年、月、日,同時用j1,j2,和j3校秒、校分、校時;當k1k2=10時,僅顯示年、月、日,同時用j1、j2和j3校日、校月和校年;k是控制輸出端。

clrn是異步清除輸入端,低電平有效;clk是時鐘輸入端,上升沿有效;jn、jy和jr分別是校年、校月、校日輸入端;qn[15..0]、qy[7..0]、qr[7..0]分別是年、月、日的輸出端。

首先,新建一個工程,把編寫的程序模塊放入進去,再把六十計數器和二十四計數器的分別生成原件符號,然后進行原理圖編輯,再連接好24小時計數器的設計同時生成原件符號。最后把各元器件組合起來。編譯,仿真,鎖定引腳,下載無誤后再調試看看能不能實現任務里面要求的功能。

把程序下載后試驗箱上能夠正確實現年、月、日和時、分、秒的顯示和切換。也能通過調節K1和K2來調節年月日和日期的切換,新加的led燈也能實現奇數全亮偶數全滅的效果。

雖然花了很多時間去做,不過我不僅學會如何做萬年歷,而且更熟練的運用QuartusII9.0軟件,對EDA技術有更深入的認識。在做完基本要求之后還創新了一個功能。雖然我創新的思路很簡單,但是實際操作中還是遇到了很多困難,比如說自己編寫的程序無法實現預期的要求。然后我就去百度和結合自己的程序繼續編寫代碼,有時實在寫不出來,我就跑去問老師。在這次中學到了很多很多東西,也增加了自己的思考能力和動手能力。從一開始開題選題,然后再著手設計框圖,再到網上查閱相關資料,確定電路圖到最終制作成型,每一步都有自己努力的付出。剛開始我做的并不成功,不能顯示萬年歷的結果。但是我相信沒有人是一下子就可以做出來的,在成功之前的付出往往是巨大的。于是我對編寫的程序進行了認真檢查和反復更改,終于我成功的實現了所需的全部功能。這次使我懂得了理論與實際相結合是很重要的,只有理論知識是遠遠不夠的,只有把所學的理論知識與實踐相結合起來,從理論中得出結論

分頻器模塊

module fenping(clk,clk_HZ);

input clk;

output reg clk_HZ;

reg[24:0] counter;

always @(posedge clk)

begin

counter = counter + 1;

if(counter==5000000) counter = 'b0;

else if(counter<=2500000) clk_HZ = 'b0;

else clk_HZ = 'b1;

end

Endmodule

控制模塊

module control(clk,k1,k2,k);

input clk,k1,k2;

output reg k;

reg [3:0] qc;

reg rc;

always @(posedge clk)

begin qc=qc+1;

if(qc<8) rc = 0;

else rc = 1;

case ({k1,k2})

0:k = rc;

1:k = 0;

2:k = 1;

3:k = rc;

endcase

end

endmodule

校時選擇模塊

module mux_4(k,jm,jf,js,jr,jy,jn,j1,j2,j3);

input k,j1,j2,j3;

output reg jm,jf,js,jr,jy,jn;

always

begin

if(k==0) {jm,jf,js}={j1,j2,j3};

else {jr,jy,jn} = {j1,j2,j3};

end

endmodule

顯示選擇模塊

module mux_16(k,qm,qf,qs,qr,qy,qn,q);

input k;

input[7:0] qm,qf,qs,qr,qy;

input[15:0] qn;

output reg[31:0] q;

always

begin

if(k==0) begin

q[31:24] = 0;

q[23:0] = {qs,qf,qm}; end

else q={qn,qy,qr};

end

endmodule

年月日模塊

module wnl2018(clrn,clk,jn,jy,jr,qn,qy,qr);

input clrn,clk,jn,jy,jr;

output [15:0] qn;

output [7:0] qy,qr;

reg [15:0] qn;

reg[7:0] qy,qr;

reg clkn,clky;

reg [7:0] date;

reg clkn1,clkn2,clkn3;

initial begin clkn1 = 1;clkn2 = 1;clkn3 = 1;end//初始化年脈沖

initial begin qn = 'h2000;qy = 1;qr = 1;end//初始化年,月,日時間

always @(posedge (clk^jr) or negedge clrn)//日計數模塊

begin

if(~clrn) qr = 1;

else begin

if(qr==date) qr = 1;

else qr=qr+1;

if(qr[3:0] == 'ha) begin

qr[3:0] = 0;qr[7:4] = qr[7:4] + 1;end

if(qr==date) clky = 1;

else clky = 0;end

end

always @(posedge clky^jy or negedge clrn)//月計數模塊

begin

if(~clrn) qy = 1;

else begin

if(qy=='h12) qy = 1;

else qy=qy+1;

if(qy[3:0] == 'ha) begin

qy[3:0] = 0;qy[7:4] = qy[7:4] + 1;end

if(qy=='h12) clkn = 1;

else clkn = 0;end

end

always

begin

case(qy)

'h01: date = 'h31;

'h02: begin

if((qn/4==0)&(qn/100!=0)|(qn/400==0)) date = 'h29;

else date = 'h28;end

'h03: date = 'h31;

'h04: date = 'h30;

'h05: date = 'h31;

'h06: date = 'h30;

'h07: date = 'h31;

'h08: date = 'h31;

'h09: date = 'h30;

'h10: date = 'h31;

'h11: date = 'h30;

'h12: date = 'h31;

default: date = 'h30;

endcase

end

//年計數模塊

always @(posedge (clkn^jn) or negedge clrn)

begin

if(~clrn) qn[3:0] = 0;

else begin if(qn[3:0]==9) qn[3:0] = 0;

else qn[3:0] = qn[3:0] + 1;

if(qn[3:0] == 9) clkn1 = 0;

else clkn1 = 1;end

end

always @(posedge clkn1 or negedge clrn)

begin

if(~clrn) qn[7:4] = 0;

else begin if(qn[7:4]==9) qn[7:4] = 0;

else qn[7:4] = qn[7:4] + 1;

if(qn[7:4]==9) clkn2 = 0;

else clkn2 = 1;end

end

always @(posedge clkn2 or negedge clrn)

begin

if(~clrn) qn[11:8] = 0;

else begin if(qn[11:8] == 9) qn[11:8] = 0;

else qn[11:8] = qn[11:8] + 1;

if(qn[7:4] == 9) clkn3 = 0;

else clkn3 = 1;end

end

always @(posedge clkn3 or negedge clrn)

begin

if(~clrn) qn[15:12] = 2;

else if(qn[15:12]==9) qn[15:12] = 0;

else qn[15:12] = qn[15:12] + 1;

end

endmodule

Led燈模塊

module led(months,qledout);

input [7:0]months;

output reg [11:0] qledout;

always

begin

if(months%2)

begin

qledout = 'b111111111111;

end

else qledout = 'b000000000000;

end

endmodule

六十進制計數器模塊

module cnt60(clk,clrn,j,q,cout);

input clk,clrn,j;

output reg[7:0] q;

output reg cout;

always @(posedge clk^j or negedge clrn)

begin

if(~clrn) q = 0;

else begin

if(q=='h59) q= 0;

else q=q+1;

if(q[3:0]=='ha) begin

q[3:0] = 0; q[7:4]=q[7:4] + 1;end

if(q=='h59) cout = 1;

else cout = 0; end

end

endmodule

二十四進制計數器模塊

module cnt24(clk,clrn,j,q,cout);

input clk,clrn,j;

output reg [7:0] q;

output reg cout;

always @(posedge clk^j or negedge clrn)

begin

if(~clrn) q = 0;

else begin

if(q=='h23) q= 0;

else q = q+1;

if(q[3:0] == 'ha) begin

q[3:0] = 0;q[7:4] = q[7:4] + 1;end

if(q == 'h23) cout=1;

else cout = 0;end

end

Endmodule

全部資料51hei下載地址:

數字日歷.zip

(1.21 MB, 下載次數: 92)

數字日歷.zip

(1.21 MB, 下載次數: 92)

2020-11-4 20:37 上傳

點擊文件名下載附件

eda

數字日歷.doc

(202 KB, 下載次數: 44)

數字日歷.doc

(202 KB, 下載次數: 44)

2020-11-4 20:37 上傳

點擊文件名下載附件

完整報告