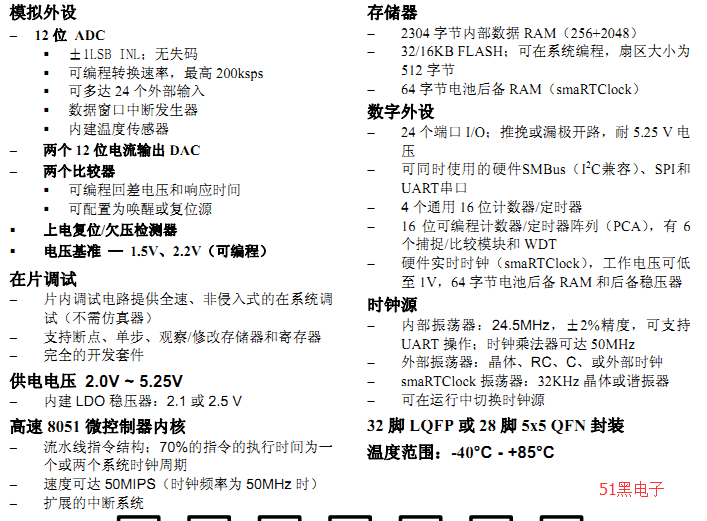

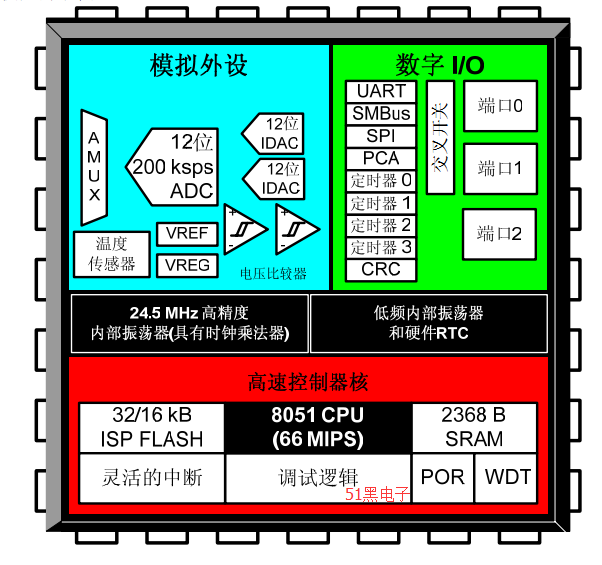

C8051F41x器件是完全集成的低功耗混合信號片上系統型 MCU。下面列出了一些主要特性,有關某一產品的具體特性參見表 1.1。

高速、流水線結構的 8051 兼容的微控制器核(可達 50MIPS)

全速、非侵入式的在系統調試接口(片內)

真 12 位 200 ksps 的24 通道 ADC,帶模擬多路器

兩個 12 位電流輸出 DAC

高精度可編程的 24.5MHz 內部振蕩器

達 32KB 的片內 FLASH 存儲器

2304 字節片內 RAM

硬件實現的SMBus/ I2C、增強型UART和增強型SPI串行接口

4 個通用的16 位定時器

具有 6 個捕捉/比較模塊和看門狗定時器功能的可編程計數器/定時器陣列(PCA)

硬件實時時鐘(smaRTClock),工作電壓可低至 1V,帶 64 字節電池后備 RAM 和后備穩壓器

硬件 CRC 引擎

片內上電復位、VDD監視器和溫度傳感器

片內電壓比較器

多達 24 個端口 I/O

具有片內上電復位、VDD監視器、看門狗定時器和時鐘振蕩器的 C8051F41x 器件是真正能獨立工作片上系統。FLASH 存儲器還具有在系統重新編程能力,可用于非易失性數據存儲,并允許現場更新8051 固件。用戶軟件對所有外設具有完全的控制,可以關斷任何一個或所有外設以節省功耗。

片內 Silicon Labs二線(C2)開發接口允許使用安裝在最終應用系統上的產品 MCU進行非侵入式(不占用片內資源)、全速、在系統調試。調試邏輯支持觀察和修改存儲器和寄存器,支持斷點、單步、運行和停機命令。在使用 C2進行調試時,所有的模擬和數字外設都可全功能運行。兩個 C2 接口引腳可以與用戶功能共享,使在系統調試功能不占用封裝引腳。

每種器件都可在工業溫度范圍(-40℃到+85℃)內用 2.0V ~ 2.75V 的電壓工作(使用片內穩壓器時電源電壓可達 5.25V) 。 C8051F41x 有 28腳 QFN (也稱為 MLP或MLF)和 32 腳LQFP兩種封裝。

1.1.1 與 8051完全兼容

C8051F41x系列器件使用Silicon Labs的專利CIP-51微控制器核。CIP-51 與MCS-51TM指令集完全兼容,可以使用標準 803x/805x的匯編器和編譯器進行軟件開發。C8051F41x系列器件的外設是標準 8052 的所有外設的超集。

1.1.2 速度提升

CIP-51 采用流水線結構,與標準的 8051 結構相比指令執行速度有很大的提高。在一個標準的 8051 中,除 MUL和 DIV以外所有指令都需要 12 或 24 個系統時鐘周期,最大系統時鐘頻率為 12-24MHz。而對于 CIP-51 核,70%的指令的執行時間為 1 或2 個系統時鐘周期,沒有執行時間大于 8 個系統時鐘周期的指令。

CIP-51 工作在 50MHz 的時鐘頻率時,它的峰值速度達到 50MIPS。CIP-51 共有 111 條指令。下表列出了指令條數與執行時所需的系統時鐘周期數的關系。

1.1.3 增加的功能

C8051F41x SoC 系列 MCU 在 CIP-51 內核和外設方面有幾項關鍵性的改進,提高了整體性能,更易于在最終應用中使用。 擴展的中斷系統允許大量的模擬和數字外設獨立于微控制器工作,只在必要時中斷微控制器。一個中斷驅動的系統需要較少的 MCU干預,因而有更高的執行效率,并使多任務實時系統的實現更加容易。

MCU有9 個復位源:上電復位電路(POR) 、片內 VDD監視器、看門狗定時器、時鐘丟失檢測器、由比較器 0 提供的電壓檢測器、smaRTClock 告警或 smaRTClock 時鐘丟失檢測器復位、軟件強制復位、外部復位引腳復位和 FLASH非法訪問保護電路復位。除了 POR、復位、軟件強制復位、外部復位引腳復位和 FLASH非法訪問保護電路復位。除了 POR、復位輸入引腳及 FLASH操作錯誤這三個復位源之外,其他復位源都可以被軟件禁止。在一次上電復位之后的 MCU初始化期間,WDT 可以被永久性使能。

C8051F41x器件的內部振蕩器在出廠時已經被校準為 24.5MHz ± 2%。器件內還集成了外部振蕩器驅動電路,允許使用外部晶體、陶瓷諧振器、電容、RC或 CMOS 時鐘源產生系統時鐘。使用時鐘乘法器可獲得 50MHz 的時鐘頻率。專用的 smaRTClock 振蕩器在低功耗系統中非常有用,它允許在 MCU 不供電或內部振蕩器被掛起的情況下使系統維持精確的時間。SmaRTClock可用于使 MCU復位或喚醒內部振蕩器。

完整的pdf格式文檔51黑下載地址:

c8051f410中文.pdf

(5.84 MB, 下載次數: 22)

c8051f410中文.pdf

(5.84 MB, 下載次數: 22)

2020-11-20 11:36 上傳

點擊文件名下載附件

|