|

設(shè)計環(huán)境語言 2.1.1 Max+plusII如圖2.1所示,MAX+PLUS II是Altera公司的全集成化可編程邏輯設(shè)計環(huán)境。MAX+plus II 界面友好,使用便捷,被譽(yù)為業(yè)界最易用易學(xué)的EDA軟件。MAX+plus II支持原理圖、VHDL和Verilog語言文本文件,以及波形與EDIF等格式的文件作為設(shè)計輸入,并支持這些文件的任意混合設(shè)計。MAX+plusII具有門級仿真器,可以進(jìn)行功能仿真和時序仿真,能夠產(chǎn)生精確的仿真結(jié)果。在適配之后,MAX+plusII生成供時序仿真用的EDIF、VHDL和Verilog三種不同格式的網(wǎng)表文件。 MAX+plusII支持主流的第三方EDA工具,如Synopsys、Cadence、Synplicity、Mentor、Viewlogic、Exemplar和Model Technology等。MAX+plusII支持除APEX20K系列之外的所有Altera FPGA/CPLD大規(guī)模邏輯器件。 MAX+plusII的HDL文本編輯器是很有彈性的工具,提供多種硬件描述語言的文字編輯與合成的環(huán)境。其中包括有: 1.Altera Hardware Description Language (AHDL) 2.Very High Integrated Circuit Hardware Description Language (VHDL) 3.Verilog Hardware Description Language (Verilig HDL) 以AHDL語法編寫的文件格式為*.tdf,以VHDL語法編寫的文件格式則為*.vhd,而以Verilog HDL語法編寫的文件格式則為*.v。可以設(shè)計程序創(chuàng)建一個符號文件供圖形編輯器使用。

圖2.1

2.1.2 VHDL VHDL 的英文全名是VHSIC Hardware Description Language(VHSIC硬件描述語言)。VHSIC是Very High Speed Integrated Circuit的縮寫,是20世紀(jì)80年代在美國國防部的資助下始創(chuàng)的,并最終導(dǎo)致了VHDL語言的出現(xiàn)。1987年底,VHDL被 IEEE 和美國國防部確認(rèn)為標(biāo)準(zhǔn)硬件描述語言。VHDL主要用于描述數(shù)字系統(tǒng)的結(jié)構(gòu),行為,功能和接口。除了含有許多具有硬件特征的語句外,VHDL的語言形式和描述風(fēng)格與句法是十分類似于一般的計算機(jī)高級語言。VHDL的程序結(jié)構(gòu)特點(diǎn)是將一項工程設(shè)計,或稱設(shè)計實(shí)體(可以是一個元件,一個電路模塊或一個系統(tǒng))分成外部(或稱可視部分,及端口)和內(nèi)部(或稱不可視部分),既涉及實(shí)體的內(nèi)部功能和算法完成部分。在對一個設(shè)計實(shí)體定義了外部界面后,一旦其內(nèi)部開發(fā)完成后,其他的設(shè)計就可以直接調(diào)用這個實(shí)體。這種將設(shè)計實(shí)體分成內(nèi)外部分的概念是VHDL系統(tǒng)設(shè)計的基本點(diǎn)。 描述 在這個語言首次開發(fā)出來時,其目標(biāo)僅是一個使電路文本化的一種標(biāo)準(zhǔn),為了使人們采用文本方式描述的設(shè)計能夠被其他人沒有二意性地所理解。因為用自然語言描述電路會產(chǎn)生二意性。 這個模型是讓人來閱讀的。 模擬的模型 作為模型語言,用于采用模擬軟件進(jìn)行模擬。這個模型是讓仿真軟件來閱讀的。 綜合的模型 在自動設(shè)計系統(tǒng)中,作為設(shè)計輸入。這個模型是讓綜合軟件來閱讀的。 VHDL 語言能夠成為標(biāo)準(zhǔn)化的硬件描述語言并獲得廣泛應(yīng)用,它自身必然具有很多其他硬件描述語言所不具備的優(yōu)點(diǎn)。歸納起來,VHDL語言主要具有以下優(yōu)點(diǎn): (1)VHDL 語言功能強(qiáng)大,設(shè)計方式多樣 (2)VHDL 語言具有強(qiáng)大的硬件描述能力 (3)VHDL 語言具有很強(qiáng)的移植能力 (4)VHDL 語言的設(shè)計描述與器件無關(guān) (5)VHDL 語言程序易于共享和復(fù)用 2.2 設(shè)計要求 1、設(shè)計一個電子定時器,控制洗衣機(jī)作如下運(yùn)轉(zhuǎn):定時啟動?正轉(zhuǎn)?暫停?反轉(zhuǎn)?暫停?定時未到回到“正轉(zhuǎn)?暫停?……”,定時到則停止; 2、用兩個數(shù)碼管顯示洗滌的預(yù)置時間(分鐘數(shù)),按倒計時方式對洗滌過程作計時顯示,直到時間到停機(jī);洗滌過程由“開始”信號開始; 3、三只LED燈表示“正轉(zhuǎn)”、“反轉(zhuǎn)”、“暫停”三個狀態(tài)。 2.3 設(shè)計流程

3 設(shè)計程序

3.1減數(shù)計時模塊由于洗衣機(jī)有工作時間,必須要一模塊來控制它的工作時間范圍,當(dāng)洗衣機(jī)開 始工作后,減法計數(shù)器即會實(shí)現(xiàn)減數(shù)功能,直到時間減到零,洗衣機(jī)便停止工作。 (1)程序 - library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_unsigned.all;

- entity count is

- port(clk,tla,start,enter:in std_logic;

- ini:in std_logic_vector(7 downto 0);

- show:out std_logic_vector(7 downto 0);

- finish:out std_logic);

- end count;

- architecture one of count is

- signal fini:std_logic;

- signal show1:std_logic_vector(7 downto 0);

- begin

- process(tla,clk,start)

- variable num:std_logic_vector(7 downto 0);

- begin

- if enter='1' then num:=ini;

- elsif(tla'event and tla='1')then

- if start='1'and num/=0 then

- num:=num-1;

- end if;

- end if;

- if enter='0'and num=0 then

- fini<='1';num:="00000000";

- else fini<='0';

- show1<=num;

- end if;

- end process;

- process(clk)

- begin

- if clk'event and clk='1'then finish<=fini;

- show<=show1;

- end if;

- end process;

- end;

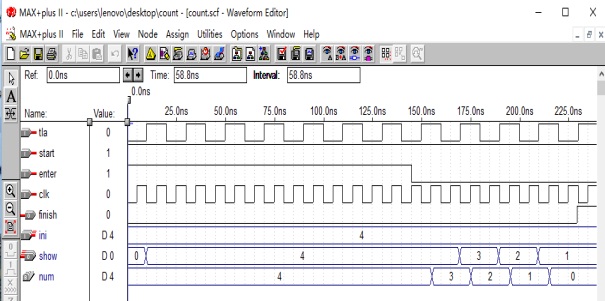

(2)仿真波形 減數(shù)計時模塊仿真如圖3.1所示,start為電源開關(guān),enter反應(yīng)時間設(shè)置情況,當(dāng)洗衣機(jī)開始工作,時由脈沖信號tla進(jìn)行控制完成倒計時,并通過show進(jìn)行顯示。  圖3.1 圖3.1

3.2 預(yù)置時間模塊設(shè)計與仿真 此模塊由一個累加器和一個命令控制器組成,用來實(shí)現(xiàn)預(yù)置時間的功能,洗滌時間數(shù)以分鐘為單位,用戶可以根據(jù)自己的需求來設(shè)置洗滌時間的長短。

通過累加預(yù)置具體洗衣時間。 - library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_unsigned.all;

- entity adder is

- port(in1:in std_logic;

- q:out std_logic_vector(2 downto 0));

- end adder;

- architecture one of adder is

- signal add:std_logic_vector(2 downto 0);

- begin

- q<=add;

- process(in1)

- begin

- if in1'event and in1='1' then

- add<=add+1;

- end if;

- end process;

- end;

累加器模塊仿真波形如圖3.2.1所示,通過累加的方式完成時間設(shè)置。

圖3.2.1

將輸入的三位二進(jìn)制時間信號編碼成十進(jìn)制數(shù)輸出到減法計數(shù)器電路。 - LIBRARY IEEE;

- USE IEEE.STD_LOGIC_1164.ALL;

- USE IEEE.STD_LOGIC_UNSIGNED.ALL;

- ENTITY ORDER IS

- PORT(CLK:IN STD_LOGIC;

- ORDER:IN STD_LOGIC_VECTOR(2 DOWNTO 0);

- TIME:OUT INTEGER RANGE 128 DOWNTO 0);

- END ORDER;

- ARCHITECTURE ONE OF ORDER IS

- BEGIN

- PROCESS(CLK)

- BEGIN

- CASE ORDER IS

- WHEN "000" =>TIME<=1;

- WHEN "001" =>TIME<=2;

- WHEN "010" =>TIME<=3;

- WHEN "011" =>TIME<=4;

- WHEN "100" =>TIME<=5;

- WHEN "101" =>TIME<=6;

- WHEN "110" =>TIME<=7;

- WHEN "111" =>TIME<=8;

- WHEN OTHERS =>TIME<=0;

- END CASE;

- END PROCESS;

- END;

命令控制器模塊仿真波形如圖3.2.2所示,將輸入的二進(jìn)制信號轉(zhuǎn)化為十進(jìn)制信號。  圖3.2.2 圖3.2.2

3.3數(shù)碼管顯示模塊: 根據(jù)設(shè)計要求,必須將洗衣機(jī)的工作狀態(tài)及工作時間在數(shù)碼管和指示燈上顯示出來,此模塊是用來控制洗衣機(jī)的工作狀態(tài)及工作的頻率,并把工作狀態(tài)及工作時間顯示出來。a,b,c,d,e,f,g分別對應(yīng)數(shù)碼管的七段,minute和second分別位選兩個數(shù)碼管,顯示十位和個位。- LIBRARY IEEE;

- USE IEEE.STD_LOGIC_1164.ALL;

- USE IEEE.STD_LOGIC_UNSIGNED.ALL;

- ENTITY SHOWTIME IS

- PORT (TIME_REMAIN:IN STD_LOGIC_VECTOR (7 DOWNTO 0);

- CLK:IN STD_LOGIC;

- MINUTE,SECOND:OUT STD_LOGIC;

- A,B,C,D,E,F,G:OUT STD_LOGIC);

- END SHOWTIME;

- ARCHITECTURE ONE OF SHOWTIME IS

- SIGNAL TEMP:STD_LOGIC_VECTOR(6 DOWNTO 0);

- SIGNAL BCD:STD_LOGIC_VECTOR(3 DOWNTO 0);

- SIGNAL CHOOSE:STD_LOGIC;

- BEGIN

- PROCESS (CLK)

- BEGIN

- IF(CLK'EVENT AND CLK='1')THEN

- CHOOSE<=NOT CHOOSE;

- IF(CHOOSE='1')THEN

- MINUTE<='0';SECOND<='1';

- BCD<=TIME_REMAIN(7 DOWNTO 4);

- ELSE

- MINUTE<='1';SECOND<='0';

- BCD<=TIME_REMAIN(3 DOWNTO 0);

- END IF;

- END IF;

- END PROCESS;

- PROCESS(BCD)

- BEGIN

- CASE BCD IS

- WHEN "0000" =>TEMP<="1111110";--0

- WHEN "0001" =>TEMP<="0110000";--1

- WHEN "0010" =>TEMP<="1101101";--2

- WHEN "0011" =>TEMP<="1111001";--3

- WHEN "0100" =>TEMP<="0110011";--4

- WHEN "0101" =>TEMP<="1011011";--5

- WHEN "0110" =>TEMP<="1011111";--6

- WHEN "0111" =>TEMP<="0001111";--7

- WHEN "1000" =>TEMP<="1111111";--8

- WHEN "1001" =>TEMP<="1111011";--9

- WHEN others =>TEMP<="0000000";

- END CASE;

- A<=TEMP(6);B<=TEMP(5);C<=TEMP(4);D<=TEMP(3);E<=TEMP(2);F<=TEMP(1);G<=TEMP(0);

- END PROCESS;

- END;

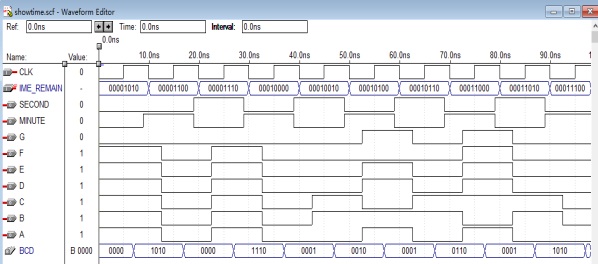

數(shù)碼顯示模塊如圖3.3所示,通過數(shù)碼管MINUTE和SECOND顯示十位和個位的數(shù)。

圖3.3

3.4狀態(tài)機(jī)模塊: 接收電機(jī)運(yùn)行狀態(tài)信號,譯碼后實(shí)時控制電機(jī)的正傳、反轉(zhuǎn)和暫停。 - library ieee;

- use ieee.std_logic_1164.all;

- entity move is

- port(out_1,out_2:in std_logic;

- REV,RUN,PAUSE:buffer std_logic);

- end move;

- architecture move of move is

- signal choose:std_logic_vector(1 downto 0);

- begin

- choose(1)<=out_1;

- choose(0)<=out_2;

- process(choose)

- begin

- case choose is

- when "00"=>REV<='0';RUN<='0';PAUSE<='1';

- when "10"=>REV<='0';RUN<='1';PAUSE<='0';

- when "01"=>REV<='1';RUN<='0';PAUSE<='0';

- when others=>REV<='0';RUN<='0';PAUSE<='0';

- end case;

- REV<=out_2;RUN<=out_1;PAUSE<=not(out_1 or out_2);

- end process;

- end move;

狀態(tài)機(jī)模塊如圖3.4所示,接受電機(jī)狀態(tài)信號,完成電機(jī)正轉(zhuǎn)RUN、反轉(zhuǎn)REV和暫停PAUSE的控制

圖3.4 采用的是模塊化層次化的設(shè)計方法,通過這樣分模塊化的思考方式,設(shè)計顯得相對容易了很多,思路也相對簡單了很多。洗衣機(jī)控制器主要有三個狀態(tài),要實(shí)現(xiàn)幾種狀態(tài)的多次循環(huán)改變,預(yù)置時間,還有計時和數(shù)碼管動態(tài)顯示的功能。因此電路可主要分為以下幾個模塊:預(yù)置時間和減法計數(shù)器模塊、數(shù)碼管動態(tài)顯示模塊、狀態(tài)控制模塊。通過每個模塊的設(shè)計,最后運(yùn)用VHDL語言的進(jìn)程語句進(jìn)行模塊間的組合,從而完成程序的設(shè)計。

通過這次設(shè)計,我對VHDL語言有了基本的掌握,對其設(shè)計方法也有了一些技巧性的了解,為將來的硬件設(shè)計打下了一定的基礎(chǔ)。對于FPGA編程、定時器和計數(shù)器的設(shè)計都熟悉起來了,加深了對時序組合電路印象。同時學(xué)會了自頂向下的數(shù)字系統(tǒng)設(shè)計思路,在設(shè)計一個系統(tǒng)時,首先要對一個系統(tǒng)的功能做充分的了解,然后模塊劃分也應(yīng)該進(jìn)行合理的安排,模塊與模塊之間又應(yīng)該如何連接,同時應(yīng)該適當(dāng)考慮電路實(shí)驗問題。

通過洗衣機(jī)設(shè)計,還可以使我們對于FPGA的工作原理,有了較之前更清楚明白的理解。FPGA可以應(yīng)用到許多方面,通過搭載不同的內(nèi)核,可以應(yīng)用到不同系統(tǒng)中,完成多種任務(wù)設(shè)計。由此可見,對于相關(guān)專業(yè)的學(xué)習(xí)與工作來說,學(xué)好FPGA,學(xué)會運(yùn)用它豐富的功能,是十分有必要的。在學(xué)習(xí)一門技術(shù)之前我們往往從它的編程語言開始,如同學(xué)習(xí)單片機(jī)一樣,我們從c語言開始入門,當(dāng)掌握了c語言之后,開發(fā)單片機(jī)應(yīng)用程序也就不是什么難事了。學(xué)習(xí)fpga也是如此,fpga的編程語言有兩種:vhdl和verilog,這兩種語言都適合用于fpga的編程。

總的來講,在對FPGA的設(shè)計中,讓我對于可編程邏輯器件的相關(guān)理論有了更深刻的理解與掌握,且鍛煉了自己熟悉新軟件能力,并且對VHDL語言有了一定的了解,對程序的設(shè)計有了直觀的體驗,從而得到許多收獲。

以上的Word格式文檔51黑下載地址:

洗衣機(jī)控制器.doc

(199.28 KB, 下載次數(shù): 30)

洗衣機(jī)控制器.doc

(199.28 KB, 下載次數(shù): 30)

2020-11-30 08:50 上傳

點(diǎn)擊文件名下載附件

FPGA

|