含時鐘使能的十進制計數器的設計,Quartus II 9.0 軟件開發,學習使用Quartus II 9.0軟件,掌握VHDL文本描述和原理圖描述的RTL級描述方法,掌握計數器的描述方法。基于74390的十進制計數器的設計,含時鐘使能的2位十進制計數器的設計和含時鐘使能的60進制計數器的設計。

1、掌握利用Quartus II 9.0 軟件開發數字電路的基本流程以及掌握Quartus II軟件的詳細操作。 2、掌握使用VHDL原理圖設計進行集成電路系統設計的實現方法。

二 實驗前的準備 1、打開計算機電源,運行Quartus II軟件。 2、工程文件需要保存在D盤工作文件夾中,本設計需要保存3個工程,請為其設定3個獨立的文件夾。本次實驗工作文件夾為exp3,在exp3下再建3個文件夾CNT10、CNTD10、CNT60,分別將十進制計數器、雙十進制計數器、30進制計數器的工程保存在對應文件夾中。

三 實驗要求 學習使用Quartus II 9.0軟件,掌握VHDL文本描述和原理圖描述的RTL級描述方法,掌握計數器的描述方法。

四 實驗內容 (一)基于74390的十進制計數器的設計 1、十進制計數器的設計原理,采用74390作為十進制計數器,注意74390的工作原理。

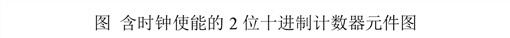

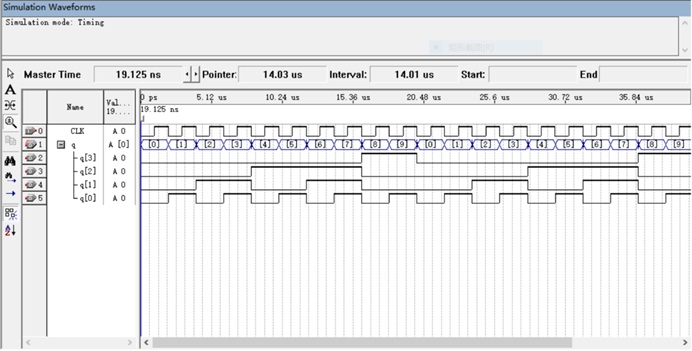

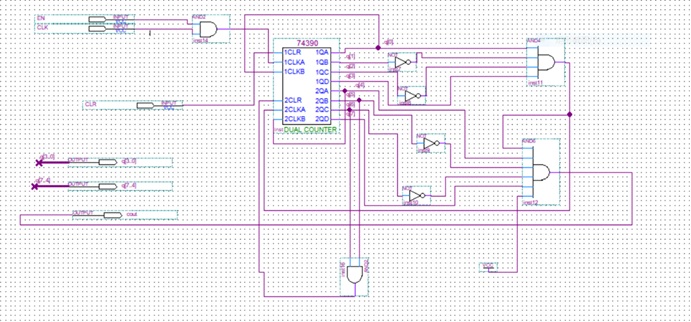

注意:圖中粗線q[3..0]代表總線,細線q[0]-q[3]代表總線中的單根線。右鍵點擊粗/細線,選擇Properties,可為連接線命名。在圖上看,q[0]-q[3]與q[3..0]是斷開的,經綜合后,此兩部分會被EDA工具自動連上。因此,相同名稱的線會在綜合時自動連接上。 2、建立工程CNT10,建立原理圖文件CNT10,添加74390元件,完成十進制計數器的設計方案。對十進制計數器的設計方案進行時序仿真,將仿真波形寫入實驗報告。 (二)含時鐘使能的2位十進制計數器的設計 1、含時鐘使能的2位十進制計數器的設計原理圖

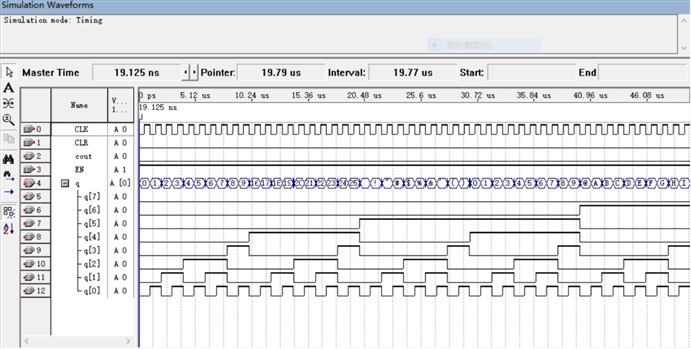

2、建立工程CNTD10,建立原理圖文件CNTD10,完成含時鐘使能的2位十進制計數器的設計方案。并對該方案進行時序仿真,將仿真波形寫入實驗報告。 (三)含時鐘使能的60進制計數器的設計 1、參考含時鐘使能的2位十進制計數器的設計原理圖,對原理圖進行修改,完成60進制計數器的設計方案。 2、建立工程CNT60,建立原理圖文件CNT60,完成60進制計數器的設計方案,并進行時序仿真,將仿真波形寫入實驗報告。 思考:60進制如何實現?當滿足進位條件時,計數清理如何實現? 五 實驗截圖過程 十進制計數器原理圖

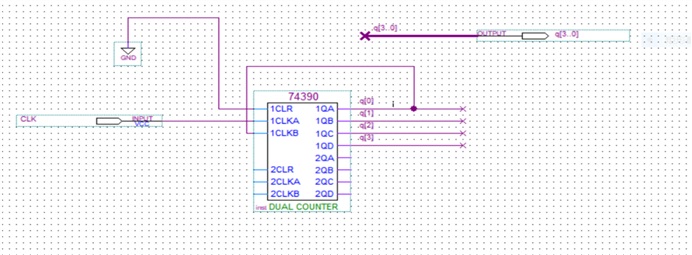

十進制計數器時序仿真波形圖

含時鐘使能的2位十進制計數器

含時鐘使能的2位十進制計數器時序仿真波形圖

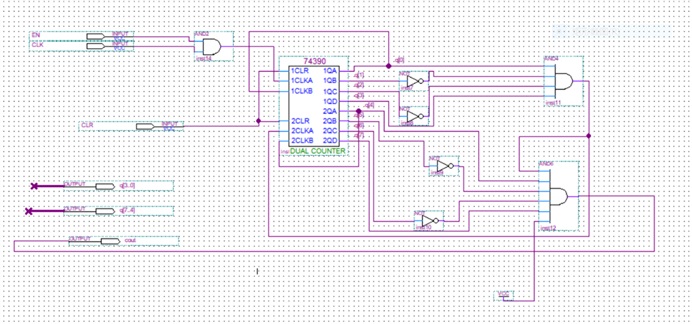

含時鐘使能的60進制計數器原理圖

含時鐘使能的60進制計數器時序仿真波形圖

資料:

EXP3.zip

(1001.04 KB, 下載次數: 10)

EXP3.zip

(1001.04 KB, 下載次數: 10)

2021-2-24 18:24 上傳

點擊文件名下載附件

實驗 含時鐘使能的十進制計數器的設計.docx

(470.32 KB, 下載次數: 5)

實驗 含時鐘使能的十進制計數器的設計.docx

(470.32 KB, 下載次數: 5)

2021-2-24 18:24 上傳

點擊文件名下載附件

|