目錄

HLS案例開發2_led_flash案例|基于FPGAKintex-7開發板 前 言 案例功能 HLS工程說明 編譯與仿真 IP核測試 更多推薦

前 言

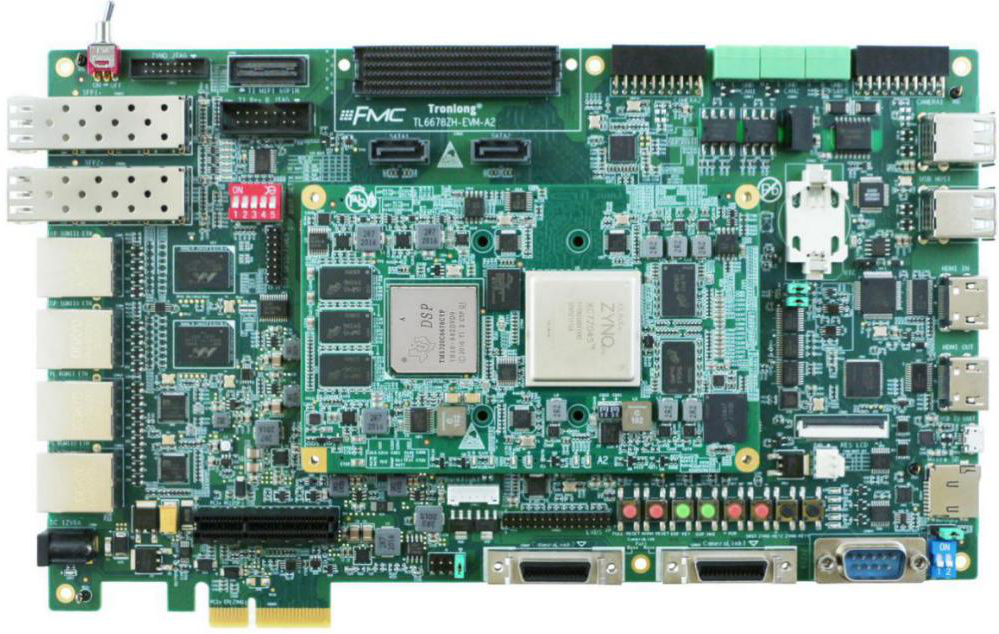

本文led_flash案例是基于創龍科技TLK7-EVM開發板,是一款基于Xilinx Kintex-7系列FPGA設計的高端評估板,由核心板和評估底板組成。核心板經過專業的PCB Layout和高低溫測試驗證,穩定可靠,可滿足各種工業應用環境。

評估板接口資源豐富,引出FMC、SFP+、PCIe、SATA、HDMI等接口,方便用戶快速進行產品方案評估與技術預研。

TLK7-EVM評估板

開發案例主要包括:

1.CameraLink、SDI、HDMI、PAL視頻輸入/輸出案例

2.高速AD(AD9613)采集+高速DA(AD9706)輸出案例

3.AD9361軟件無線電案例

4.UDP(10G)光口通信案例

5.UDP(1G)光口通信案例

6.Aurora光口通信案例

7.PCIe通信案例

8.案例源碼、產品資:site.tronlong.com/pfdownload

案例功能

控制評估底板LED2每隔0.5s將狀態翻轉一次。

HLS工程說明

時鐘

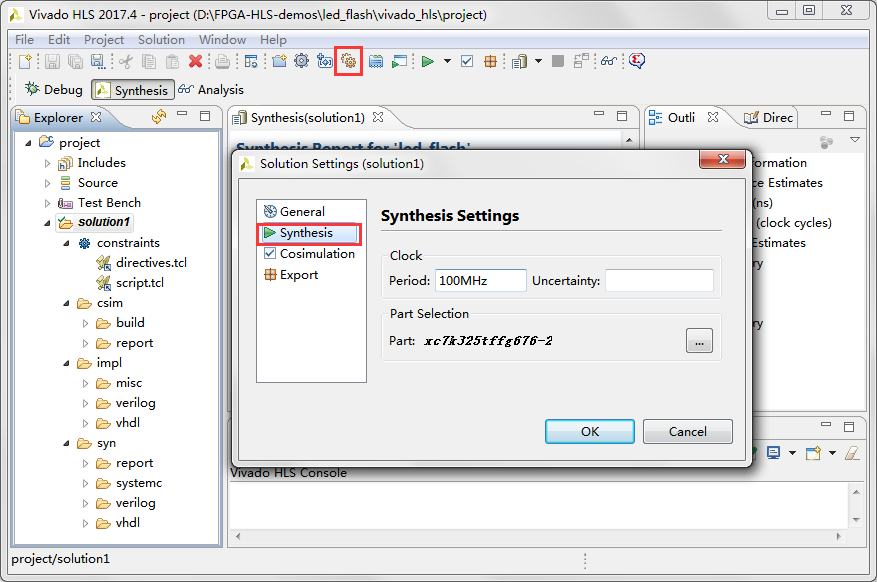

HLS工程配置的時鐘為100MHz,案例將該時鐘用于計算0.5s間隔時間進行LED2亮滅狀態控制,生成的IP核亦需接入該時鐘。如需修改時鐘頻率,請打開HLS工程后點擊,在彈出的界面中的Synthesis欄目進行修改。

頂層函數

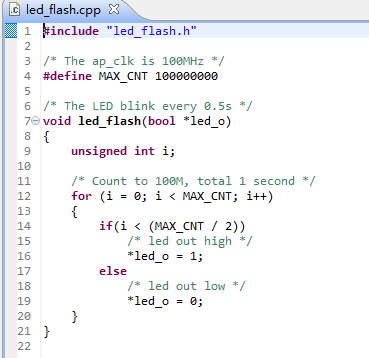

案例頂層函數為led_flash.cpp中的led_flash()。

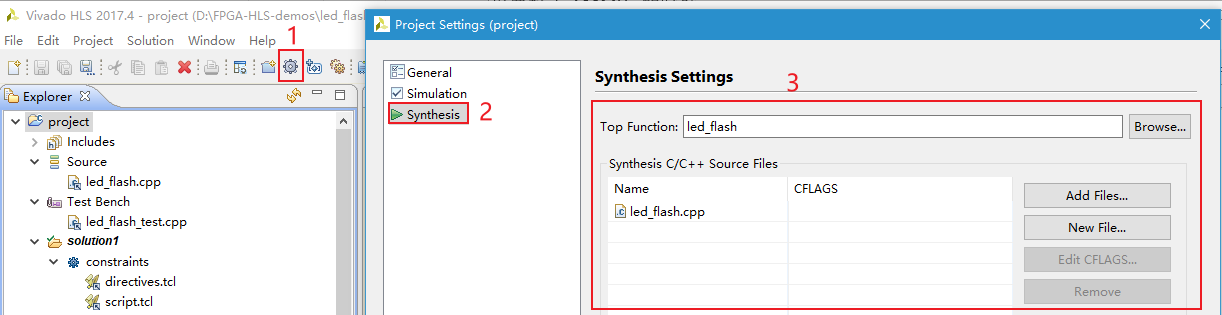

點擊后,可在彈出的界面中的Synthesis欄目查看或設置頂層函數。

該函數控制評估底板LED2每隔0.5s將狀態翻轉一次。工程設置的時鐘為100MHz(周期10ns),在for循環里計數值為100000000,用時為10ns x 100000000 = 1s。

編譯與仿真

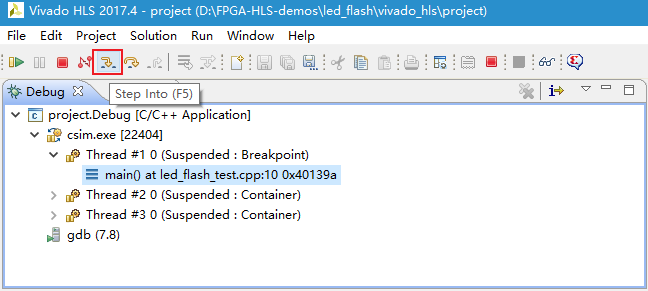

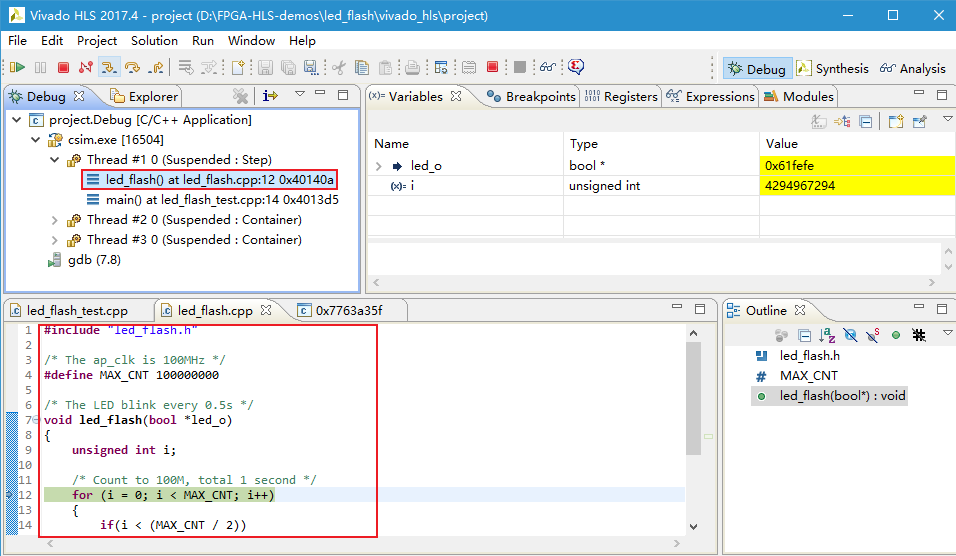

請參考本文檔HLS開發流程說明章節,進行編譯。編譯完成后,進入仿真界面點擊進行單步運行,進入led_flash()函數。

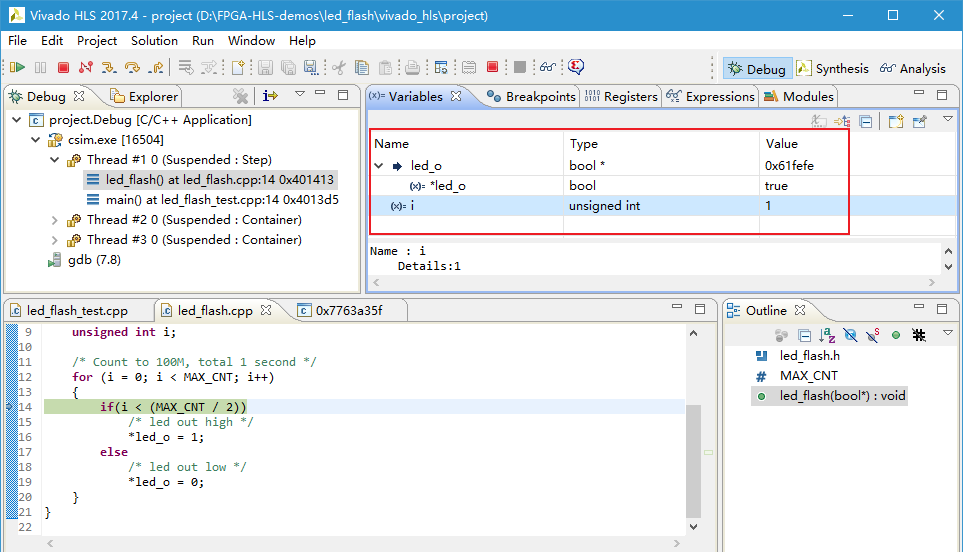

繼續點擊進入for循環,當i < 50000000時,*led_o等于1(true)。

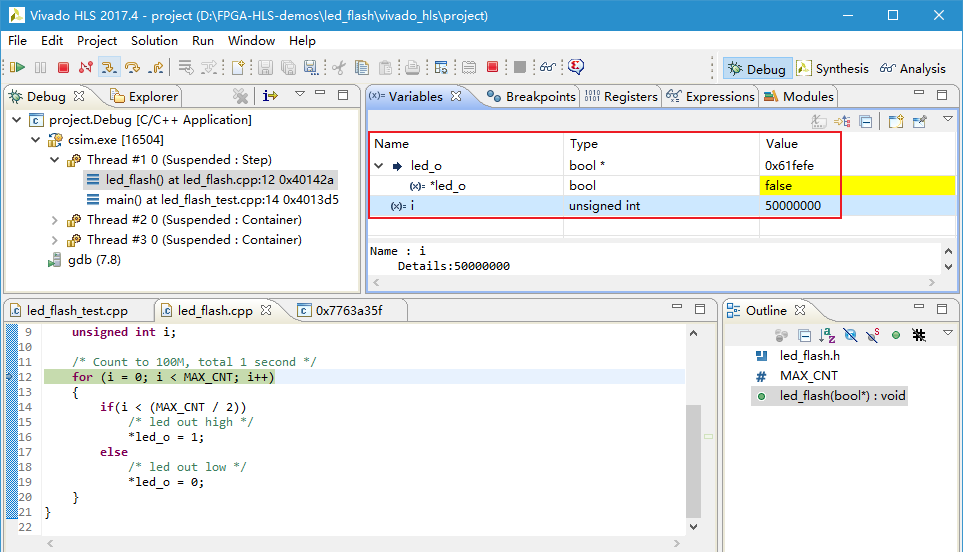

點擊全速運行或修改i的值為50000000,當i ≥ 50000000時,*led_o等于0(false)。

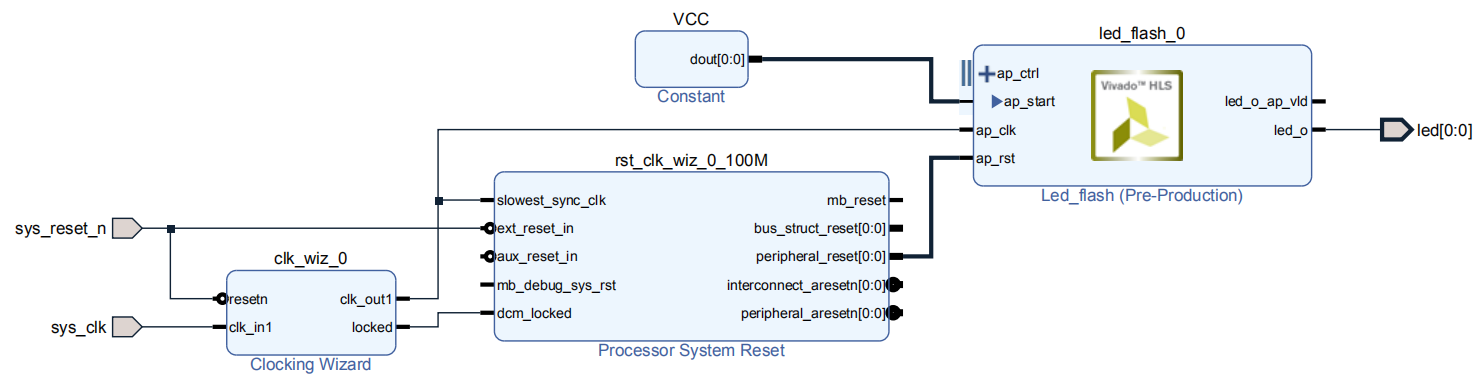

IP核測試請參考本文檔HLS開發流程說明章節,完成IP核測試前的準備工作。

HLS工程生成的IP核為led_flash_0。

加載.bit格式可執行文件到評估板,即可看到評估底板的LED2進行閃爍。

更多推薦

TL6678ZH-EVM評估板(C6678 + ZYNQ,地表至強,多核DSP +多核ARM +FPGA!)

基于TI KeyStone架構C6000系列TMS320C6678八核C66x定點/浮點DSP,以及Xilinx Zynq-7000系列XC7Z045/XC7Z100 SoC處理器設計的高端異構多核評估板。

TMS320C6678每核心主頻可高達1.25GHz,XC7Z045/XC7Z100集成PS端雙核ARM Cortex-A9 + PL端Kintex-7架構28nm可編程邏輯資源。

引出雙路CameraLink、雙路SFP+光口、四路千兆網口、雙路SATA、雙路PCIe、四路USB、雙路CAN、雙路CAMERA、HDMI IN/OUT、LVDS、LCD、RS485、RS232、Micro SD、HPC FMC等接口。

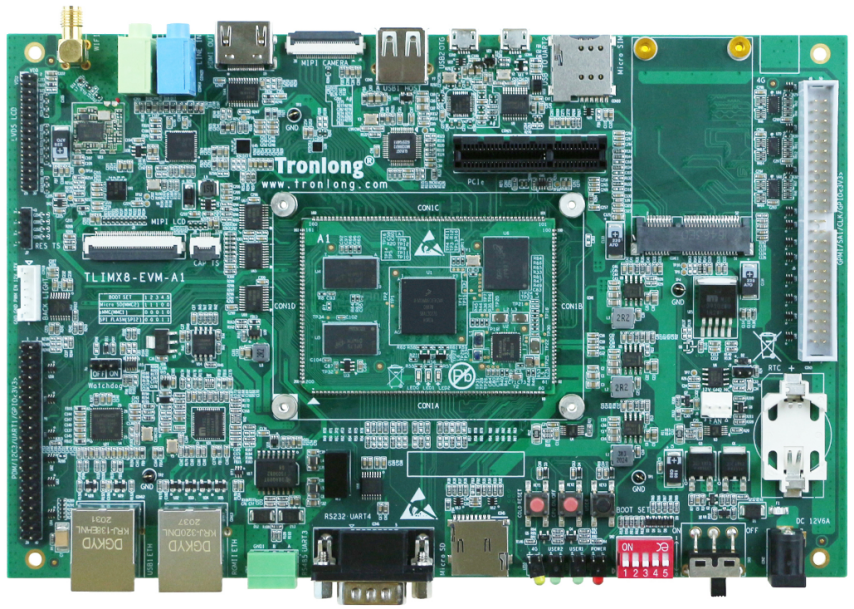

TLIMX8-EVM評估板(i.MX 8,,4核ARM Cortex-A53!)

基于NXP i.MX 8M Mini的4核ARM Cortex-A53 + 單核ARM Cortex-M4多核處理器設計的高性能評估板,每核主頻高達1.6GHz。

引出MIPI CAMERA、MIPI/LVDS LCD、HDMI OUT、LINE IN/OUT、PCIe、FlexSPI、USB、RS485、RS232、千兆網口、百兆網口等接口

|