|

ժ Ҫ����Ƭ�C����ϵ�y�ڰl�әC늇��еõ��ˏV���đ���,Ȼ�����ڰl�әC�����h�����ӣ���߿���ϵ�y�Ŀ��ɔ_�����P��Ҫ�������ˆ�Ƭ�C�ɔ_����Ҫ��Դ������Ӳ����ܛ�����ɔ_�OӋ�п��Y��һЩȡ�����ÿ��ɔ_�Եķ�����

���M�І�Ƭ�C�����_�l���^���У����������ڌ�����{���ܺõĆ�Ƭ�Cһ�������F���͕����F�@�ӻ��ǘӵĆ��}���@��Ҫ�������OӋδ��ֿ��]�����h�����ڵĸɔ_����Cе���ӡ����N늴Ų��ͭh���ز��Ӱ�Ӳ��ϵ�y�����ܣ�����늿؆�Ԫ���������������b�ڴ˱����^ȫ������˸ɔ_��Ƭ�C����ϵ�y�����ز��Y���Լ����о��n�}�����һЩ������ϵ�y���ɔ_�Եķ����� 1��Ƭ�Cϵ�y����Ҫ�ɔ_Դ

ϵ�y�ĸɔ_Դ�����ϵ�y�ĸɔ_��Ҫ��늴������ɔ_����Ҫ����ĸɔ_Դ�ǣ�

��1���o����Oʩ�����l�ɔ_��

��2���l�әC�ϵĸ߉��c��Ȧ����ݗ��ň����ȴ��l������늴Ų�;

��3����Ƭ�C�Ȳ��ľ����·�ǃȲ��ɔ_Դ֮һ��

��4�������·�����T�·�l���Č�ͨ����ֹ����Դ�ؾ����׃����Ҳ���a���ܴ�ĸ��l늴Ÿɔ_�����N�_�P����O��ͨ���r�a���ļ���׃����������a���^���l�V�ɔ_��

��5����罻���·�Юa���Ĺ��l�ɔ_����Ӱ�ģ�M�·ݔ����̖�Ĝʴ_�ԡ�

2�ɔ_����Ϸ�ʽ

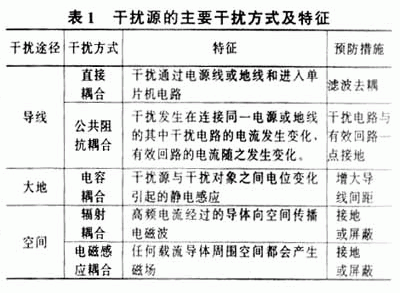

�ɔ_Դ�a���ĸɔ_��ͨ�^����ŵ����C�y��ϵ�y�a���ɔ_���ã������Ҫ���x�ɔ_Դ�c����ϵ�y֮�g������ŵ�����1�г��˸ɔ_Դ����Ҫ�ɔ_��ʽ��������

3��Ƭ�C��Ӳ�����ɔ_�OӋ ��Ӳ�����ɔ_���g��ϵ�y�OӋ���x�Ŀ��ɔ_��ʩ��������Ч�����Ƹɔ_Դ�����ɔ_�Ă�ݔ�ŵ������õĴ�ʩ�У��V�����g��ȥ��g�����μ��g�ͽӵؼ��g��

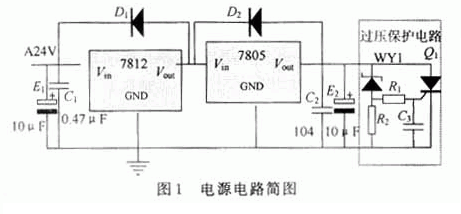

3.1�Դ�·���OӋ ���ڱ�늿�ϵ�y�У�ģ�M�·�Դ�c߉�·�Դ���x��һ�Ǟ���ȥ��ͨ�^�Դ���߉�·�a���ĸɔ_�M��ģ�M�·�����Ǟ��˱��������ͨ�^�Դ��ό�ECU�ɔ_��������ģ�K���ϵ�y��D1��ʾ���Բ���7812��7805���˷�������оƬ���Ҷ��Ϊ����Դ�M��ؓ����o���@�Ӳ���������ijһ�����Դ���F���϶�Ӱ�����ϵ�y�·��ʹ�õ�ͨ�V������ɜp���Ըߴ��C�������ĸɔ_Դ���Ķ������Դ����;��ݔ���˲������^�����o�·��ͨ�^�����OӋ�ɘO����߹�늵Ŀɿ��ԡ��D��D1��D2����ؓ����o����ֹ���������������be�Yʹ��������ʧЧ��������WY1�����l��Q1�����^�����o�����E1��E2��C1��C2ʹݔ��늉����y������һ�������ȡ���

3.2ģ�M�·���ɔ_�OӋ

��Ӳ���·���OӋ�У�ģ�M�·�OӋ�dz���Ҫ���l�әC�Ĺ����h���ض�׃�����^�������ģ�M�·�Б��x��͜�Ưϵ���ļ��ɷŴ�������ģ�M�·����,��ģ��̖���·��Ӱ��^����ģ�M�·�в��ò�ӷŴ��·���ɵó��ɶ�ݔ����̖�����Օr�����p����̖�D����ζ���̖���ɷdz���Ч�����ƹ�ģ��̖�����·��ݔ����̖׃�����^�����ڷŴ�������^��ǰ��ݔ��˱��o�·�Ա��������ēp�ġ���罻���·�a���Ĺ��l�ɔ_��ģ�M��̖���^���Ӱ푣����·�в�����Դ�V�����͵�ͨ�V������

3.3�x�Õr��l�ʵ͵Ć�Ƭ�C

��r��Ǹ��l��Դ��������������Ӳ���·�a���ɔ_�⣬߀�܌����a���ɔ_������x�õ��l�ʵĆ�Ƭ�C����߿��ɔ_�Ե�ԭ�t֮һ����ͬ��1 ��s�r��8051��Ƭ�C��r犞�12 MHz��Atmel��˾��Ƭ�C��r犞�6 MHz����Microchip��Motorola�Ć�Ƭ�C�r��l�ʞ�4 MHz��

3.4ݔ�롢ݔ�����x

ݔ�롢ݔ����̖ͨ�^���x�����Д�ɔ_�ŵ������⏊�������·�ě_�������õĸ��x�����й�늸��x���^������x��׃�������x��׃�������x�ǂ��f�}�_ݔ�롢ݔ����̖�r�����܂��fֱ����������˳����ڲ�Ҫ����fֱ��������ݔ��ݔ�������O���С������������ڽY�����Σ����^�V������ݔ�롢ݔ�����x�ŵ�֮�С�

3.5����g

���δ�ʩ���Է�ֹ����O������ݗ��ɔ_늴Ų���Ҳ��������늴Ÿɔ_Դ������O��ĸɔ_��������Դ�^����_�P�Դ���ɲ����p�����Σ����_�P�Դ�Ȳ��Ѹ��l׃�����Ͷ���Ȧ�M�����Σ�Ȼ�������_�P�Դ�M�����α��o��3.6ȥ���· ��������̖�ƽ�D�Q���D�Q�^���Е��a���ܴ�ě_����������ڂ�ݔ�������Դ�����Ϯa���^�����γɇ��ظɔ_�������ƴ˸ɔ_�����Դ�·�������·����̖̎���·���m������ȥ����ݣ����γ�ȥ���·���@�ӿ���·�����·�a���ĸɔ_��ȥ�����Ӌ��ɰ����·���Ӌ�㣺

C�ݦ�i/(��v/��t)

���Ц�i����v�������늉���׃��������t��׃���ĕr�g��

3.7ӡˢ�·����OӋ

3.7.1�M���IJ���

���·����Ԫ���������ܼ��в��ã�������ģ�K�ĽM�����_�����Ҳ�ͬģ�K�քe�c�������Դ���ؾ����B�������һ�c�ӵء�

��1����Ƭ�C������Uչ�·������һ���Կs������֮�g�Y�Ϻ͵�ַ�����L�ȣ��@���ܫ@���^�ÿ��ɔ_Ч����

��2������߉�·�r��ԭ�t�ϑ��ڳ������ӷ��ø������������h̎���õ��������̓ȴ棬�@�Ӳ��ÿɽ������迹��Ϻ�ݗ����ϡ�

��3��������ݑ���������IC�M����

��4�����˽����ⲿ��·���M�ĸɔ_���������������x׃�����͞V����ͨ�����ڿ����������ӵĵط���

3.7.2�·�岼��

��1���Դ�����ؾ��M���ܴ�һ�c������������c��̖����һ�¡�

��2�������·���M��������Ƭ�C��ʯӢ���w��ʎ���⚤�ӵأ��r���ʎ�·�������

���·�õؾ�Ȧ������

��3���·���~ģ���M��ʹ��45���۾�������90���۾���

��4������������̖���ľ��g�ɔ_�͜p����̖�ڂ�ݔ�����ϵ����t��

��5��ģ�M��̖���_���l���������������Ҫ��ģ�M��̖�����õؾ��������k���Ԝp��늴���ϡ�

3 8�x���������õĽM��

�y��ϵ�y��̎�ĭh�������Ї��صĸɔ_������x�����ܺܺõĮaƷ���e�dž�Ƭ�C����RAM�ȣ�����x��һ��Ʒ���@�ӿ����ϵ�y�Ŀ��ɔ_�ԣ���������������x��CMOS�������������ƹ�ģ�ɔ_���x�Üy���Ŵ�����3.9���ݔ����̖늉������ �����ݔ��ݔ���B�Ӿ�·�^�L�������߂���늉���������Ԝp����̖��˥�p��ɔ_�������̖ʧ�档�^���εķ������ڂ��Ͷ˼�һ��1488�����ն˼�һ��1489��

4��Ƭ�Cܛ���Ŀ��ɔ_�OӋ

�M�ܲ�ȡ��Ӳ�����ɔ_��ʩ�������ڸɔ_��̖�a����ԭ����s�����кܴ���S�C�ԣ�����ڲ�ȡӲ�����ɔ_��ʩ�Ļ��A�ϣ���ȡܛ�����ɔ_��ʩ�����a�䡣��Ҋ��ܛ�����ɔ_���g�У����֞V����ָ������͡����T�������g��ϵ�y�\�Р�B�Oҕ������_�P��ݔ�롢ݔ���ɔ_��

ϵ�y��Ҋ�ij��e�F�����C�����،����`�����Ͷ��r���ʣ�������Ҫ���ڃȲ�����ָ��e�yʹ�����M�롰��ѭ�h����RAM�Y�ϱ��_�y���׃���µġ�

4.1���֞V��

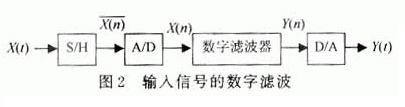

���ɔ_�B��ݔ���ŵ���ģ�M��̖�r��ʹ�����ɼ��`��Ӵ��e��ݔ���ŵ�ģ�M��̖�^���r���ˬF����Ӈ��ء��������������ɼ����`��������gƽ���������^ȡ�ᷨ��һ�A����V��������ֵ�����ɸ�����̖�ɔ_��Ҏ�ɣ���������OӋ������ݔ��ģ�M��̖̎����D2��ʾ��ͨ�^���֞V�����ɞV��������ݔ����̖�ɔ_�������ݔ�������e�`��

4.2ָ������͡����T�������g

��Ƭ�C���ɔ_����ɳ���Ӌ����PCֵ��׃���Ɖij��������\�С�ᘌ��@һ���}�����P�I�ط�����һЩ���ֹ�ָ��NOP����Ч�Ć��ֹ�ָ�������ָ��LJMP MAIN �����@�ġ��y�w�����������λ��ڵ�ַ���Ķ�������y�w����������һЩ���y�w�������������ѭ�h��ͨ������ܛ��Ӳ�������T�������g�������T�������g���Dz���Oҕ�����\�Еr�g���������\�г��F���ϕr��Ӌ���������ϵ�y��λ�������\��ϵ�y����

4.3���RAM�Y�Ͽɿ���

�Դ�_���͔�늼�CPU�ܵ��ɔ_�п����Ɖ�RAM�е��Y�ϡ�ֻ�в����Y�����༼�g���oRAM�е��Y�ϡ�ϵ�y��λ�����������õ�RAM����Ҫ�����M�����ҙz�ͻ֏ͣ��Ķ����oRAM�е��Y�ϡ�

4.4����_�P��ݔ�롢ݔ�����ɔ_

��������Ч��̖�ϯB��һϵ���xɢ���}�_���@�N�ɔ_������Ӳ���������ƣ��ɲ���ܛ���؏͙z�y�����ݔ�롢ݔ���ӿڿ��ɔ_�ԡ�

5���Y

��ͬ�Ć�Ƭ�Cϵ�y�����Լ���ϵ�yҪ������c����Ӳ����ܛ�����ɔ_�OӋ��Ҳ�����Լ�����ɫ��ᘌ��o������l�ɔ_�ͽ����·���l�ɔ_��5�N��Ҫ�ĸɔ_Դ�Լ��ɔ_�ķ�ʽ���ɲ���������Ӳ�����ɔ_��ʩ������ܛ�����ɔ_��ʩ���������˽�y������ɔ_���أ������ɔ_�ā�Դ��Ȼ�����ϵ�y�OӋ��Ч�Ŀ��ɔ_������ |

����TQQ:125739409;���g����QQȺ281945664

����TQQ:125739409;���g����QQȺ281945664