|

|

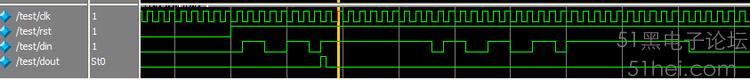

經(jīng)常在筆試的時候出現(xiàn)這樣的題:檢測序列為11001101,輸出為1,否則輸出為0。抽空寫了下代碼,僅供參考。

FSM1:一段式

module machine_test1(clk,rst,din,dout);

input clk,rst;

input din;

output dout;

//11001101

parameter idle=0,

st0=1,

st1=2,

st2=3,

st3=4,

st4=5,

st5=6,

st6=7;

reg [3:0] next_state;

reg dout;

always @ (posedge clk or negedge rst)

begin

if(!rst)

begin

next_state=idle;

dout=0;

end

else

begin

case(next_state)

idle:

if(din)

begin

next_state=st0;

dout=0;

end

else

begin

next_state=idle;

dout=0;

end

st0:

if(din)

begin

next_state=st1;

dout=0;

end

else

begin

next_state=idle;

dout=0;

end

st1:

if(!din)

begin

next_state=st2;

dout=0;

end

else

begin

next_state=st1;

dout=0;

end

st2:

if(!din)

begin

next_state=st3;

dout=0;

end

else

begin

next_state=st0;

dout=0;

end

st3:

if(din)

begin

next_state=st4;

dout=0;

end

else

begin

next_state=idle;

dout=0;

end

st4:

if(din)

begin

next_state=st5;

dout=0;

end

else

begin

next_state=idle;

dout=0;

end

st5:

if(!din)

begin

next_state=st6;

dout=0;

end

else

begin

next_state=st1;

dout=0;

end

st6:

if(din)

begin

next_state=idle;

dout=1;

end

else

begin

next_state=idle;

dout=0;

end

default:

begin

next_state=idle;

dout=0;

end

endcase

end

end

endmodule

FSM2:兩段式

module machine_test(clk,rst,din,dout);

input clk,rst;

input din;

output dout;

//11001101

parameter idle=0,

st0=1,

st1=2,

st2=3,

st3=4,

st4=5,

st5=6,

st6=7;

reg [3:0] current_state,next_state;

reg dout;

always @ (posedge clk or negedge rst)

begin

if(!rst)

current_state<=idle;

else

current_state<=next_state;

end

always @ (next_state or current_state or din or dout)

begin

case(current_state)

idle:

if(din)

begin

next_state=st0;

dout=0;

end

else

begin

next_state=idle;

dout=0;

end

st0:

if(din)

begin

next_state=st1;

dout=0;

end

else

begin

next_state=idle;

dout=0;

end

st1:

if(!din)

begin

next_state=st2;

dout=0;

end

else

begin

next_state=st1;

dout=0;

end

st2:

if(!din)

begin

next_state=st3;

dout=0;

end

else

begin

next_state=st0;

dout=0;

end

st3:

if(din)

begin

next_state=st4;

dout=0;

end

else

begin

next_state=idle;

dout=0;

end

st4:

if(din)

begin

next_state=st5;

dout=0;

end

else

begin

next_state=idle;

dout=0;

end

st5:

if(!din)

begin

next_state=st6;

dout=0;

end

else

begin

next_state=st1;

dout=0;

end

st6:

if(din)

begin

next_state=idle;

dout=1;

end

else

begin

next_state=idle;

dout=0;

end

default:

begin

next_state=idle;

dout=0;

end

endcase

end

endmodule

FSM3:三段式

module machine_test2(clk,rst,din,dout);

input clk,rst;

input din;

output dout;

//11001101

parameter idle=0,

st0=1,

st1=2,

st2=3,

st3=4,

st4=5,

st5=6,

st6=7,

st7=8;

reg [3:0] current_state,next_state;

reg dout;

always @ (posedge clk or negedge rst)

begin

if(!rst)

current_state<=idle;

else

current_state<=next_state;

end

always @ (next_state or current_state or din or dout)

begin

case(current_state)

idle:

if(din)

next_state=st0;

else

next_state=idle;

st0:

if(din)

next_state=st1;

else

next_state=idle;

st1:

if(!din)

next_state=st2;

else

next_state=st1;

st2:

if(!din)

next_state=st3;

else

next_state=st0;

st3:

if(din)

next_state=st4;

else

next_state=idle;

st4:

if(din)

next_state=st5;

else

next_state=idle;

st5:

if(!din)

next_state=st6;

else

next_state=st1;

st6:

if(din)

next_state=st7;

else

next_state=idle;

st7:

if(din)

next_state=st1;

else

next_state=idle;

default:

next_state=idle;

endcase

end

always @ (posedge clk)

begin

if(next_state==st7)

dout<=1'd1;

else

dout<=1'd0;

end

endmodule

仿真結(jié)果:

|

|