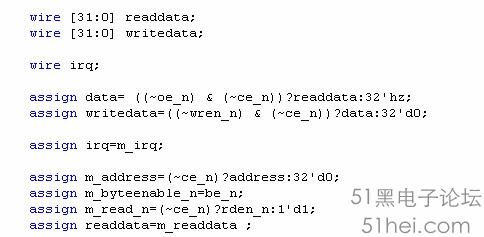

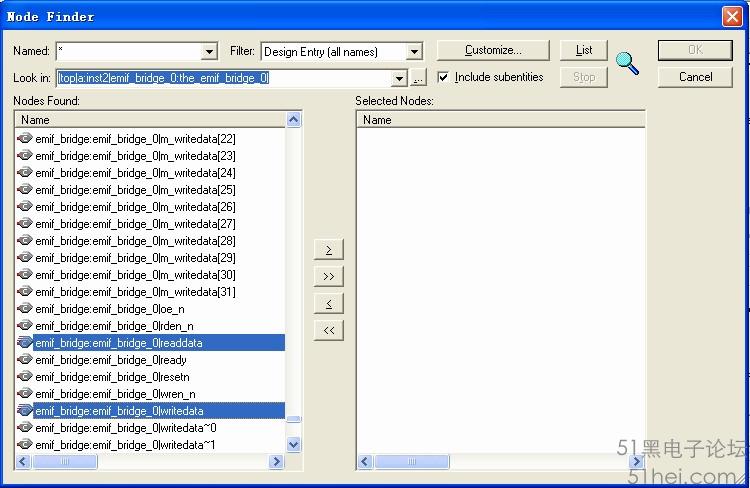

wire型數據 readdata和writedata,綜合以后不能添加到SignalTap中觀測。

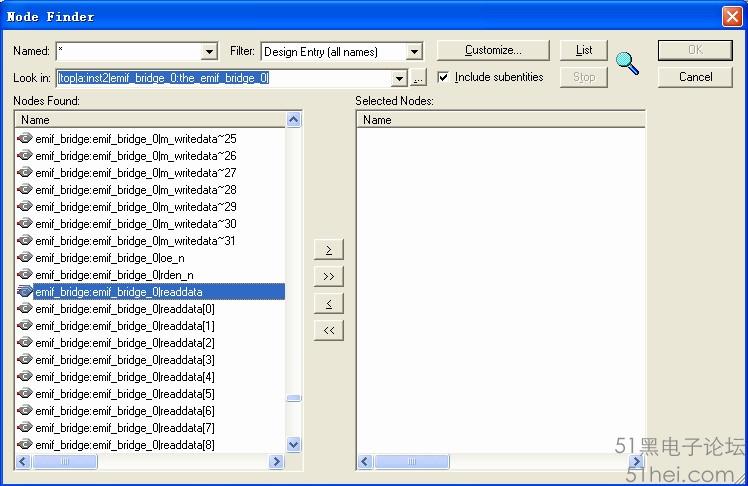

在待觀察的wire信號旁邊加上/*synthesis keep*/; wire [31:0] readdata /* synthesis keep = 1 */;

對于沒有output的reg信號,Quartus在綜合時也采用了最佳方式,因此,在SIgnalTap II中不能觀察該信號。 解決方法: 對于reg信號則加/*synthesis noprune*/ 或者 /* synthesis preserve */ 兩者的不同之處在于: /*synthesis noprune*/避免Quartus II優化掉沒output的reg。 /*synthesis preserve*/避免Quartus II將reg優化為常數,或者合并重復的reg。

若是想觀察整個模塊中的reg信號,則在module之后添加/*synthesis noprune*/ module test(clk,rst,data)/*synthesis noprune*/ ;

|