首先聲明:本文是在我的技術指導員的指導下由本人根據實踐摸索而得的經驗所原創,如有轉載請注明作者及出處。

-----(本文與新浪博客同步)

并且也敢大膽的說一句這也許是網絡上最完整的最清晰最詳細的在FPGA中嵌入51單片機內核的中文教程。不信你網上搜搜,反正當初我摸索的時候是每找到一篇具有實用價值的文章。我就非常不理解,這不是一項很少人掌握的技術,為什么就幾乎沒有人將此分享出來呢。

好了,廢話不多說了,上正文。此教程我使用的是oreganosystems提供的開源8051內核。Altera自帶的8051內核并不是免費的,我也曾跟altera的客服發郵件申請過8051內核(英文的郵件交流。。我也不太說),反正用郵件對話了幾次大致意思是他們不免費給,說網上有免費的51IP核可以自己去下載。可以自己去那個網上下載或者下載我上傳的

該源碼請:點擊下載(附件依附于21EDA論壇歡迎訪問)

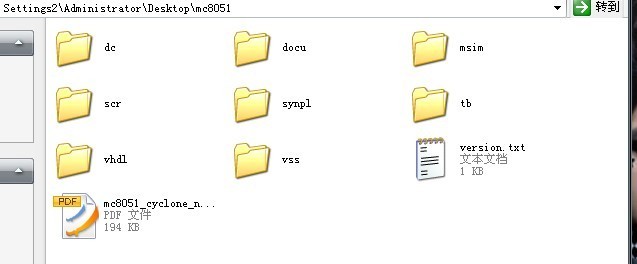

打開后的文件有上面這些文件夾。其中就一個最重要的就是8051核的源碼,全部放在vhdl這個文件夾里面。那個pdf文檔是這個IP核的使用教程,是官方標配的使用文檔,也是純英文的,對于英語四級沒過的我下定決心花了大力氣看最后只是一場空。。這問文檔寫的是用Synplify Pro這個綜合軟件綜合的,雖然據說用這個軟件進行綜合可以節約FPGA的很多邏輯單元,但是對于我們這些初學者來講,真的又麻煩又不適用,我們還是直接用QuartusII 來進行綜合好了。 51IP核的源碼全部在都在vhdl 這個文件夾中,打開是一大堆的源文件。

對于這么多的文件該怎么用,該如何使用,這是本文的重點。 首先用QuartusII建立一個工程,這這里先提醒下,文件目錄最好不要包含中文,空格,不然會有些無法理解的錯誤。 然后將 vhdl 整個文件夾復制到工程目錄下(個人習慣,等下添加進工程里面的時候方便點)。下面是添加8051核文件的步驟。

選擇文件添加進工程。這里注意下 后面拖著_cfg 的這種文件不要添加進工程里面,還有就是含有_top_的文件也不要添加到里面。 然后雙擊打開mc8051_p.vhd 這個文件。把下面這些模塊的例化語句全部刪掉,這點非常重要!! component mc8051_top port (clk : in std_logic; reset : in std_logic; int0_i : in std_logic_vector(C_IMPL_N_EXT-1 downto 0); int1_i : in std_logic_vector(C_IMPL_N_EXT-1 downto 0); all_t0_i : in std_logic_vector(C_IMPL_N_TMR-1 downto 0); all_t1_i : in std_logic_vector(C_IMPL_N_TMR-1 downto 0); all_rxd_i : in std_logic_vector(C_IMPL_N_SIU-1 downto 0); p0_i : in std_logic_vector(7 downto 0); p1_i : in std_logic_vector(7 downto 0); p2_i : in std_logic_vector(7 downto 0); p3_i : in std_logic_vector(7 downto 0); p0_o : out std_logic_vector(7 downto 0); p1_o : out std_logic_vector(7 downto 0); p2_o : out std_logic_vector(7 downto 0); p3_o : out std_logic_vector(7 downto 0); all_rxd_o : out std_logic_vector(C_IMPL_N_SIU-1 downto 0); all_txd_o : out std_logic_vector(C_IMPL_N_SIU-1 downto 0); all_rxdwr_o : out std_logic_vector(C_IMPL_N_SIU-1 downto 0));

end component;

----------------------------------------------------------------------------- -- START: Component declarations for simulation models ----------------------------------------------------------------------------- component mc8051_ram port (clk : in std_logic; reset : in std_logic; ram_data_i : in std_logic_vector(7 downto 0); ram_data_o : out std_logic_vector(7 downto 0); ram_adr_i : in std_logic_vector(6 downto 0); ram_wr_i : in std_logic; ram_en_i : in std_logic);

end component;

component mc8051_ramx port (clk : in std_logic; reset : in std_logic; ram_data_i : in std_logic_vector(7 downto 0); ram_data_o : out std_logic_vector(7 downto 0); ram_adr_i : in std_logic_vector(15 downto 0); ram_wr_i : in std_logic);

end component;

component mc8051_rom port (clk : in std_logic; reset : in std_logic; rom_data_o : out std_logic_vector(7 downto 0); rom_adr_i : in std_logic_vector(15 downto 0));

end component; ----------------------------------------------------------------------------- -- END: Component declarations for simulation models -----------------------------------------------------------------------------

然后雙擊打開mc8051_core.vhd 這個文件。

這樣就可以生成mc8051核的原理圖模塊了。

當然光有這個核,它還不是完整的51核,還需要給它添加ram和rom Ram是必須的,ramx是擴展的,rom也是必須的,是用來放所需運行的51單片機程序的,大小可以根據需要定制。但是推薦ram的大小用固定的以下配置。

三個存儲單元都有一點需要注意,就是不能寄存輸出。

就是在ram和rom配置的時候都要把 ‘q‘output port 前面的勾去掉!這點也很重要。 rom配置的時候需要加入.hex文件,就是keilc51 編譯好的平時下載到單片機實驗板上的那個程序文件,初始的時候可以隨便添加一個就可以了,待程序寫好后,就重新把它添加要rom里面,注意,如果改變了rom的程序文件,那么要重新完整編譯一次下載到板子上才是更新后的程序噢。

然后就按照固定的格式將他們連接起來就可以了。可以發現,有些線是斷開的通過標號來連接的,跟protel里的網絡標號差不多。一般的數據寬度不匹配的時候就用這種方式來連接,如果直接連接,編譯會報錯的。

這里面我添加了鎖相環,這個最好加上,因為我在測試的時候發現同樣的時鐘頻率下,加了鎖相環才能工作,不加就不工作。 Ok 編譯下載就成功了。不過從編譯報告來看,這個東西的確占邏輯單元比較多,我的板子是EP2C8Q208C8的芯片,用了一半的邏輯單元去。。。電腦CPU差,編譯時間又挺漫長的。。 嗯,總結一下嵌入51核要注意的點 1、添加文件進工程時,有些是必要的,有些是不能加的。 2、有個文件要進行一下修改 3、配置ram和rom的時候,不要寄存器輸出。 如有錯誤,歡迎指正。

|