|

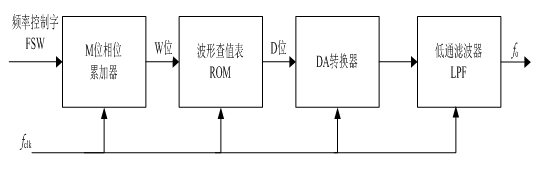

函數(shù)信號(hào)發(fā)生器設(shè)計(jì)報(bào)告 參賽學(xué)校:河池學(xué)院 參賽作者:梁平 摘要 本系統(tǒng)基于直接數(shù)字頻率合成(DDS)技術(shù),系統(tǒng)以Luminary Micro公司的Stellaris系列的ARM1138為控制核心平臺(tái),配合DAC電路,設(shè)計(jì)了完成了低頻三相函數(shù)信號(hào)發(fā)生器,頻率范圍100Hz~20KHz,頻率穩(wěn)定度優(yōu)于10-5-,最小步進(jìn)1Hz,頻率精度優(yōu)于0.1%。采用NE5532的功放電路使得10kΩ負(fù)載上的電壓峰-峰值Vopp≥10V。利用DDS原理同時(shí)產(chǎn)生FM調(diào)制波形及占空比可控、頻率可預(yù)置、步進(jìn)為1Hz的矩形波波形。通過(guò)把數(shù)據(jù)寫入24C04可以實(shí)現(xiàn)掉電保護(hù)功能。經(jīng)實(shí)際測(cè)測(cè)試完成了題目要求的全部功能和指標(biāo)。 一、系統(tǒng)方案 1.1比較與選擇 方案一:采用DDS專用芯片AD9850作為信號(hào)產(chǎn)生模塊,以單片機(jī)為系統(tǒng)的控制核心。該方案具有頻譜純度高、集成度高等特點(diǎn)。由于AD9850自帶32位相位累加的數(shù)控振蕩器,會(huì)產(chǎn)生低噪聲、高穩(wěn)定的頻率輸出波形。但它只直接提供了實(shí)現(xiàn)多種數(shù)字調(diào)制的功能,像二進(jìn)制PSK、二進(jìn)制FSK,這類調(diào)制方式實(shí)現(xiàn)起來(lái)比較簡(jiǎn)單,二要實(shí)現(xiàn)模擬線性調(diào)制FM具有一定的難度。故此方案也不采用。 方案二:采用基于FPGA的直接數(shù)字頻率合成,并以FPGA作為整個(gè)系統(tǒng)的信號(hào)產(chǎn)生和控制中心。基于FPGA的直接數(shù)字頻率合成其組成框圖如圖1-1。直接數(shù)字頻率合成(DDS),具有頻率切換速度快,頻率分辨率高、可編程全數(shù)字化、相位連續(xù)、轉(zhuǎn)換速度高、控制方便且有輸出任意波形的能力等優(yōu)點(diǎn)。用FPGA實(shí)現(xiàn)DDS技術(shù)比較靈活,可以產(chǎn)生多種調(diào)制方式,多種組合方式。采用此方案把重心放在了FPGA設(shè)計(jì)上,增加了FPGA部分程序的量,鑒于分工關(guān)系,放棄此方案。  圖1-1 基于FPGA的直接數(shù)字頻率合成 圖1-1 基于FPGA的直接數(shù)字頻率合成 方案三:采用基于DDS專用芯片AD9850作為信號(hào)產(chǎn)生模塊,并以基于ARM7的微控制器ARM1138作為整個(gè)系統(tǒng)的控制核心。在ARM1138中嵌入U(xiǎn)COSII操作系統(tǒng)方便實(shí)現(xiàn)多任務(wù)處理。例如波形轉(zhuǎn)換,頻率調(diào)節(jié),幅值調(diào)節(jié),12864顯示,I2C掉電保護(hù)等。本方案融合了如方案一頻率合成的優(yōu)點(diǎn),并能發(fā)揮ARM控制器強(qiáng)大的系統(tǒng)管理能力。同時(shí)可利于分工合作,以最快的時(shí)間完成題目的所有要求。此方案比較靈活、可擴(kuò)展性好,能完全達(dá)到設(shè)計(jì)要求,故采用此方案。

二、理論分析與說(shuō)明 2.1總體設(shè)計(jì)思路及說(shuō)明 ARM微控制器從鍵盤獲得控制信息,通過(guò)計(jì)算得到控制字并通過(guò)IO口送給DDS的頻率和相位的控制端口,同時(shí),將信息顯示在LCD上。DDS輸出信號(hào)由程序控制其預(yù)置頻率和相位的正弦信號(hào)或方波信號(hào),再通過(guò)放大倍數(shù)可調(diào)的運(yùn)算放大系統(tǒng)來(lái)控制調(diào)幅。三角波則由方波信號(hào)經(jīng)過(guò)一級(jí)方大后通過(guò)積分電路獲得。掉電保護(hù)功能則由ARM1138內(nèi)部AD把數(shù)據(jù)讀回再通過(guò)I2C寫入24C04來(lái)完成。結(jié)構(gòu)圖如圖2-1。

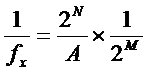

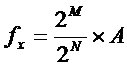

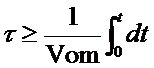

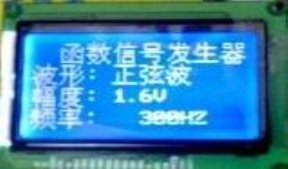

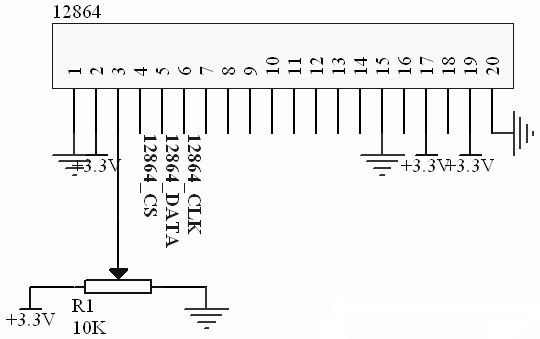

圖2-1 基于ARM1138的直接數(shù)字頻率合成 2.2DDS的實(shí)現(xiàn)設(shè)計(jì) DDS的基本原理是利用采樣定理,通過(guò)查表法產(chǎn)生波形,其基本架構(gòu)如圖2-2所示: 圖2-2 DDS原理框圖 相位累加器由N位加法器與N位累加寄存器級(jí)聯(lián)構(gòu)成。 每來(lái)一個(gè)時(shí)鐘脈沖fs,加法器將頻率控制字k與累加寄存器輸出的累加相位數(shù)據(jù)相加,把相加后的結(jié)果送至累加寄存器的數(shù)據(jù)輸入端。累加寄存器將加法器在上一個(gè)時(shí)鐘脈沖作用后所產(chǎn)生的新相位數(shù)據(jù)反饋到加法器的輸入端,以使加法器在下一個(gè)時(shí)鐘脈沖的作用下繼續(xù)與頻率控制字相加。這樣,相位累加器在時(shí)鐘作用下,不斷對(duì)頻率控制字進(jìn)行線性相位累加。 由此可以看出, 相位累加器在每一個(gè)時(shí)鐘脈沖輸入時(shí),把頻率控制字累加一次,相位累加器輸出的數(shù)據(jù)就是合成信號(hào)的相位,相位累加器的溢出頻率就是DDS輸出的信號(hào)頻率。 用相位累加器輸出的數(shù)據(jù)作為波形存儲(chǔ)器(ROM)的相位取樣地址,這樣就可把存儲(chǔ)在波形存儲(chǔ)器內(nèi)的波形抽樣值 (二進(jìn)制編碼) 經(jīng)查找表查出,完成相位到幅值轉(zhuǎn)換。波形存儲(chǔ)器的輸出送到D/A轉(zhuǎn)換器,D/A轉(zhuǎn)換器將數(shù)字量形式的波形幅值轉(zhuǎn)換成所要求合成頻率的模擬量形式信號(hào)。低通濾波器用于濾除不需要的取樣分量,以便輸出頻譜純凈的正弦波信號(hào)。 DDS在相對(duì)帶寬、頻率轉(zhuǎn)換時(shí)間、高分辨力、相位連續(xù)性、 正交輸出以及集成化等一系列性能指標(biāo)方面遠(yuǎn)遠(yuǎn)超過(guò)了傳統(tǒng)頻率合成技術(shù)所能達(dá)到的水平,為系統(tǒng)提供了優(yōu)于模擬信號(hào)源的性能。 DDS原理有以下特點(diǎn): (1)輸出頻率相對(duì)帶寬較寬 輸出頻率帶寬為50%fs(理論值)。但考慮到低通濾波器的特性和設(shè)計(jì)難度以及對(duì)輸出信號(hào)雜散的抑制, 實(shí)際的輸出頻率帶寬仍能達(dá)到40%fs。 (2)頻率轉(zhuǎn)換時(shí)間短 DDS是一個(gè)開(kāi)環(huán)系統(tǒng),無(wú)任何反饋環(huán)節(jié),這種結(jié)構(gòu)使得DDS的頻率轉(zhuǎn)換時(shí)間極短。事實(shí)上,在DDS的頻率控制字改變之后,需經(jīng)過(guò)一個(gè)時(shí)鐘周期之后按照新的相位增量累加,才能實(shí)現(xiàn)頻率的轉(zhuǎn)換。因此,頻率轉(zhuǎn)換的時(shí)間等于頻率控制字的傳輸時(shí)間,也就是一個(gè)時(shí)鐘周期的時(shí)間。時(shí)鐘頻率越高,轉(zhuǎn)換時(shí)間越短。DDS的頻率轉(zhuǎn)換時(shí)間可達(dá)納秒數(shù)量級(jí),比使用其它的頻率合成方法都要短數(shù)個(gè)數(shù)量級(jí)。 (3)頻率分辨率極高 若時(shí)鐘fs 的頻率不變,DDS的頻率分辨率就由相位累加器的位數(shù)N決定。 只要增加相位累加器的位數(shù)N即可獲得任意小的頻率分辨率。目前,大多數(shù)DDS的分辨率在1Hz數(shù)量級(jí),許多小于1mHz甚至更小。 (4)相位變化連續(xù) 改變DDS輸出頻率,實(shí)際上改變的每一個(gè)時(shí)鐘周期的相位增量,相位函數(shù)的曲線是連續(xù)的,只是在改變頻率的瞬間其頻率發(fā)生了突變,因而保持了信號(hào)相位的連續(xù)性。 (5)輸出波形的靈活性 只要在DDS內(nèi)部加上相應(yīng)控制如調(diào)頻控制FM、 調(diào)相控制PM和調(diào)幅控制AM,即可以方便靈活地實(shí)現(xiàn)調(diào)頻、調(diào)相和調(diào)幅功能,產(chǎn)生FSK、PSK、ASK和MSK等信號(hào)。另外,只要在DDS的波形存儲(chǔ)器存放不同波形數(shù)據(jù), 就可以實(shí)現(xiàn)各種波形輸出, 如三角波、鋸齒波和矩形波甚至是任意的波形。當(dāng)DDS的波形存儲(chǔ)器分別存放正弦和余弦函數(shù)表時(shí),既可得到正交的兩路輸出。 分析計(jì)算 假設(shè)時(shí)鐘為2MHz,數(shù)據(jù)保持寄存器選擇N Bit,在時(shí)鐘驅(qū)動(dòng)下,累加器輸出結(jié)果S被反饋到累加器輸入端B,B和A的數(shù)據(jù)被累加到S,下一個(gè)時(shí)鐘脈沖又將S反饋到B,再次與A累加到S,下一個(gè)時(shí)鐘脈沖又將S反饋到B,如此循環(huán)累加,實(shí)現(xiàn)按步進(jìn)值,按時(shí)鐘節(jié)拍循環(huán)累加,使得N Bit數(shù)據(jù)被徐循環(huán)累加,產(chǎn)生循環(huán)掃描的地址碼0~64(高6 Bit)。完成一次地址循環(huán)需要的時(shí)間由時(shí)鐘和步進(jìn)值決定,可以由公式計(jì)算: 一次地址循環(huán)可以輸出一個(gè)完整的波形,既T就是輸出波形的周期,轉(zhuǎn)換成頻率 ,得到計(jì)算公式: ,得到計(jì)算公式:  , ,  當(dāng)晶振(2M)和計(jì)數(shù)器Bit數(shù)N確定之后, 既與步進(jìn)值A(chǔ)成正比,對(duì)A的調(diào)整可以完成對(duì) 既與步進(jìn)值A(chǔ)成正比,對(duì)A的調(diào)整可以完成對(duì) 的設(shè)定,當(dāng)N足夠大時(shí),比例常數(shù) 的設(shè)定,當(dāng)N足夠大時(shí),比例常數(shù) 可以很小,例如0.01,既 可以很小,例如0.01,既 等于A的0.01倍,這樣就可以實(shí)現(xiàn)對(duì) 等于A的0.01倍,這樣就可以實(shí)現(xiàn)對(duì) 的精細(xì)調(diào)整,譬如0.01Hz。 的精細(xì)調(diào)整,譬如0.01Hz。 根據(jù)題目的基本要求,頻率范圍為100HZ~20KHZ。 根據(jù):輸出頻率: 最小頻率分辨率: 其中m為相位累加器的位數(shù),F(xiàn)TW為頻率控制字, 為時(shí)鐘頻率,輸出信號(hào)頻率主要取決于頻率控制字FTW.當(dāng)N增大時(shí), 為時(shí)鐘頻率,輸出信號(hào)頻率主要取決于頻率控制字FTW.當(dāng)N增大時(shí),  可以不斷增加, 可以不斷增加, 2.3正弦波產(chǎn)生模塊實(shí)現(xiàn)原理 由DDS原理,AD9850有40位控制字,32位用于頻率控制,5位用于相位控制。1位用于電源休眠(Power down)控制,2位用于選擇工作方式。這40位控制字可通過(guò)并行方式或串行方式輸入到AD9850,圖4是控制字并行輸入的控制時(shí)序圖,在并行裝入方式中,通過(guò)8位總線A0…D7將可數(shù)據(jù)輸入到寄存器,在重復(fù)5次之后再在FQ-UD上升沿把40位數(shù)據(jù)從輸入寄存器裝入到頻率/相位數(shù)據(jù)寄存器(更新DDS輸出頻率和相位),同時(shí)把地址指針復(fù)位到第一個(gè)輸入寄存器。接著在W-CLK的上升沿裝入8位數(shù)據(jù),并把指針指向下一個(gè)輸入寄存器,連續(xù)5個(gè)W-CLK上升沿后,W-CLK的邊沿就不再起作用,直到復(fù)位信號(hào)或FQ-UD上升沿把地址指針復(fù)位到第一個(gè)寄存器。在串行輸入方式,W-CLK上升沿把25引腳的一位數(shù)據(jù)串行移入,當(dāng)移動(dòng)40位后,用一個(gè)FQ-UD脈沖即可更新輸出頻率和相位。圖2-3是相應(yīng)的控制字串行輸入的控制時(shí)序圖。 圖2-3 DDS電路實(shí)現(xiàn)原理圖如圖2-4所示: 本次設(shè)計(jì)我們采用的是8位并行數(shù)據(jù)線控制,所用到的引腳功能如下: D0~D7:8 位數(shù)據(jù)輸入口,可給內(nèi)部寄存器裝入 40 位控制數(shù)據(jù)。 FQ-UD:頻率更新控制信號(hào),時(shí)鐘上。 W-CLK:字裝入信號(hào),上升沿有效。 RESET:復(fù)位端。低電平清除 DDS 累加器。 圖2-4 2.4方波模塊實(shí)現(xiàn)原理 AD9850可以產(chǎn)生一個(gè)頻譜純凈、頻率和相位都可編程控制且穩(wěn)定性很好的模擬正弦波,這個(gè)正弦波能夠直接作為基準(zhǔn)信號(hào)源,或通過(guò)其內(nèi)部高速比較器轉(zhuǎn)換成標(biāo)準(zhǔn)方波輸出,直接產(chǎn)生方波,這個(gè)是DDS合成的最大優(yōu)點(diǎn)。 2.5三角波模塊實(shí)現(xiàn)原理 由矩形波放大后經(jīng)積分電路轉(zhuǎn)換實(shí)現(xiàn)。由于積分電容的影響,輸出的三角波有失真,所以使用一個(gè)四位拔碼開(kāi)關(guān),選取不同的積分電容,選取不同的頻率范圍。 積分模塊原理:在本設(shè)計(jì)電路中,三角波是通過(guò)反向積分器對(duì)方波的積分產(chǎn)生。積分器的設(shè)計(jì)就是選擇集成運(yùn)算放大器和計(jì)算確定外電路的元件參數(shù)。應(yīng)注意到設(shè)計(jì)積分電路還應(yīng)考慮的問(wèn)題是怎樣減小積分漂移來(lái)減小積分誤差。 (1)集成運(yùn)放的選擇:在本設(shè)計(jì)中,集成運(yùn)放選用NE5532,因其有較小的輸入失調(diào)電壓和輸入失調(diào)電流,且開(kāi)環(huán)增益和帶寬足夠。 (2)電路元件參數(shù)的確定和電路原理圖如圖2-5所示: 、信號(hào)輸入端接入一耦合電容,大小為10uF; 、如圖(1)所示,左邊的NE5532為運(yùn)算放大電路,先將方波的V-PP放大到20V再進(jìn)行積分,放大倍數(shù)計(jì)算為A=R2/R1。R3為靜態(tài)平衡電阻,用以補(bǔ)償偏置電流所產(chǎn)生的失調(diào)。R4為積分漂移泄放電阻,用以防止積分漂移所造成的積分飽和或截止現(xiàn)象,但是,增加R4后,由于R4對(duì)電容的分流作用,會(huì)產(chǎn)生新的積分誤差,所以應(yīng)使R4>>RC,一般選擇R4=10R3。 、積分時(shí)間常數(shù)て的確定:積分設(shè)計(jì)常數(shù)て是決定積分器工作速度的主要參數(shù),て越小工作速度越高。但由于集成運(yùn)放的最大輸出電壓為有限值,是不允許將時(shí)間常數(shù)選得太小。如果集成運(yùn)放的最大輸出電壓為Vom,方波電壓幅值為E,則:て的值必須滿足 即  若て太大,積分器的輸出就小;て太小集成運(yùn)放的輸出就飽和。而且て的選擇與信號(hào)頻率有關(guān),頻率越低,時(shí)間常數(shù)就應(yīng)越大。 、積分電容的確定:て確定后,根據(jù)て=RC,則可得出積分電容的大小。一方面,增大輸入電阻R可以減小積分電容,但這又會(huì)加劇積分漂移;另一方面,積分電容越大漏電也會(huì)增大,使積分誤差增大。所以在選擇時(shí)應(yīng)對(duì)其進(jìn)行綜合考慮。 經(jīng)計(jì)算和實(shí)驗(yàn),本設(shè)計(jì)要求的頻率范圍從100Hz—20KHz的方波積分成三角波只需要一個(gè)105和一個(gè)273的兩種不同的瓷片電容即可達(dá)到。此裝置再換上不同的電容輸出的三角波頻率范圍可達(dá)10HZ到1MHZ。 圖2-5 2.6幅值調(diào)節(jié)模塊 由于AD9850輸出的正弦信號(hào)只有固定幅值,無(wú)法滿足幅值可調(diào) 因此利用可編程放大器實(shí)現(xiàn)幅值控制 因此利用可編程放大器實(shí)現(xiàn)幅值控制 但這種方法只能實(shí)現(xiàn)倍數(shù)調(diào)節(jié),而無(wú)法實(shí)現(xiàn)高精度連續(xù)調(diào)節(jié) 但這種方法只能實(shí)現(xiàn)倍數(shù)調(diào)節(jié),而無(wú)法實(shí)現(xiàn)高精度連續(xù)調(diào)節(jié) 本設(shè)計(jì)正弦幅值控制要求必須連續(xù)可調(diào),要高精度,X9511數(shù)字電位器的特點(diǎn)是只要按下向上按輸入(PU)和向下按輸入(PD)即可實(shí)現(xiàn)電阻可調(diào),其原理圖如2-6所示: 本設(shè)計(jì)正弦幅值控制要求必須連續(xù)可調(diào),要高精度,X9511數(shù)字電位器的特點(diǎn)是只要按下向上按輸入(PU)和向下按輸入(PD)即可實(shí)現(xiàn)電阻可調(diào),其原理圖如2-6所示: 圖2-6 因此,我們采用了數(shù)字電位器X9511,外加兩個(gè)按鍵進(jìn)行電阻的輸出可調(diào),改變放大器的反饋電阻,從而達(dá)到改變放大倍數(shù),即實(shí)現(xiàn)了幅值可調(diào)。其電路原理圖如圖2-7所示: 圖2-7 2.7顯示模塊設(shè)計(jì) 本次設(shè)計(jì)的顯示我們用的是12864液晶,12864液晶相對(duì)于1602液晶顯示的內(nèi)容要豐富得多,顯示的信息量大,切換全部用微動(dòng)開(kāi)關(guān)作按鍵來(lái)完成。液晶自帶字庫(kù),顯示漢字和符號(hào)方便。該液晶屏能顯示4行字符,每行顯示8個(gè)漢字或者16個(gè)英文字符,顯示的信息量已經(jīng)足夠。它的接口有20根線,有串行控制和并行控制兩種驅(qū)動(dòng)方式,在這里使用串行控制,以節(jié)省IO口,圖2-8為液晶接口電路。圖中的R1為液晶顯示對(duì)比度的調(diào)節(jié)電阻,典型值為10K,液晶選用3線串口驅(qū)動(dòng),這樣的好處是減少IO口的使用,這3跟線分別為時(shí)鐘線(12864_CLK)、片選線(12864_CS)、數(shù)據(jù)線(12864_DATA)。

本次我們用了5個(gè)按鍵控制,KEY1是選擇波形型號(hào),KEY2選擇頻率遞增,KEY3選擇頻率遞減,KEY4選擇幅值遞增,KEY5選擇幅值遞減。詳細(xì)見(jiàn)程序流程圖控制。

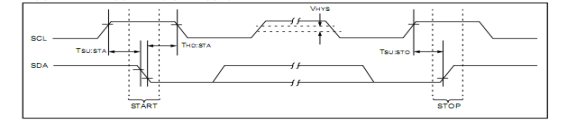

圖2-8 液晶接口電路 2.8 掉電保護(hù)I2C模塊設(shè)計(jì) 掉電保護(hù)我們采用的是24C02芯片,此芯片有2K的CMOS的E2PROM。24C02的 400KHz I2C 總線協(xié)議兼容 1.8 到 6.0 伏工作電壓范圍低功耗 CMOS技術(shù)寫保護(hù)功能,當(dāng) WP 為高電平時(shí)進(jìn)入寫保護(hù)狀態(tài),可以定時(shí)編程擦寫1,000,000 可保存數(shù)據(jù)可保存100年。24C02的時(shí)序如圖2-9所示:

三、程序設(shè)計(jì)圖2-9 本次軟件設(shè)計(jì)流程如圖3-1所示:程序初始化后進(jìn)入初始界面,再判斷KEY1是否被按下,按下KEY1是選擇波形型號(hào),按下KEY2選擇頻率遞增,按下KEY3選擇頻率遞減,按下KEY4選擇幅值遞增,按下KEY5選擇幅值遞減。本設(shè)計(jì)最大的優(yōu)點(diǎn)就是能實(shí)現(xiàn)掉電保護(hù),實(shí)時(shí)保存數(shù)據(jù),防止電壓過(guò)低或者突然斷電造成的數(shù)據(jù)丟失。 圖3-1 四、系統(tǒng)測(cè)試 4.1測(cè)試條件 表1 儀器儀表

4.2測(cè)試方案與測(cè)試結(jié)果 4.2.1觀察示波器,記錄頻率值和輸出電壓峰-峰值。 表二 頻率值和輸出電壓峰-峰值測(cè)量記錄表

4.2.2 觀察示波器,記錄步進(jìn)頻率值。 表三 步進(jìn)頻率值記錄表

4.3測(cè)試結(jié)果分析 由實(shí)驗(yàn)調(diào)試結(jié)果及測(cè)試結(jié)果,該函數(shù)信號(hào)發(fā)生器達(dá)到了題目的所有指示要求,在選擇波形與調(diào)節(jié)幅度頻率試時(shí)采用LCD人機(jī)交互界面,界面友好方便,具有直觀性。 五、結(jié)語(yǔ) 本次設(shè)計(jì)的低頻三相信號(hào)源,主要運(yùn)用了DDS基本原理,利用ARM1138作為仿真測(cè)試和實(shí)際測(cè)量(測(cè)量結(jié)果見(jiàn)上表)符合題目給定的基本要求。 六、參考文獻(xiàn) [1].謝自美,電子線路設(shè)計(jì)、試驗(yàn)、測(cè)試,武漢:華中科技大學(xué)出版社,2002年,第二版; [2].黃志偉,全國(guó)大學(xué)生電子設(shè)計(jì)競(jìng)賽訓(xùn)練教程,北京:電子工業(yè)出版社,200年 [3].康華光,電子技術(shù)基礎(chǔ).模擬部分,北京:高等教育出版社,1999年,第四版 附錄 1.程序壓縮包 2.附圖

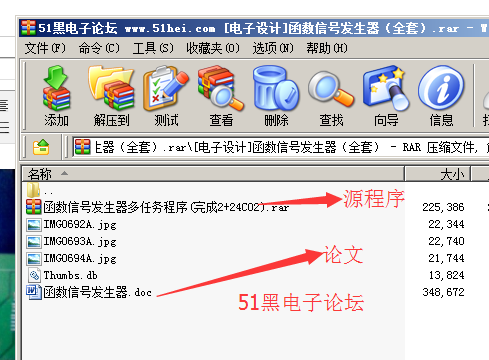

全部資料下載地址:

http://www.zg4o1577.cn/bbs/dpj-93416-1.html

|