通過QT 實現將數據傳輸至ARM FSMC至FPGA

附件包含源碼,原理圖等

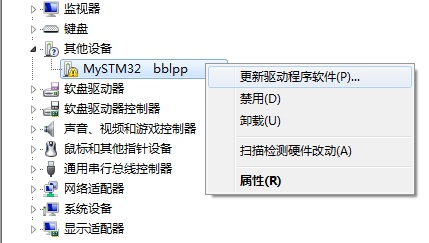

一、 驅動安裝:

圖1:更新驅動軟件(路徑:???)

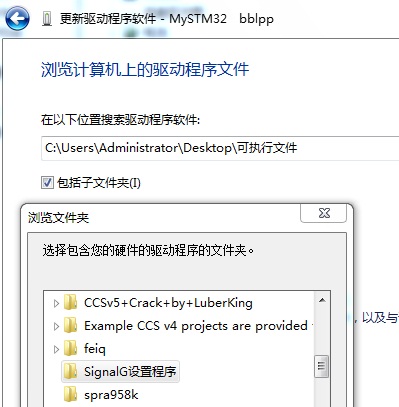

圖2:將程序更新到指定文件夾(建議:???)

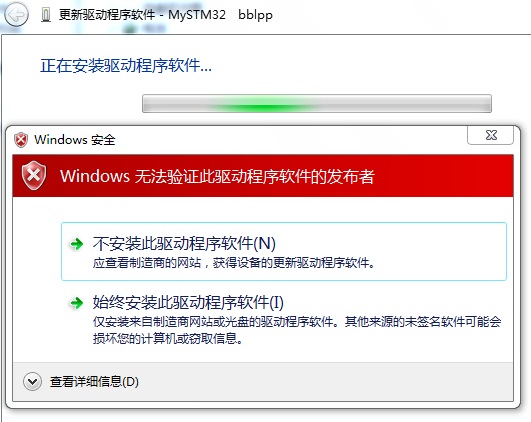

圖3:選擇始終安裝此驅動程序

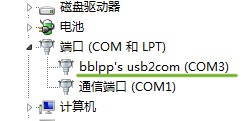

圖4:安裝后 多出的虛擬COM即為通訊接口。

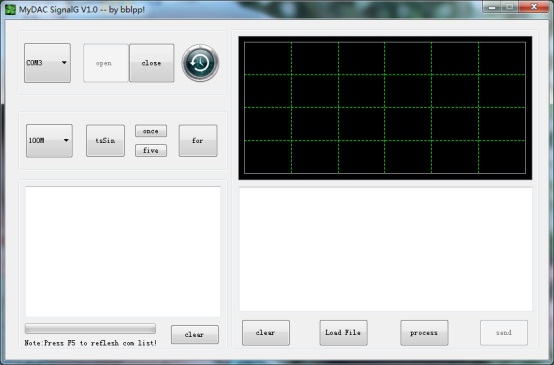

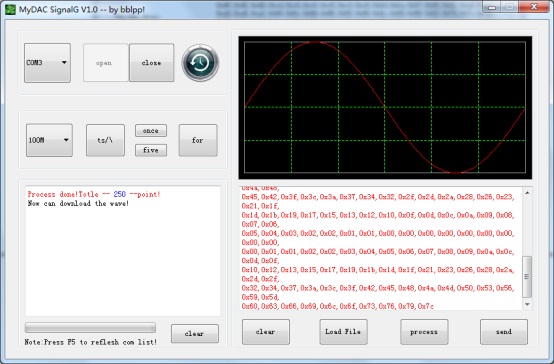

二、 設置 2.1程序啟動 將板卡通過USB連接后,打開SignalG_set.exe軟件,選擇剛剛安裝驅動后呈現的串口如COM3,然后點擊OPEN打開該串口。

圖5:進入軟件界面 注: 1)如果先打開的軟件再連接板卡,則可通過按下鍵盤F5鍵刷新串口選擇列表。 2)各按鍵定義說明: 100M選擇按鈕是用來選擇FPGA輸出時鐘,最高100M。 tsSin是內置的測試信號,分別可選擇輸出正炫波、方波、三角波、調幅波等。 Once/five:是設置只輸出一次或者連續輸出5次。該輸出次數可設置為0~255   圖6:示波器波形輸出 For:設置連續輸出。如果想要停止可按下once。 Clear按鍵是清楚信息窗口內容。

2.2測試輸出

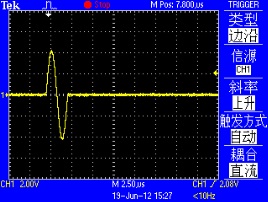

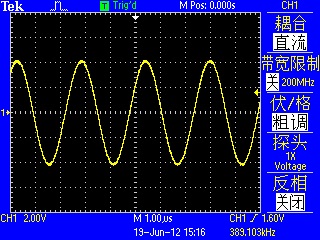

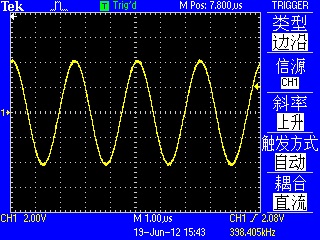

圖7:波形輸出 點擊TSSIN按鈕后,右側上面窗口會顯示輸出的波形 示波器中的圖如下:

圖8:波形輸出

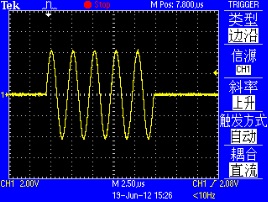

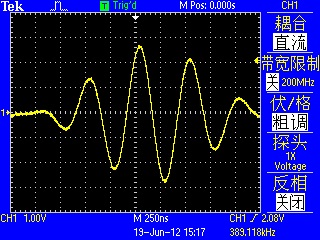

圖9:波形輸出 圖9:波形輸出

測試條幅信號輸出,波形如下:

圖10:波形輸出

2.3右側窗口功能

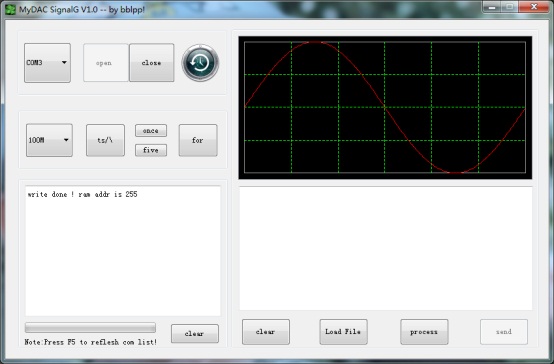

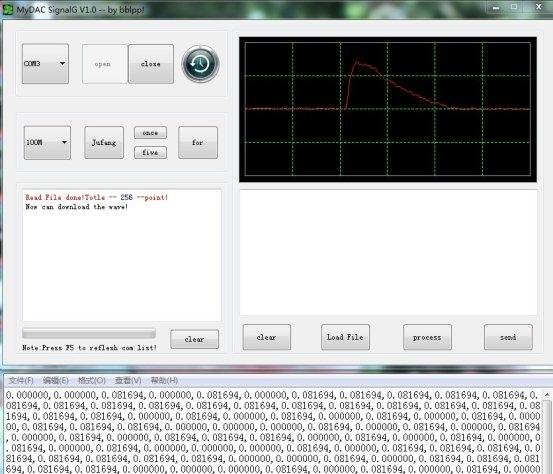

LoadFile 按鈕支持從文件中讀取,將讀取到的數據解析后畫到上面的圖中,這時點擊Send即可設置至板卡中。

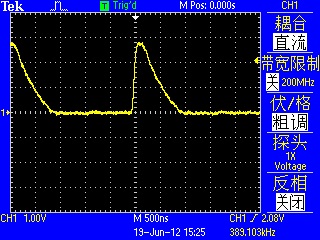

圖11:板卡寫入 注:文件中存儲的數據均為浮點型數據,以‘,’逗號隔開。解析成功后左側信息欄中會提示信息。 示波器中的圖像:

圖12:示波器波形顯示 2.4右下側窗口功能 右下側窗口是方便直接輸入解析后數據的,板上使用的DAC是8位DAC,那么它輸出的最小值是0x00,最大值是0xff,為了獲取最大值和最小值之間的數據,我們可以通過直接輸入原始的十六進制的數據來獲得。也可以通過Freq_calc.exe來獲得。

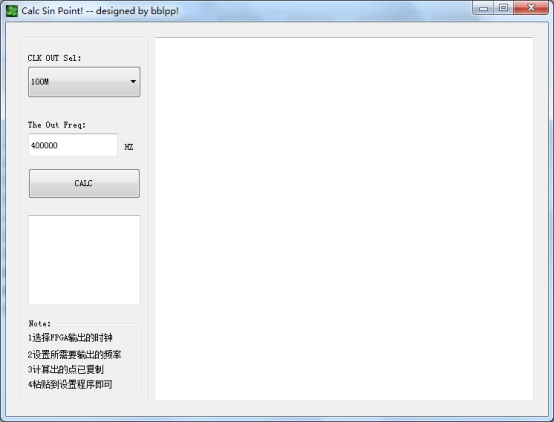

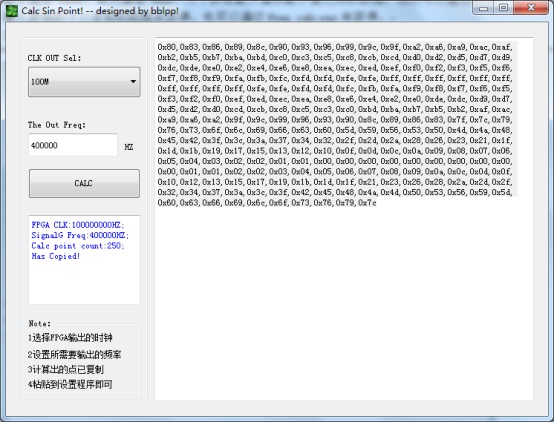

圖12:打開Freq_calc.exe軟件 我們可以選擇FPGA的輸出時鐘,默認為100M。然后設置輸出的頻率,(僅限正炫波)如400KHz,點擊CALC即可,數據已默認復制到剪貼板中。

圖13:時鐘輸出

圖14:時鐘輸出 在Signal_set.exe右下窗口點右鍵選擇粘貼Paste,然后點擊Process處理,即可將這些點處理成需要的格式,左側窗口會給出提示信息,并且會將處理后的波形刷到左上側的窗口中。

圖15:示波器波形顯示

附硬件設計: 圖一 正面 圖二 反面 系統設計原理圖: 如上圖,硬件設計主要參考小馬哥的“IBOARD電子學堂”,上位機將需要輸出的波形進行編碼,通過USB將波形數據傳給STM32,STM32通過FSMC接口將波形刷給FPGA,FPGA在時鐘的節拍下控制DAC輸出轉換。具體資源請參考相關芯片。

|