背景:Quartus II 13.0sp1(64-bit)、Modelsim SE-64 10.1c、DE2-70

目的:今天我們通過一個實驗來認識和初步使用鎖相環模塊ALTPLL,實驗的內容是將輸入的50Mhz的時鐘信號經過鎖相環模塊ALTPLL,輸出一路25MHz的分頻信號、一路100MHz的倍頻信號和一路有3ns相移的50Mhz的時鐘信號。 說明:我們有三種方式可以驗證實驗的正確性,一種方法是通過DE2-70開發板,將三路輸出信號映射到FPGA的引腳,通過示波器觀察,驗證結果;另外一種方法是利用SignalTapII Logical Analyzer進行驗證;第三種方法是編寫激勵塊,在軟件QuartusII中調用Modelsim SE進行仿真驗證實驗的正確性。本實驗會給出激勵塊,在仿真環境ModelsimSE中驗證實驗結果。 前兩種方式基于FPGA硬件設備,第三種方式可以在無硬件的條件下驗證實驗的正確性!! 1、配置鎖相環模塊ALTPLL: 1) 打開QuartusII軟件,選擇菜單欄Tool-->Mega Wizard Plug-In Manager,選擇Create a newcustom megafunction,意為創建一個新的宏功能模塊,然后單擊Next;  2) 在彈出的界面中,右上角選擇器件系列和輸出文件類型(此處選擇CycloneII和Verilog),在左邊框欄中選擇IO文件夾下的ALTPLL,最后選擇輸出文件保存路徑和文件名,按如圖所示設置后,點擊Next;  3) 在新彈出的界面中,設置輸入時鐘inclk0的頻率為50MHz(因為DE2-70開發板的輸入時鐘為50Mhz),設置devicespeed grade為6,這個參數與具體芯片的型號有關,其他保持默認,然后點擊Next;  4)設置輸入輸出信號。在彈出的界面中,按照如圖所示設置,其中OptionalInput項目下面包含”pllena(使能端,高電平有效)”、”areset(異步清零端,高電平有效)”、”pfdena(相位/頻率檢測器的使能端,高電平有效)”,為了方便操作,我們只選擇了areset異步清零端;同時LockOutput項目下,選擇”locked”,通過這個輸出端口可以判斷鎖相環是否失鎖,高電平表示正常;

5)單擊Next兩次,在彈出的界面中設置三個輸出信號c0、c1、c2的參數(頻率、相位和占空比)。設置輸出信號c0的頻率為25MHz,相移為零,占空比為50%,c1的頻率為50MHz,相移為4ns,占空比為50%,c2的頻率為100MHz,相移為零,占空比為50%,按照如圖進行設置: 說明:可以通過分頻因子和倍頻因子設置輸出信號頻率,也可以直接輸入輸入信號頻率,具體使用哪種方法,根據個人愛好!

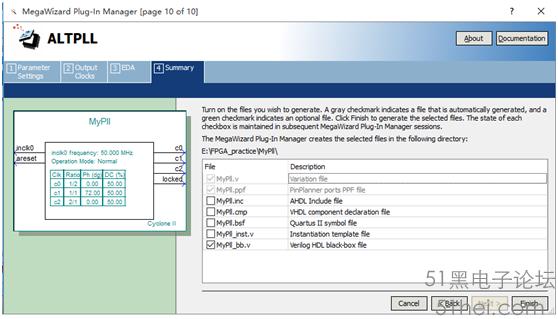

需要選中Use thisclock,圖片中忘記標記!!  6)設置輸出文件類型。設置完c0、c1、c2輸出信號的頻率、相位和占空比等參數后,點擊兩次Next,在新彈出的界面中選擇需要的輸出文件格式。 說明:MyPll.v文件是我們建立的實例模塊,需要在頂層模塊中調用,所以系統默認選中; MyPll_inst.v文件展示了在頂層模塊中引用的方法; MyPll.bsf文件與原理圖有關; 每個人可以根據自己的需要選擇文件,一般情況下保持默認即可!!

7)點擊Finish,配置完畢。 2、新建頂層文件,引用剛才生成的MyPll.v文件,同時編寫激勵塊文件,進行相關設置。 說明:關于如何建立工程、生成激勵塊文件,可以參考我的另一篇博文! 1)新建工程,并編寫頂層模塊,命名為My_Pll_Top.v具體代碼如下所示: moduleMy_Pll_Top(areset,inclock0,c0,c1,c2,locked); inputareset,inclock0; outputc0,c1,c2,locked; MyPll MyPll_inst( .areset(areset), .inclk0(inclock0), .c0(c0), .c1(c1), .c2(c2), .locked(locked)); endmodule 2)編寫激勵塊文件,具體代碼如下: `timescale 1 ns/ 1 ps moduleMy_Pll_Top_vlg_tst(); regareset; reginclock0; wirec0; wirec1; wirec2; wirelocked; My_Pll_Top i1( .areset(areset), .c0(c0), .c1(c1), .c2(c2), .inclock0(inclock0), .locked(locked) ); initial begin areset =1'b1; # 100 areset = 0; # 1000$stop; $display("Runningtestbench"); end always begin inclock0 = 1'b0; inclock0 = #10 1'b1; #10; end endmodule 2)將之前生成的MyPll.v文件加入到當前項目,然后對整個工程進行編譯,直到編譯通過。 3、進行仿真測試,驗證實驗結果。 1)首先在QuartusII中對仿真環境進行設置(具體設置可以參考里一片博文); 2)選擇菜單欄Tools-->Run Simulation Tool-->RTLSimulation,等待一會,系統會自動打開Modelsim SE仿真環境。 3)實驗結果如圖所示,通過各個信號的波形,可以觀察到輸入信號inclock0和輸出信號c0、c1、c2之間的關系: a、100ns之后,areset變為低電平,大約90ns之后,輸出信號正常; b、輸入信號inclock0的頻率為50Mhz, 輸出信號c0的頻率為25Mhz,c1的頻率為50Mhz,c2的頻率為100MHz; c、輸入信號inclock0和c0、c2同相位,同占空比,輸出信號c1相位滯后3ns; d、通過分析信號波形,得出實驗結果和理論一致。

|